无线工程师经常希望使用无线信号实现从概念到原型。诸如USRP(通用软件无线电外设)设备的软件无线电(SDR)提供了满足该需求的灵活解决方案。由于当今的应用需要更高的带宽和更短的延迟,因此需要在SDR的FPGA上实现更多的信号处理。但编程FPGA的无线工程师经常面临下列挑战:

1 FPGA与输入/输出(如RF信号或主机CPU)之间的接口困难

2 不熟悉用于算法实现的编程样式,及

3 编译时间长

在本系列适用于无线工程师的FPGA原型设计中,了解LabVIEW Communications System Design Suite (LabVIEW Communications)和NI SDR硬件如何帮助您克服关键性挑战,并快速创建无需FPGA知识的实时、无线测试平台。

第1部分. 立即连接FPGA算法至I/O

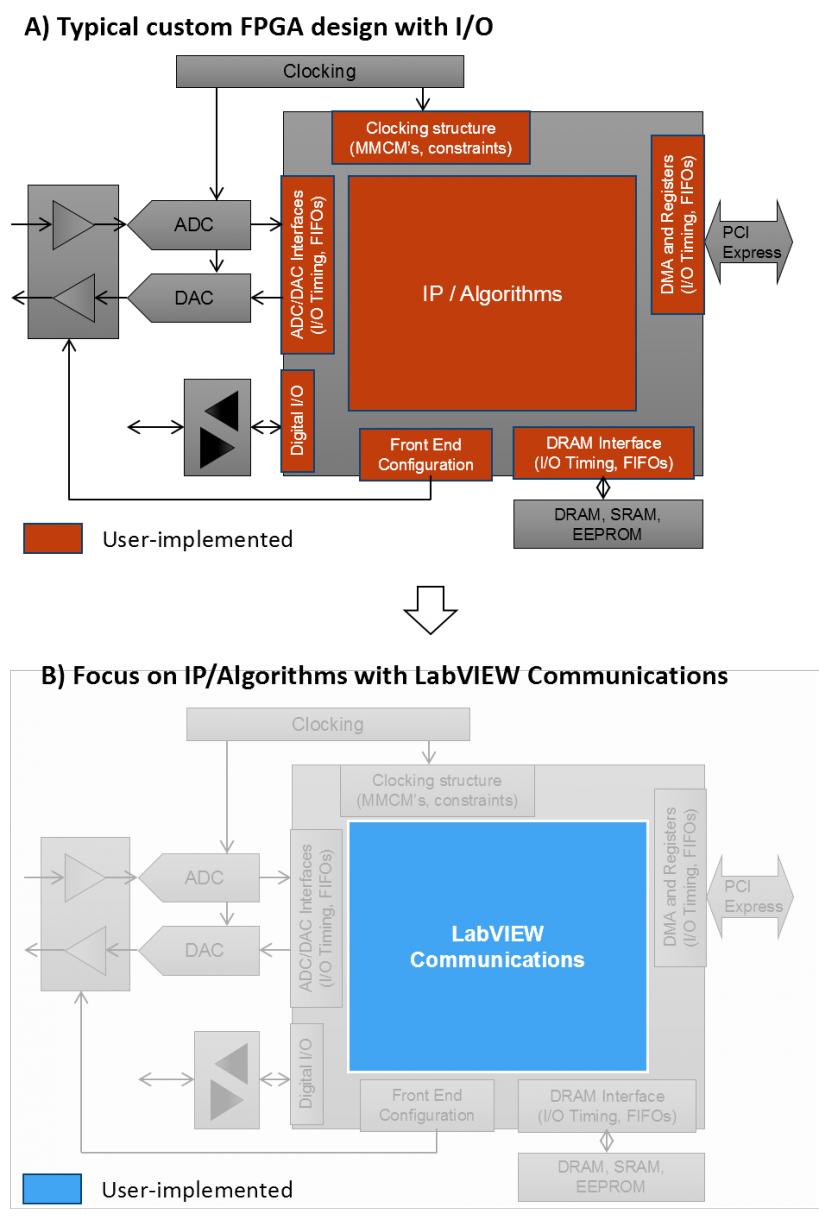

FPGA设计通常需要多个VHDL代码组件以用于模数转换器(ADC)、数模转换器(DAC)、PCI Express总线、存储器、时钟等接口(图1A)。其中的每一部分通常来自于:从零开发、重用现有的设计或从Xilinx或其他IP供应商处获得的IP。这意味着必须完成重要的集成工作以连接上述各部分,该集成工作通常比算法实现本身工作量更大。

尽管这些硬件接口实现起来很难,但定制它们的意义不大。例如,通过ADC接口关闭静态定时和计算同步可能较难实现,但它在不同项目中的模数转换功能基本相同。为了消除此瓶颈,LabVIEW Communications提供了SDR印刷电路板上所有硬件的接口。例如,ADC数据作为已被正确采样且已转换为正确的数据类型的采样提供给FPGA程序框图,用户仅需在程序框图上放置读取I/O节点即可访问这些数据。同样,如要将数据以数据流方式从FPGA传输至CPU,仅需使用写入FIFO节点而无需考虑实际的数据流实现方式。

在无线工程师适用的FPGA原型的第一部分,我们将介绍如何利用LabVIEW Communications快速在FPGA上传输数据,即让用户专注于算法的实现。

图1.(A)在带有I/O的典型自定义FPGA设计中,设计团队通常在集成I/O接口上花费的时间要高于实现算法或IP。(B)在LabVIEW Communications中已经实现了这些接口,因此设计团队可以专注于实现信号处理而不是系统集成。

第1步. 放置I/O节点

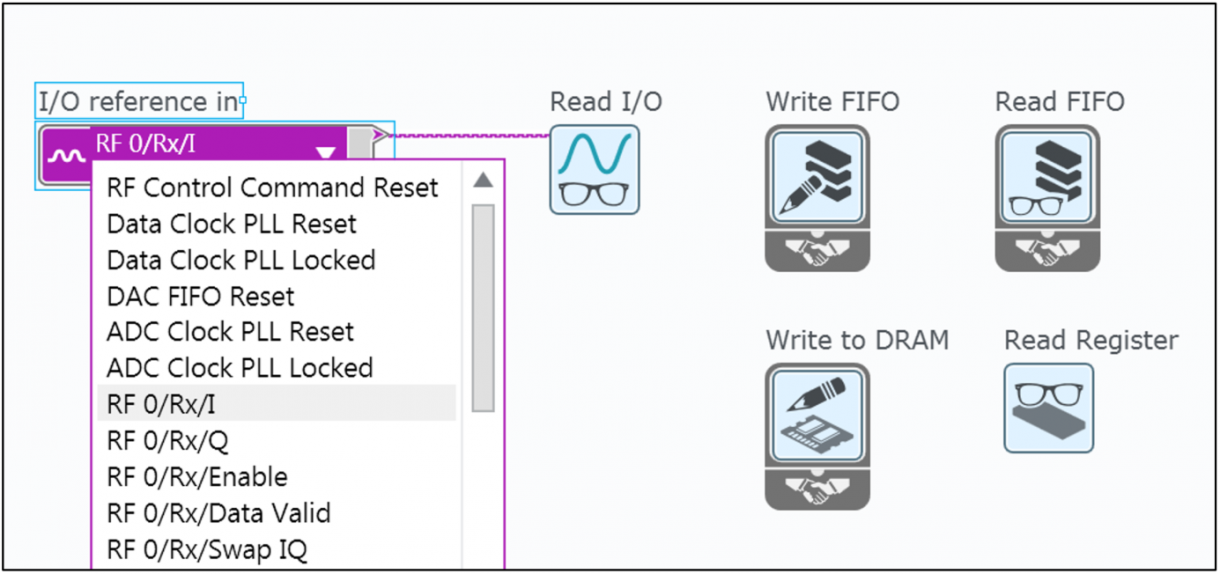

如要将FPGA算法与连接到RF前端的ADC和DAC、主机CPU或内存等资源建立连接,仅需为该资源放置一个读取或写入节点。关于节点的范例见图2。

图2.使用这些块与实际I/O及与主机CPU、USRP RIO设备上的DRAM或寄存器交互数据的FIFO通信。

第2步. 配置I/O节点

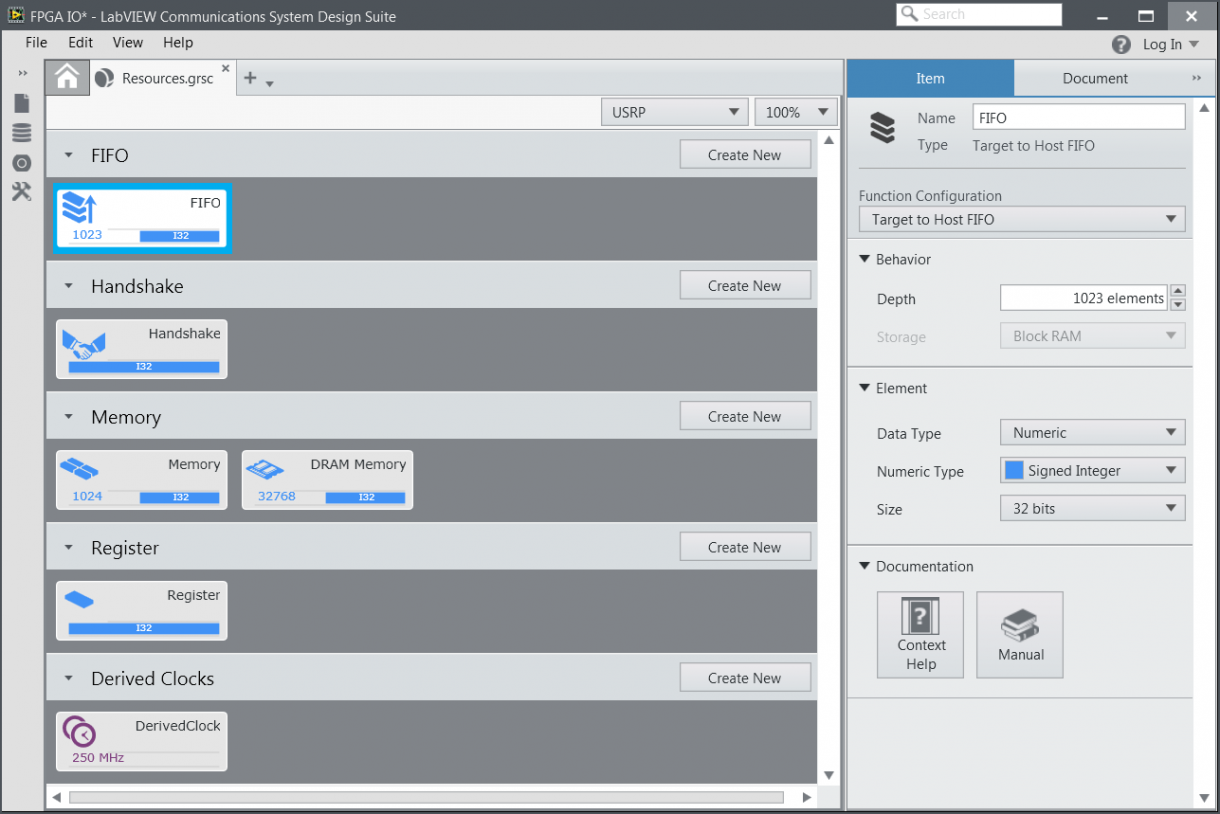

可使用资源文件配置FPGA I/O资源,如图3所示。配置资源别名、数据类型、方向(FPGA到主机、主机到FPGA、FPGA到FPGA、本地)或缓冲深度等属性。

图3.使用资源文件来创建和配置FIFO、内存、时钟和其他资源。

第3步. 连接算法至I/O节点

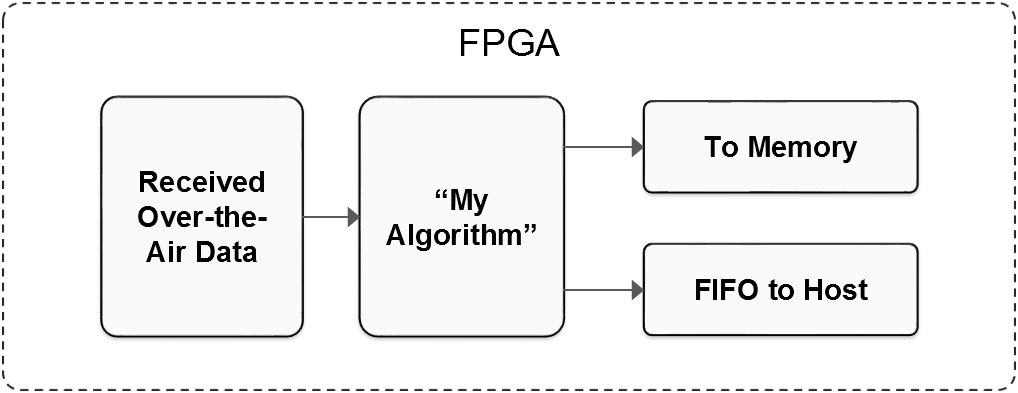

创建并配置了所需的资源后,就可以将它们连接至在FPGA上实现的算法。例如,图4框图是在LabVIEW Communications中的FPGA上实现的(见图5)。在该设计中,来自USRP RIO设备接收端口的数据以数据流方式传递至FPGA上的“My Algorithm”,这与同步、解调或滤波块类似。然后,该输出以数据流方式传输至内存和FPGA至CPU FIFO。

图4.该范例设计的框图显示了如何从RF前端接收数据,然后经由名为“My Algorithm”的用户创建块处理,最后以数据流方式传输至内存和主机CPU。“My Algorithm”可以是任意算法(如解调、滤波或快速傅里叶变换)。

图5.在LabVIEW Communications中FPGA代码的理论程序框图的实现中,从RF前端读取原始I和Q数据,然后经由“My Algorithm”处理,最后以数据流方式传输至内存和主机CPU。

第4步. 下一步

如要在FPGA上编写类似“My Algorithm”这样的自定义实时块,使用LabVIEW Communications免除了具备VHDL经验的要求。如要了解如何创建类似20 MHz正交频分复用(OFDM)调制器的算法,请继续阅读本技巧和窍门系列的下一部分:在不具备HDL专门知识的情况下从概念到FPGA代码。

文章转载自:NI官网