作者:默宸,来源:FPGA技术联盟

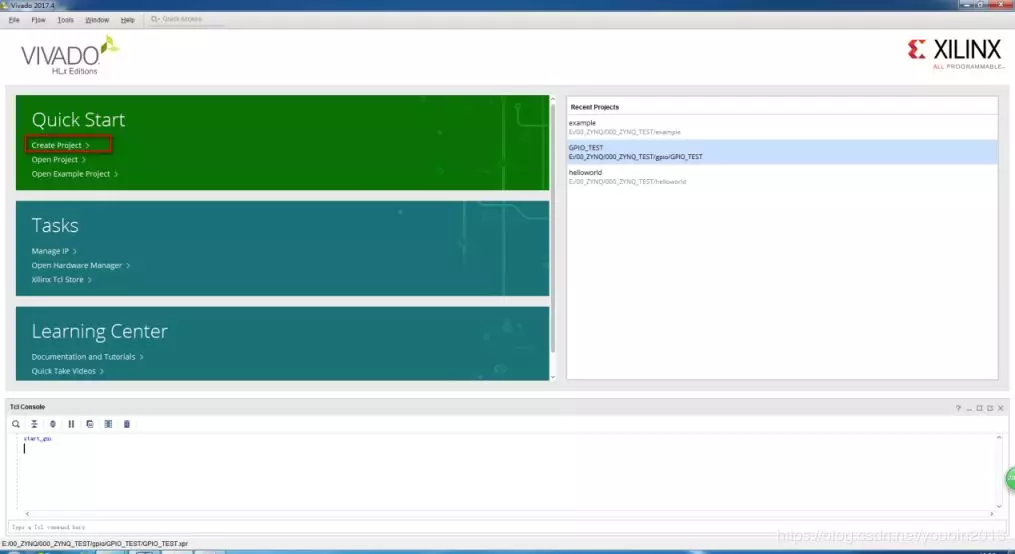

新建工程

1. 打开vivado2017.4,在出现的对话框中选择创建一个工程,如图所示。这一步是为了创建一个ZYNQ的工程。

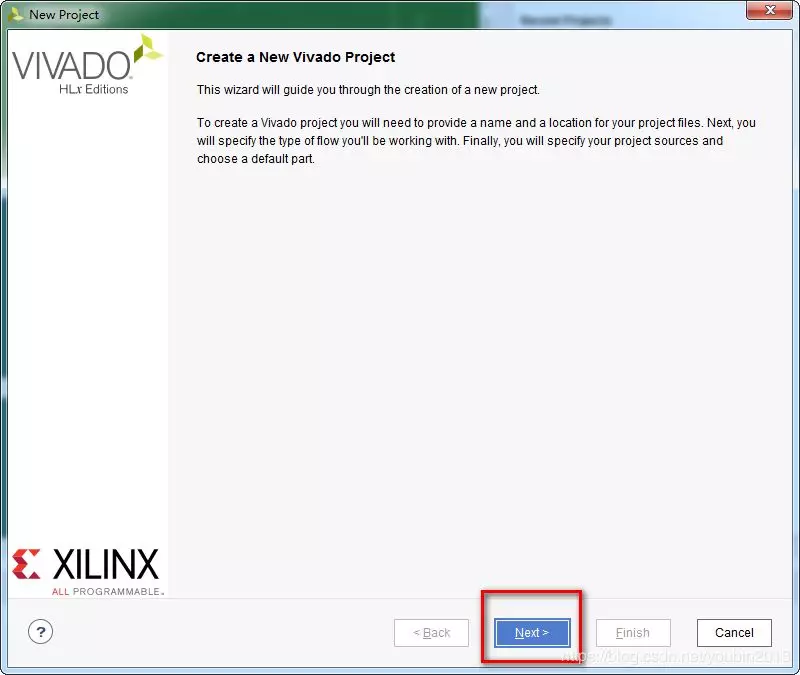

2. 点击创建工程后,出现对话框如图所示,然后点击对话框中的下一步。这一步表示这是一个创建工程的向导,通过该向导去新建一个工程。

3,此时会出现一个对话框如图所示,这一步给工程命名,并且确定工程的保存路径,下面的小勾表示创建一个和工程名字相同子目录,然后点击下一步。

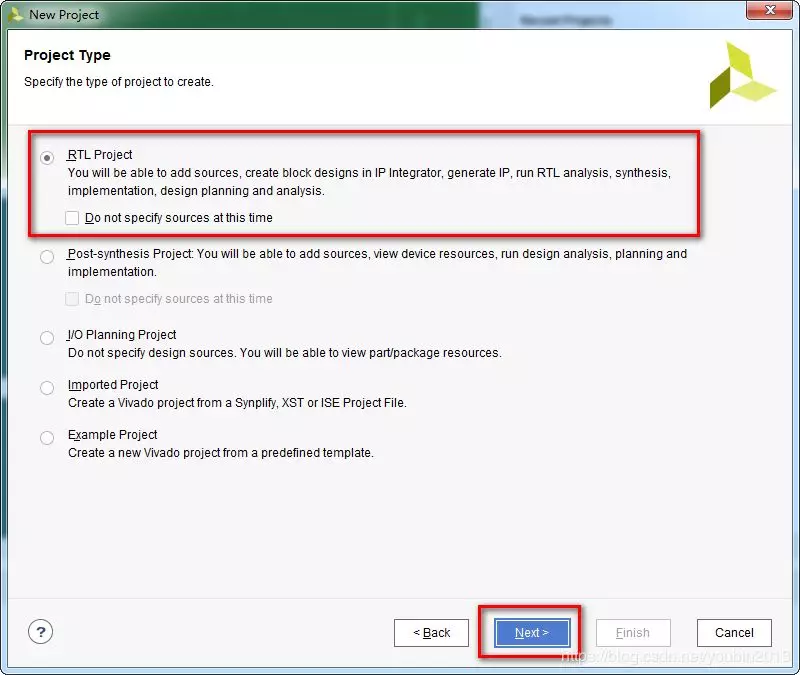

4,下一步后出现对话框如图所示,该步骤是确定需要创建工程的类型,我们选择RTL工程,该类型的工程可以添加源文件,创建IP大框架,生成IP,综合分析和实现等。点击下一步。

5,此时出现对话框如图所示,该步骤表示添加现有的源文件,创建一个空的工程,这步直接点击下一步。

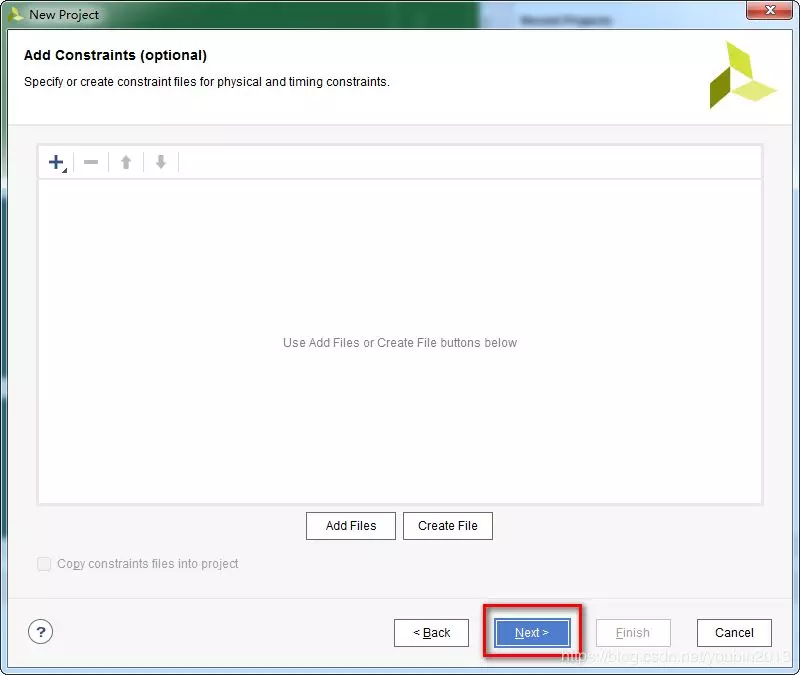

6,出现对话框如图所示,该步骤为添加现有的约束文件,创建空的工程,直接点击下一步。

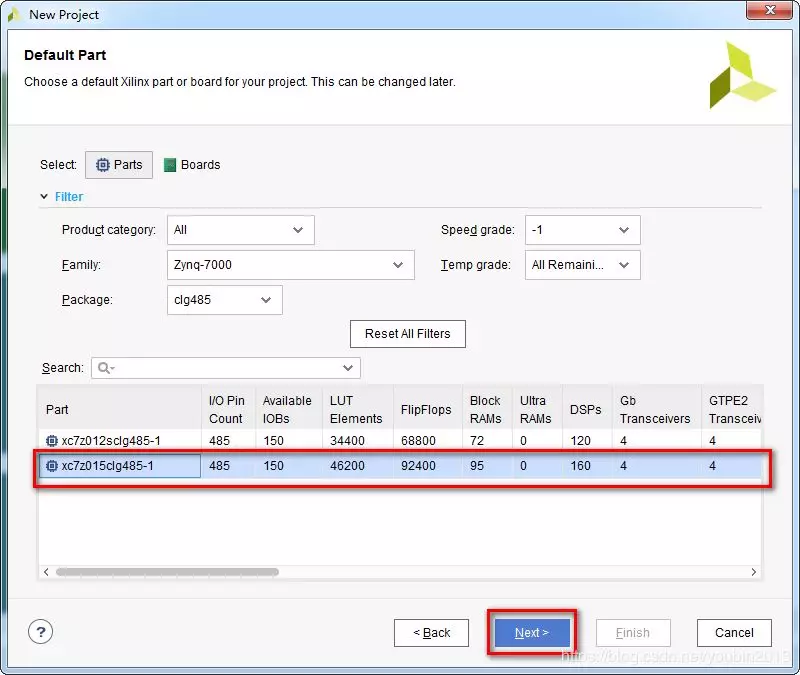

7,出现对话框如图所示,该步骤选择芯片的类型,本工程建立在7015型号上,所以选择xc7z015clg485-1,然后点击下一步。

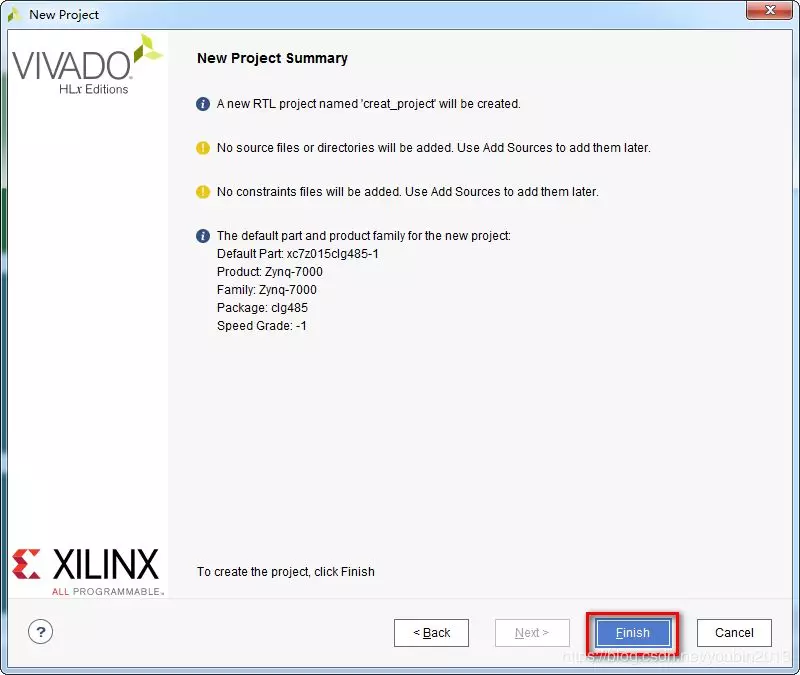

8,此时出现对话框如图所示,该步骤表示工程创建完成,显示所创建的工程的信息,点击完成。

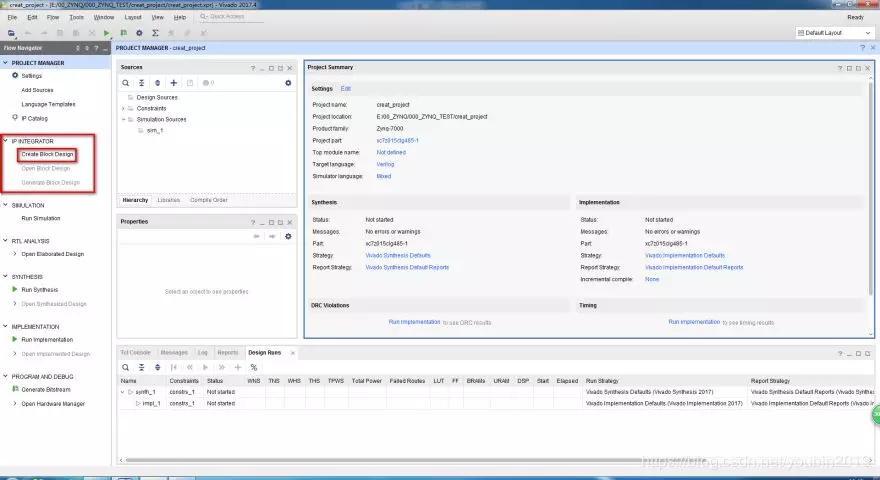

9,空的工程创建完成以后出现界面如图所示,需要往里面添加需要的IP大框架,在IP向导下拉表中双击创建IP框架,建立IP框架图。

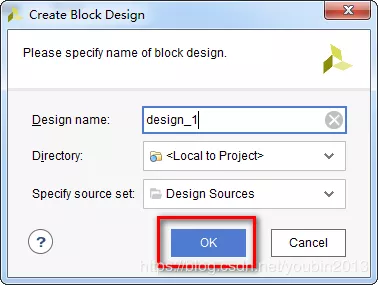

10,双击后出现创建设计对话框如图所示,点击OK。

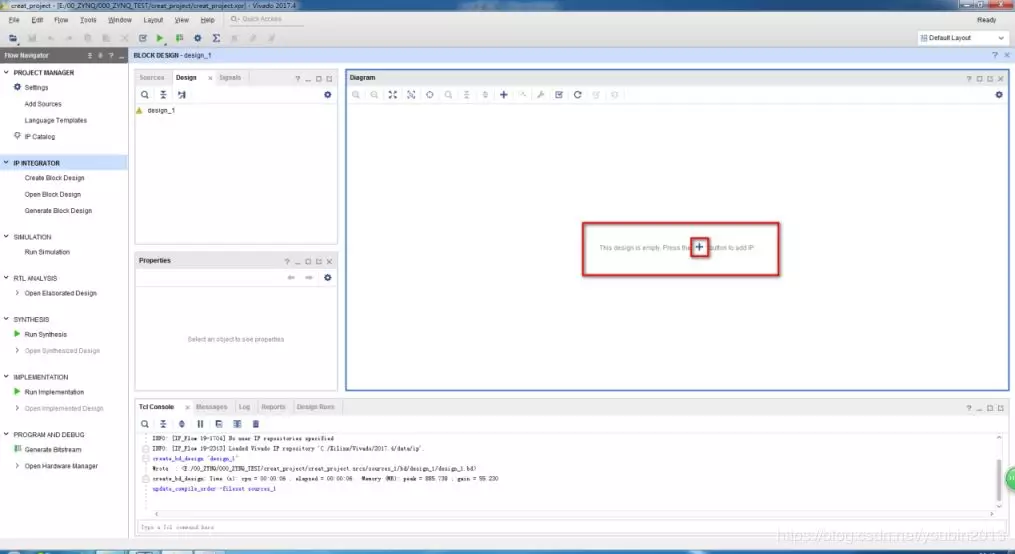

11,创建背框后出现如图的对话框,点击diagram中的大空白页中的“+”图标,添加IP到设计框架。

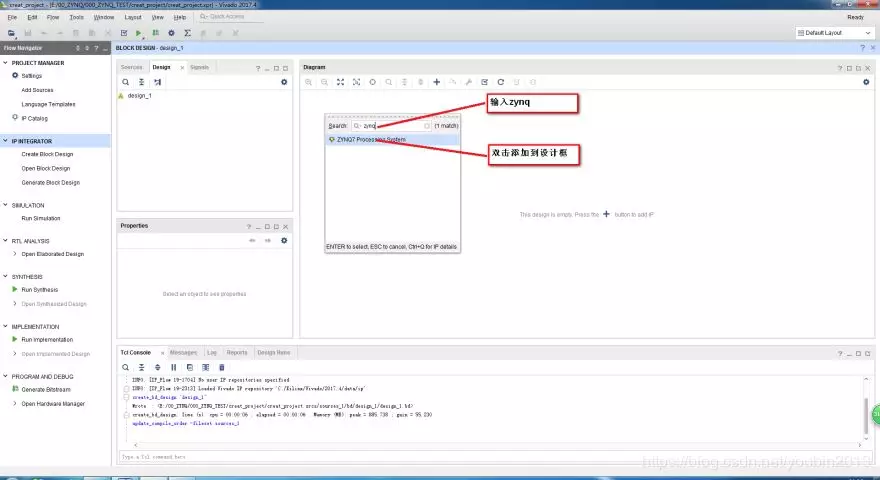

12,点击+号后添加ZYNQ的IP到设计框架中,如图所示,在输入框中输入zynq,下拉表中会有对应的zynq出现,双击下面的IP添加到设计框中。

13,添加zynq的ip后对话框如图所示,双击图中的ZYNQ核心IP,出现配置界面。

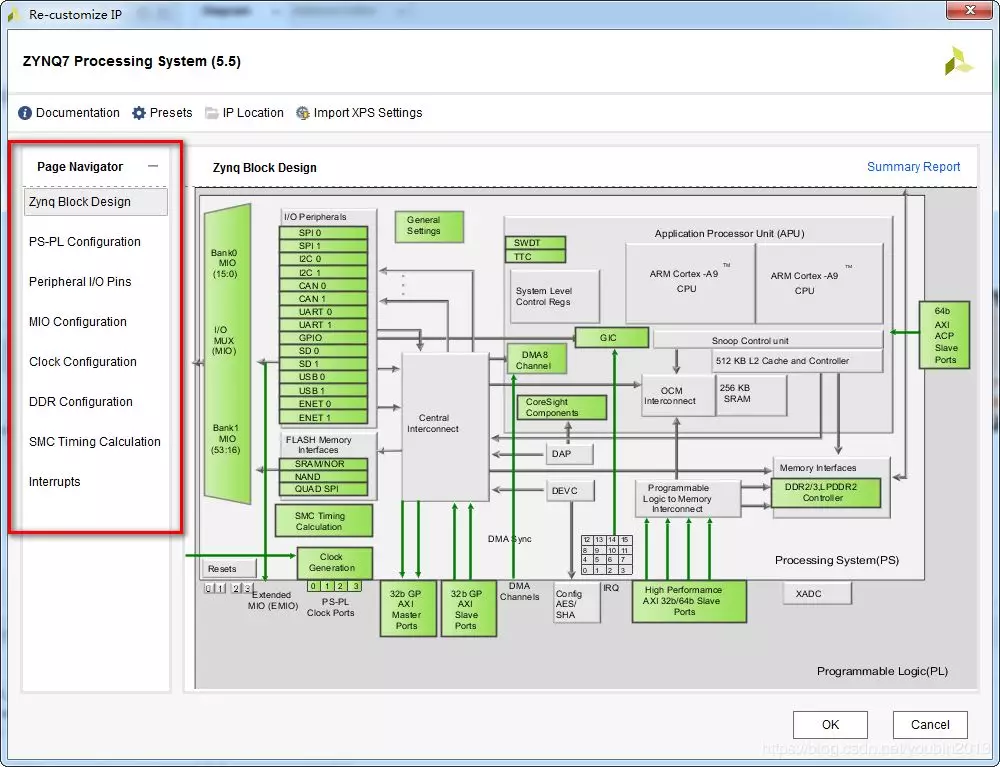

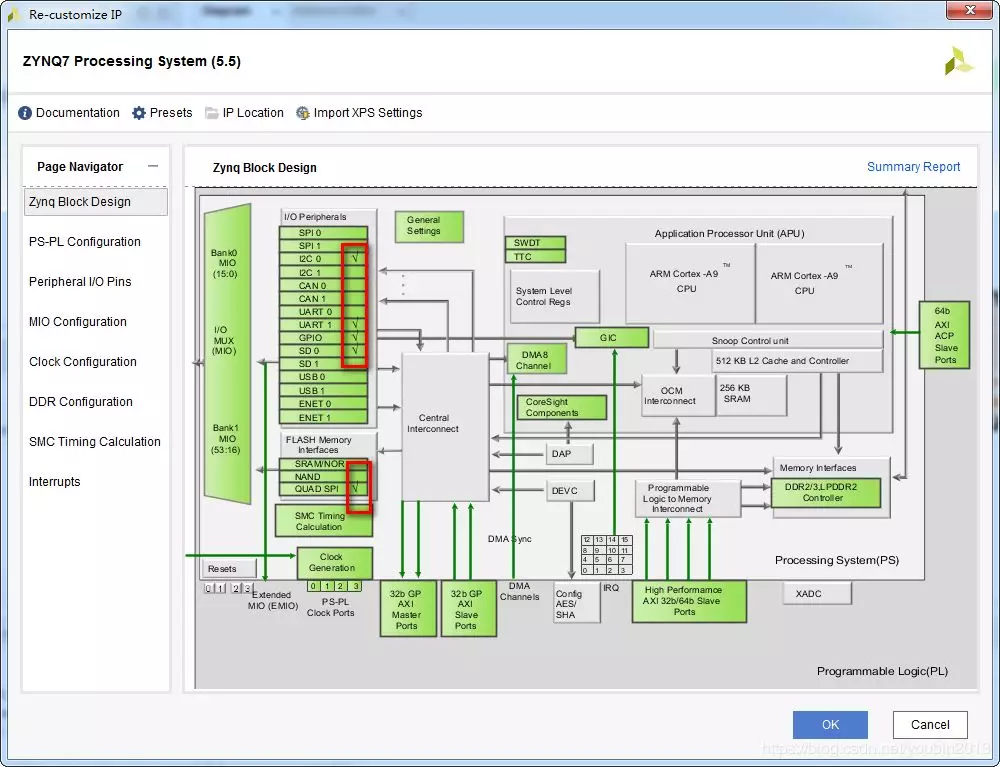

14,出现的配置界面如图所示,这时可以对ZYNQ进行配置了,其Page Navigator 界面下有 8 个子项,分别为 Zynq Block Design,PS-PL Configuration,

Peripheral I/O Pins,MIO Configration,Clock Configuration,DDRConfiguration,SMC Timing Calculation,Interrupts。这些页面选项是针对 ZYNQ 的不同硬件模块的配置,其中PS_PL 页面提供了 PS 到 PL 的相关接口配置信息以及 PS 部分一些配置信息;Peripheral I/O Pins 页面主要是对一些通用外设接口的配置;MIO Configruation 页面主要是对 MIO 以及EMIO 的分配控制;Clock Configruation 页面主要是对 PS 端时钟资源的配置和管理;DDR Configration 页面主要是对 DDR 控制器一些参数的配置;Interrupts 页面主要是对中断进行配置管理。

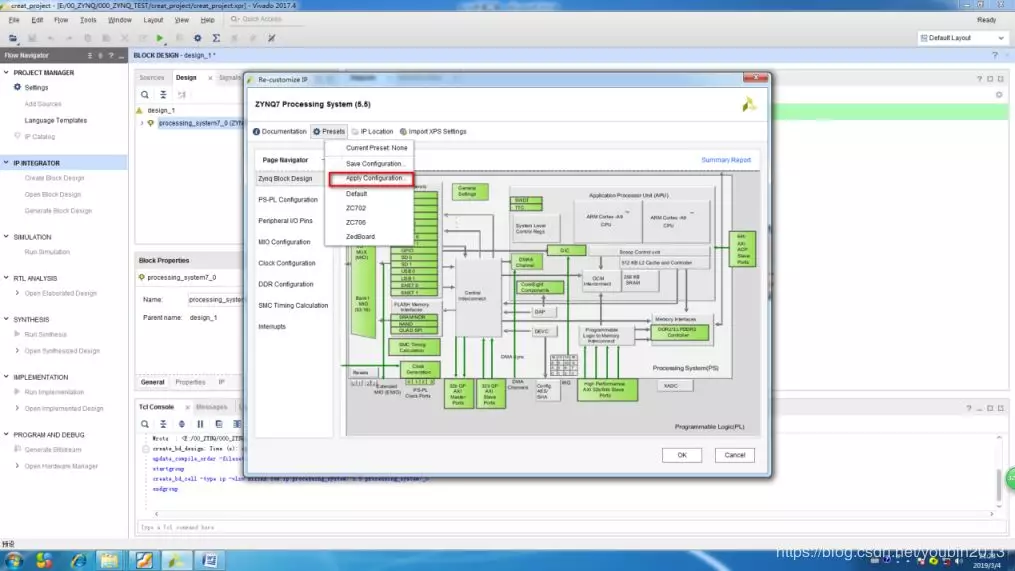

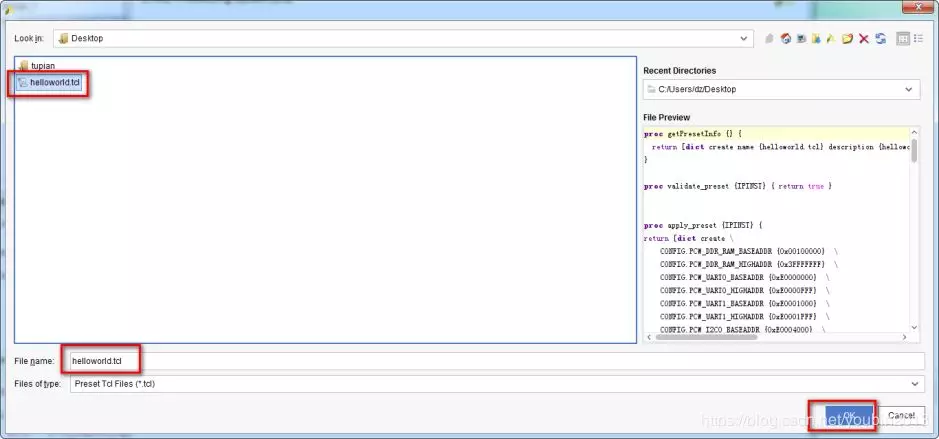

15,可以通过page navigator中的的八个设计单元分别去配置工程中zynq的硬件外设单元;也可以通过加载脚本的方式配置设计单元;这里通过脚本去设计ZYNQ器件的基本单元,点击presets,出现下列列表,选择apply configuration选项,如图所示。

16,然后出现选择脚本路径的对话框如图所示,选择之前保存的好的最小系统脚本,点击ok按钮,配置好ZYNQ的IP。

17,待配置好IP后会出现如图的对话框,表示配置好了相关的属性和外设,配置了的外设后面会打上勾,点击ok。

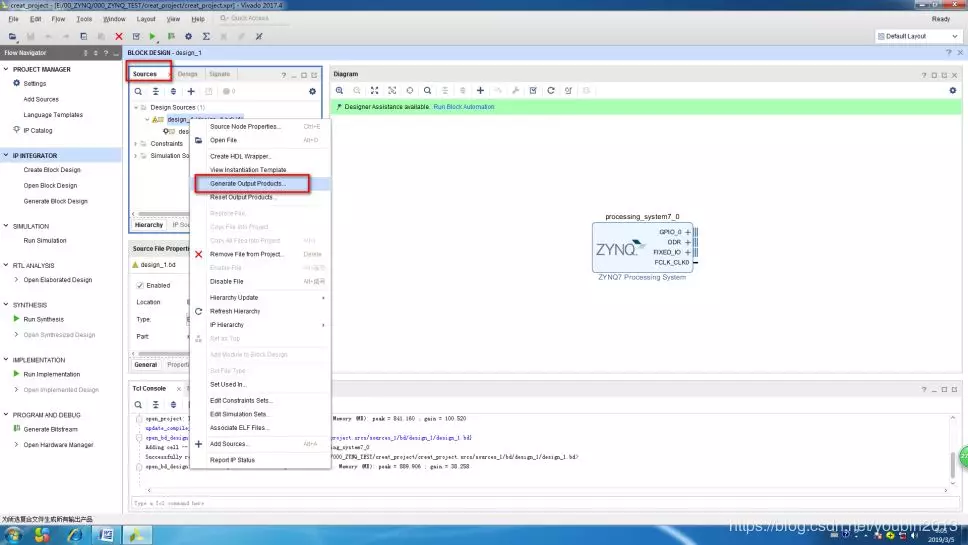

18,配置好IP外设后出现如图的对话框,点击红框中的source选项卡,然后鼠标右键点击在design sources下的design_1(design_1为刚刚设计的IP),在弹出的下拉列表中选择generate output products,生成输出的产品。

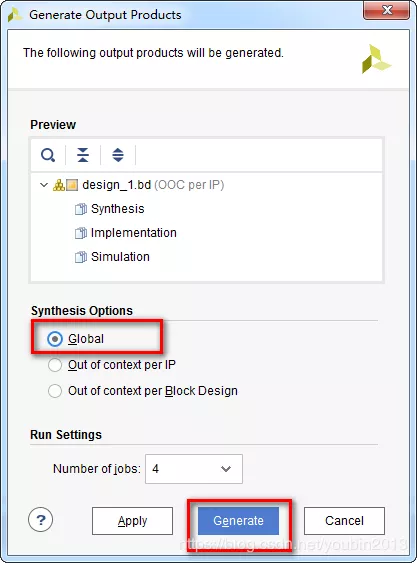

19,点击generate output products后出现对话框如图所示,表示将要生成输出产品,选择global,并点击下面的生成。生成成功后点击OK,

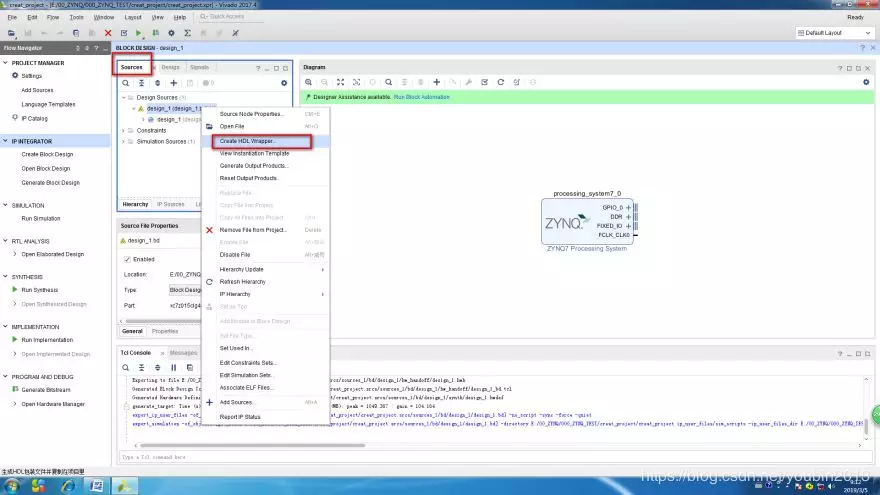

20,再点击红框中的source选项卡,然后鼠标右键点击在design sources下的design_1,在弹出的下拉列表中选择create HDL wrapper,如图所示,表示生成顶层文件。

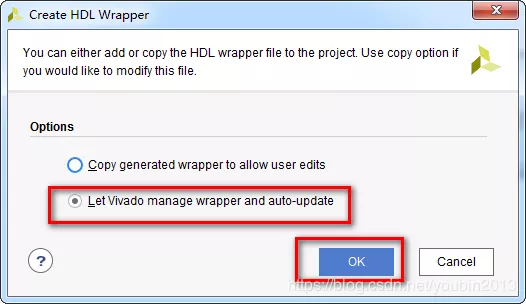

21,生成顶层文件成功后出现如图所示对话框,点击OK。

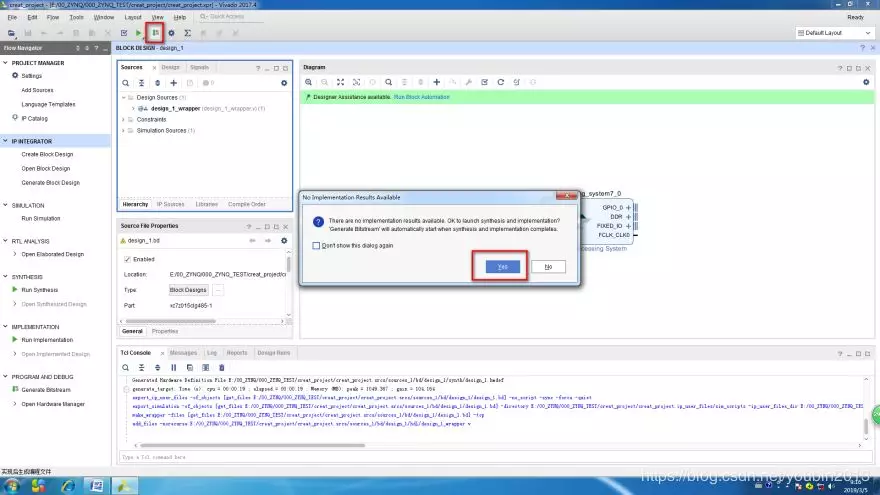

22,生成了顶层文件后,进行综合实现布线并生成.bit文件,如图所示,点击红框图标,然后出现对话框是否确认生成bit文件,点击yes,确定生成文件。

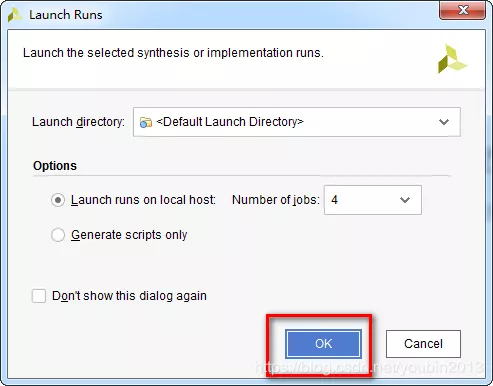

23,点击yes后出现对话框如图所示,点击ok开始生成bit文件。

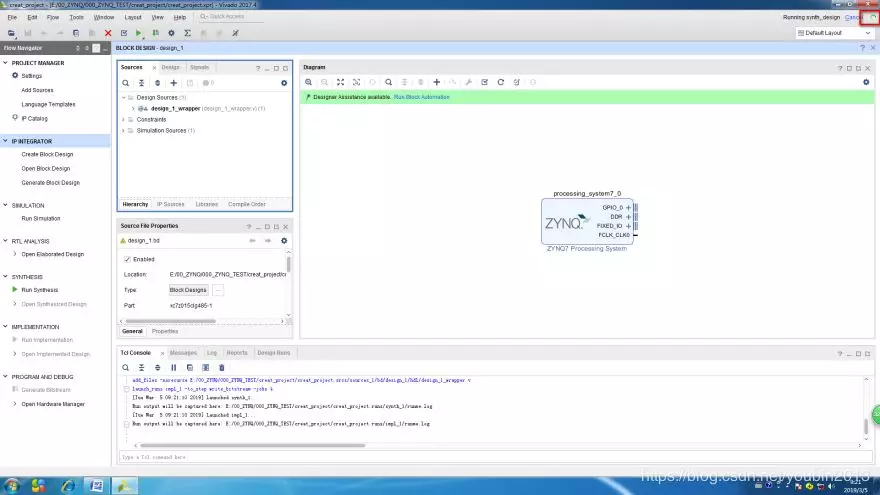

24,然后等待综合实现布线的完成,等待界面右上角的圈圈转完,表示.bit文件生成完成,如图所示。

25,生成成功以后会出现如图所示的对话框,右上角会有勾出现,并且提示是否看生成后的设备布线等具体信息,这里不看点击cancel。

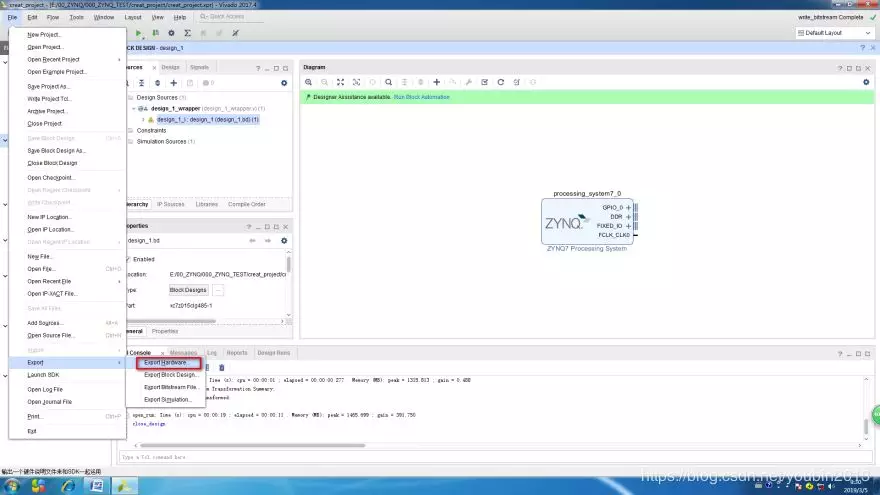

26,生成.bit文件以后,点击file菜单,在下拉列表中选择export,并且在子菜单中选择export hardware,生成硬件平台,供后续软件sdk使用,如图所示。

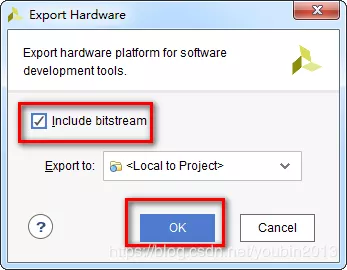

27,后续出现对话框如图所示,勾选上包含.bit文件,点击OK,表示生成硬件平台。

28,有了硬件平台后,点击file菜单,在下拉列表中选择launch SDK,打开ps端开发的SDK,如图所示。

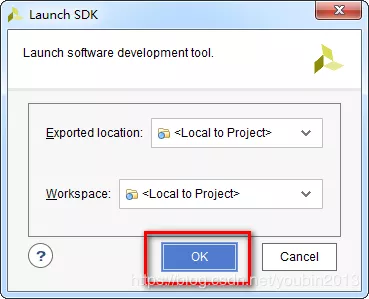

29,然后出现对话框如图所示,确认SDK的工作空间等信息,点击OK,至此开始进入到PS端开发SDK。

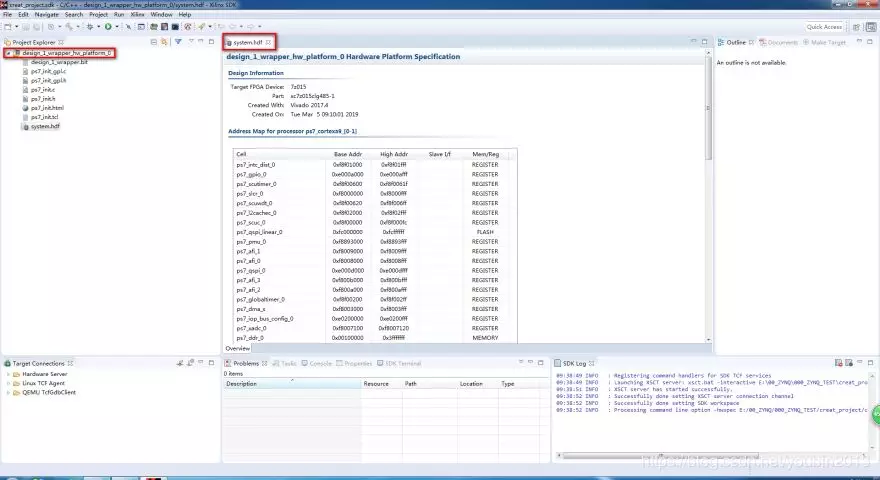

30,等待SDK打开完成,打开后出现界面如图所示,此时拥有了硬件平台design_1_wrapper_hw_platform_0。在system.hdf文件中会显示相应硬件平台外设的基地址和地址范围。

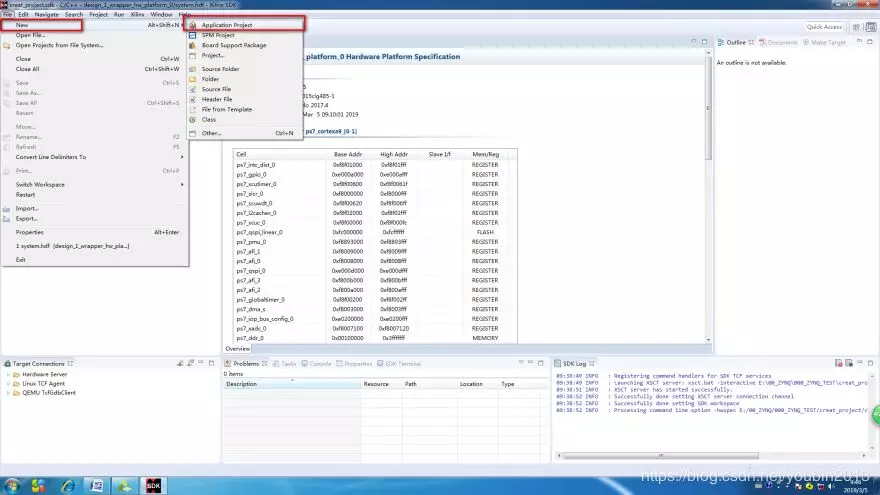

31,拥有硬件平台后,此时还需要建立软件工程,软件工程一般需要建立两个,一个是FBSL工程,一个是应用工程,FBSL工程是用来做固化启动芯片的工程,而应用工程则是需要实现的应用程序,这里先新建FBSL工程,点击file菜单,在下拉列表中选择new,在子菜单中选择application project,如图所示。

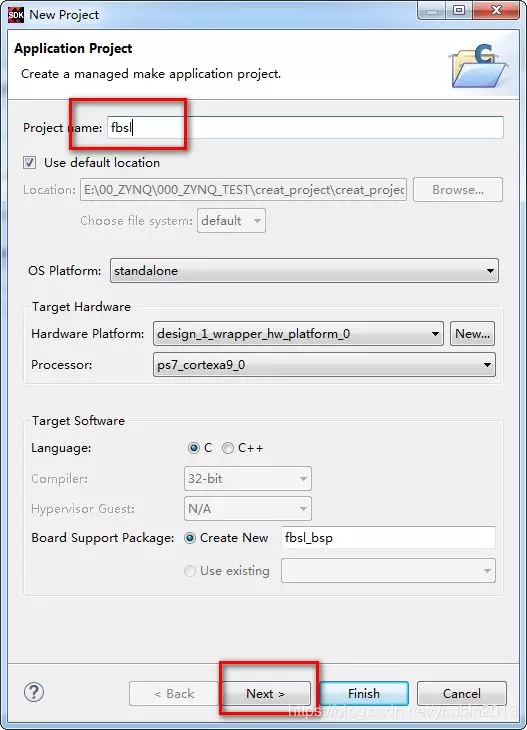

32,然后出现对话框如图所示,输入工程名字,选择工程路径,一般使用默认路径,选择系统平台standalone,选择上述的硬件平台design_1_wrapper_hw_platform_0,选择操作核心0核(ps_cortexa9_0),确定开发语言为C语言,创建新的板级开发包,然后点击下一步。

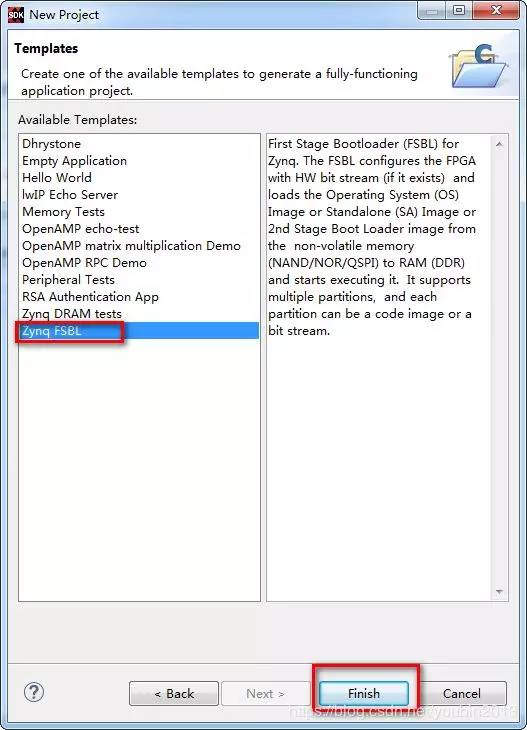

33,后续出现对话框如图所示,选择创建工程的模板类型,这里要创建FBSL工程,所以选择zynq fbsl类型模板,点击finish,完成工程的新建。

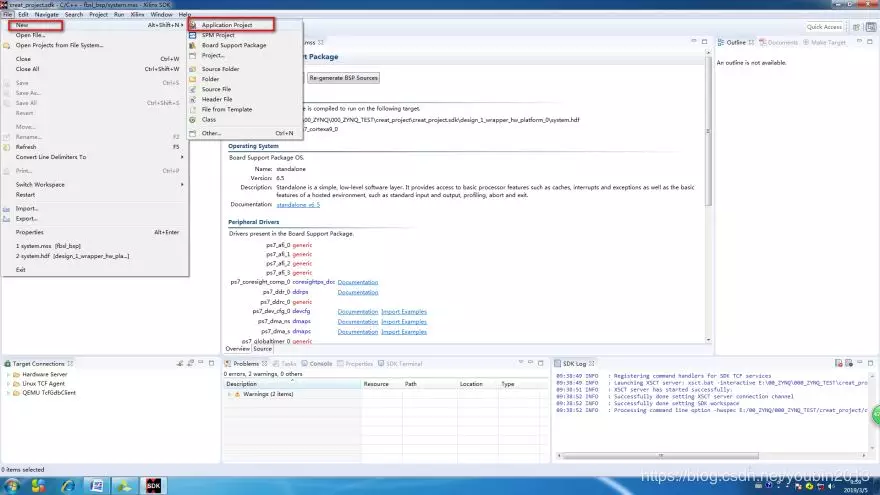

34,有了启动工程以后,还要有应用程序工程,所以在新建一个应用程序,这里再新建一个应用工程,点击file菜单,在下拉列表中选择new,在子菜单中选择application project,如图所示。

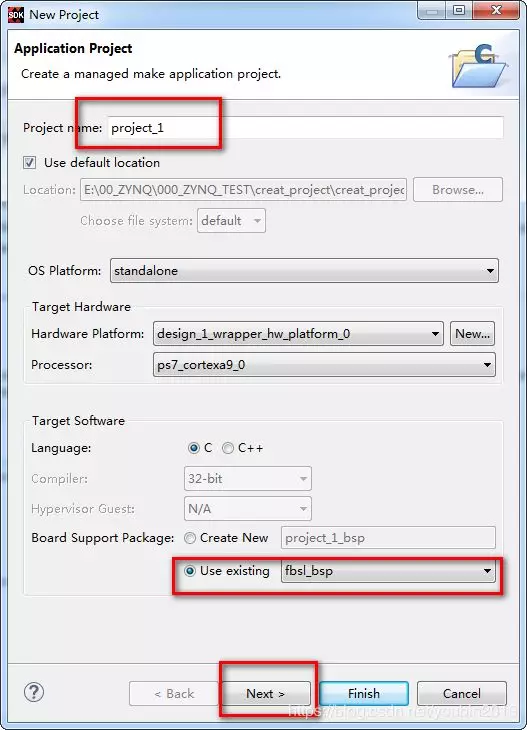

35,然后出现新建工程信息对话框,如图所示,输入工程名字,选择工程路径,一般使用默认路径,选择系统平台standalone,选择上述的硬件平台design_1_wrapper_hw_platform_0,选择操作核心0核(ps_cortexa9_0),确定开发语言为C语言,由于有了板级开发包了,所以这里使用之前创建的板级开发包,然后点击下一步。

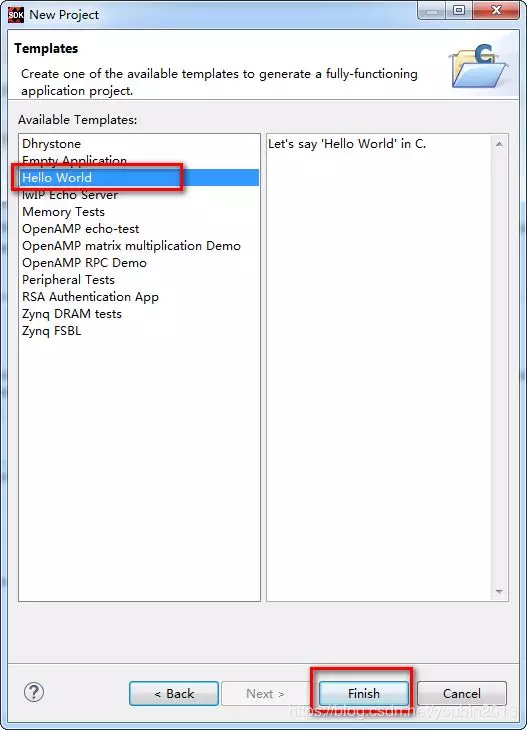

36,后续出现对话框如图所示,选择创建工程的模板类型,这里要创建一个helloworld模板应用程序,所以选择helloworld类型模板,点击finish,完成工程的新建。

使用调试

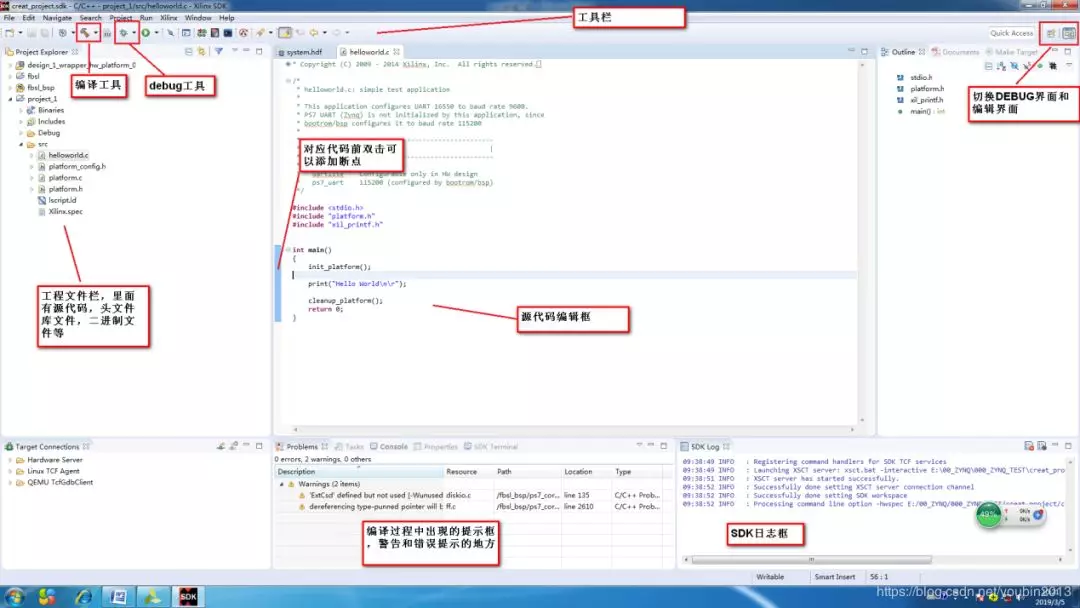

1,建立完工程以后需要进行在线调试程序,整个SDK中的界面分布如图所示。

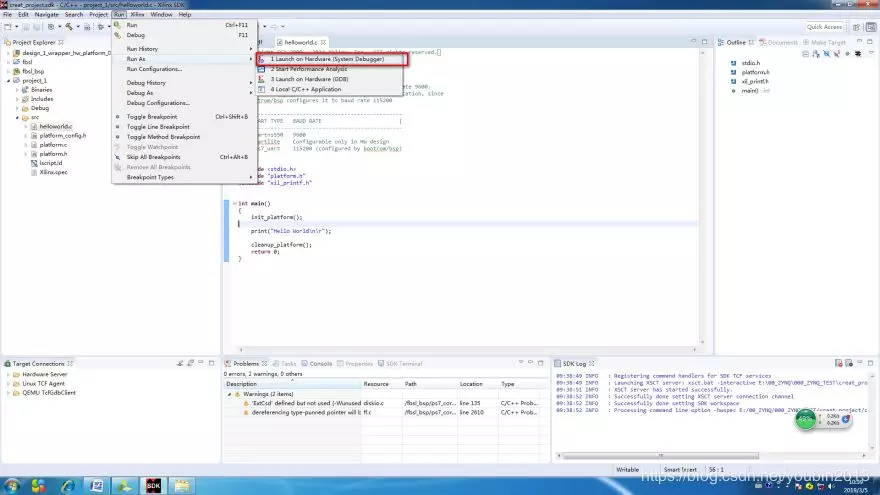

2,配置debug的一些相关设置,点击菜单栏上的run,会出现下拉列表,如图所示,在列表中会出现好多和debug相关的调试配置,有断点的配置,有运行的配置,这里先选择run as下的launch on hardware,选择在创建的硬件平台上运行程序。

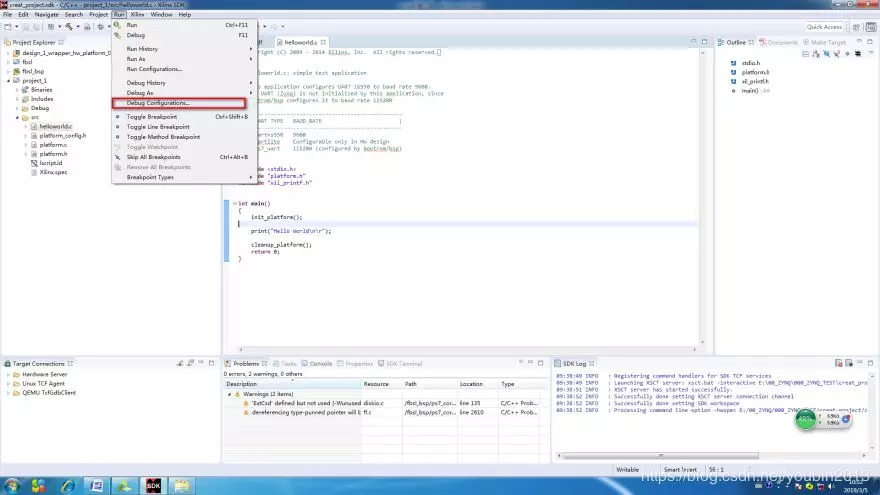

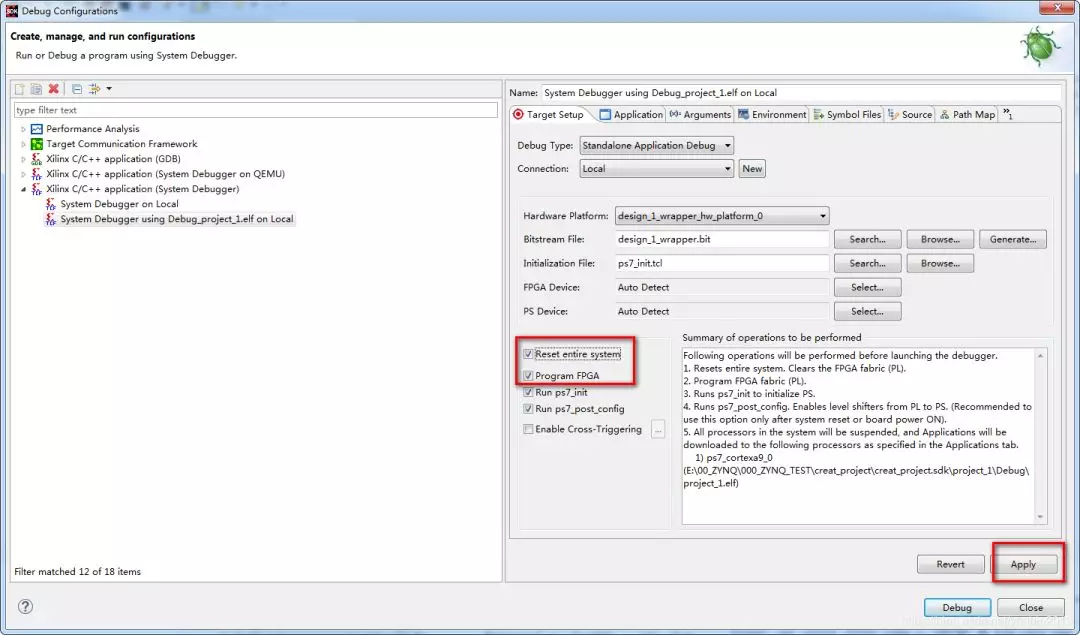

选择debug configurations,配置一些debug相关的信息,如图所示。主要是选择上复位整个系统和下载FPGA程序的操作,在这两个选项上打上勾,然后点击应用,主要是在进入调试模式时复位系统,并且下载好fpga程序。

3,点击小爬虫以后进入debug的界面,如图所示。其分布主要为:工具栏,核心选择栏,程序源码栏,变量监测栏,内存监测栏等,在图中红色框框中描述的功能是调试过程中经常用到的功能。

加载固化

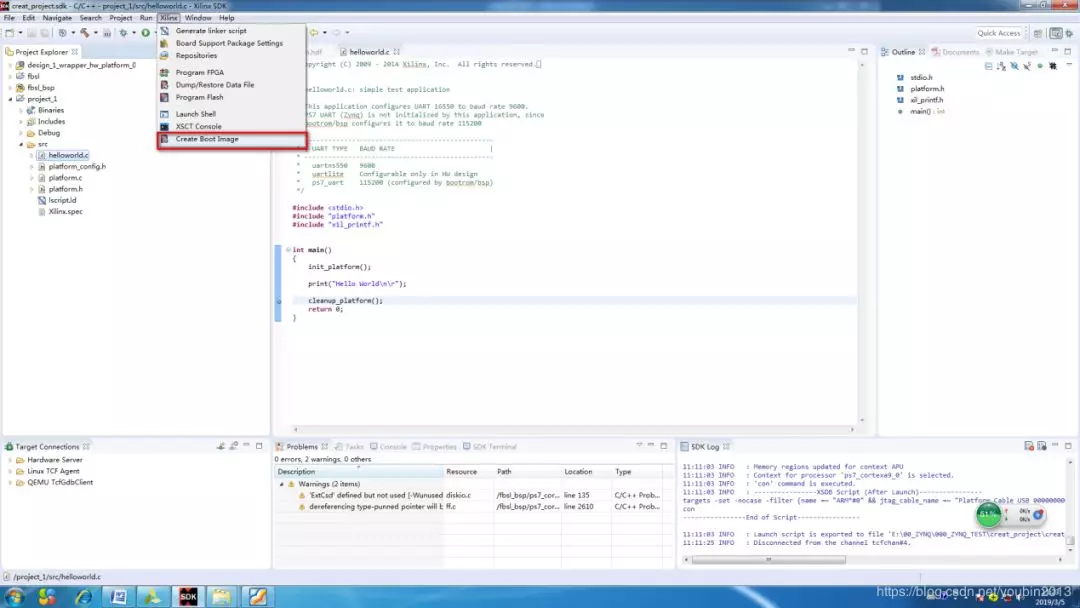

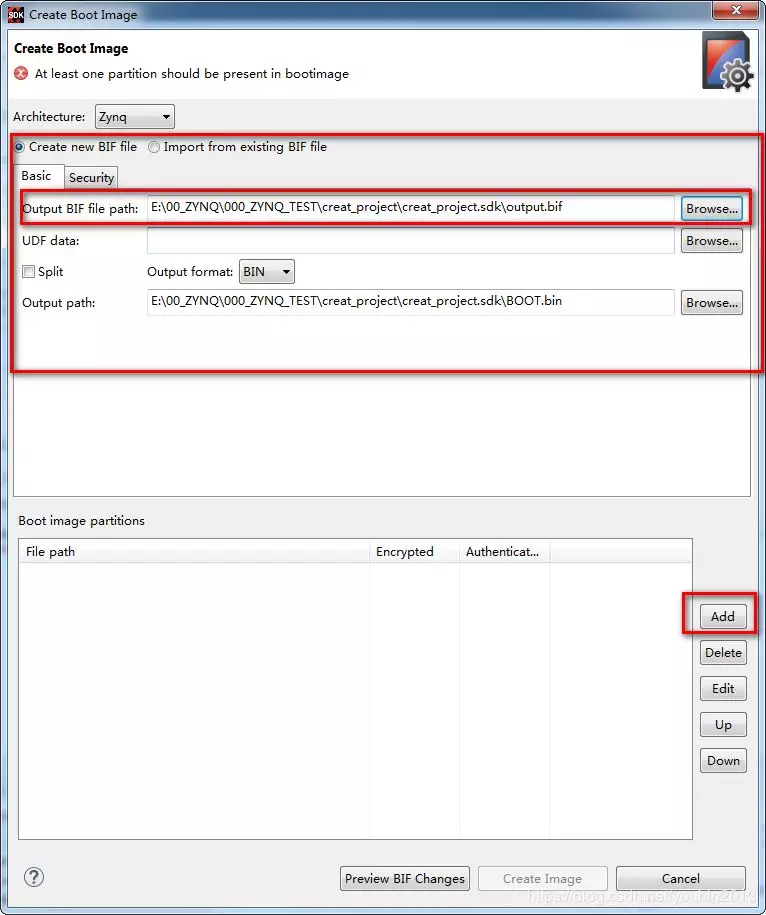

1,固化程序需要首先创建一个固化程序文件,然后将这个.bin文件下载到flash中;作为ZYNQ的固化程序,需要三个部分的程序,一部分为FBSL程序,该程序作为应用程序的bootloader;一部分为FPGA端的.bit文件,工程中的系统文件;还有一部分就是应用程序的文件了。使用SDK生成固化文件,选择菜单 Xilinx ->Create Boot Image,如图所示。

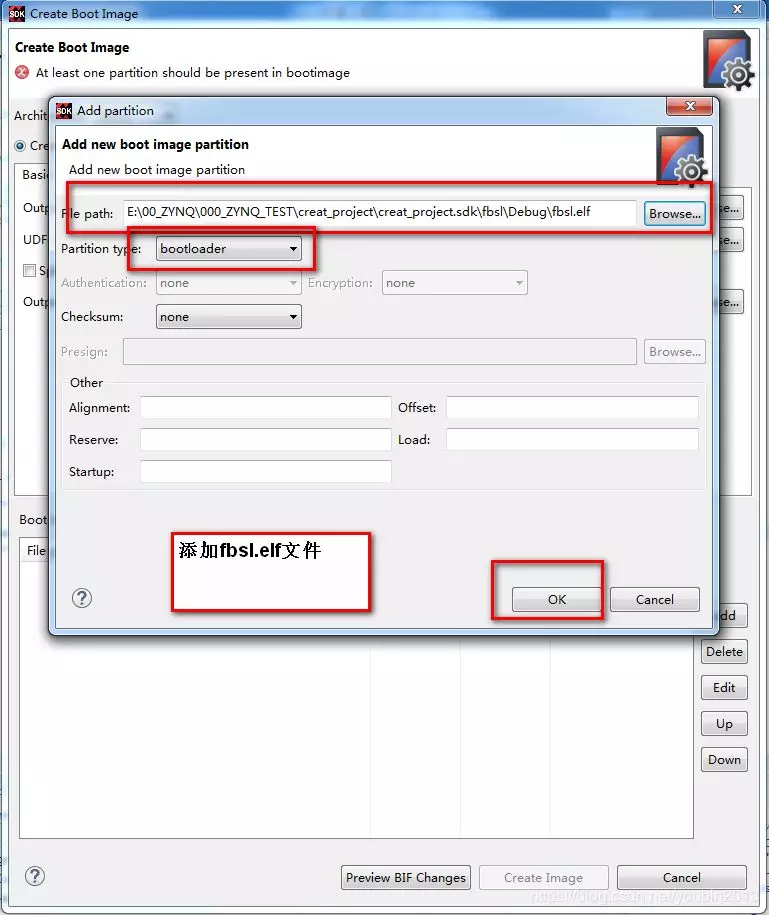

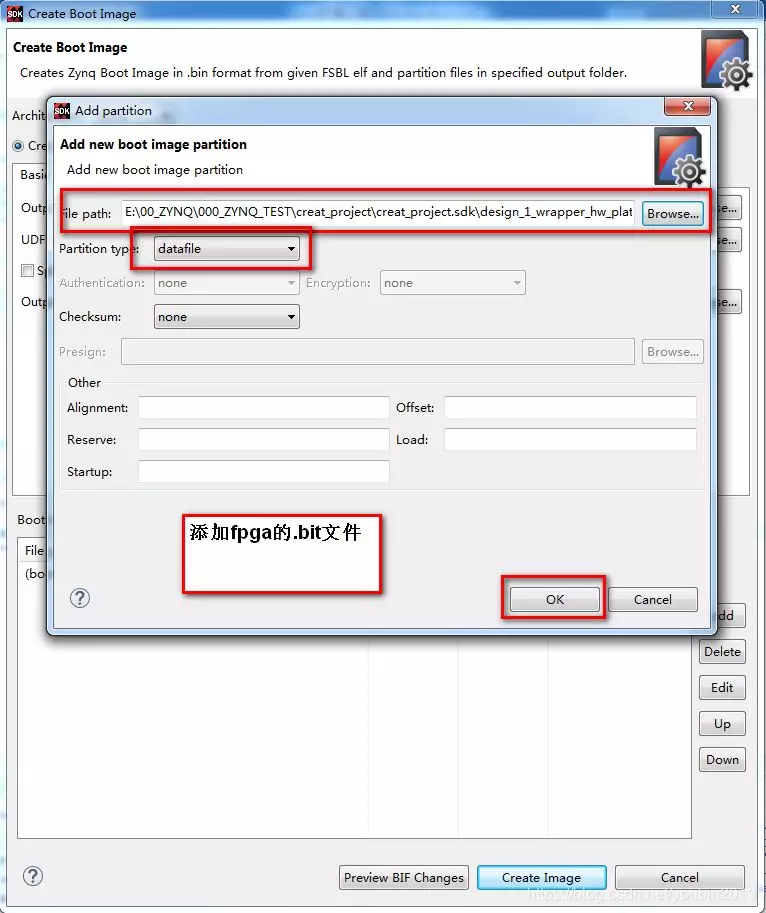

2,弹出对话框如图所示,输入生成固化程序的路径,点击output bif file path路径中的browse浏览生成路径,下面output path会和上述选择路径一样,然后在下方的框框中点击add,通过三次添加把fsbl程序文件,fpga端的.bit文件以及应用程序的.elf文件三个文件加入到boot image partion中,最后点击create image创建出固化程序。

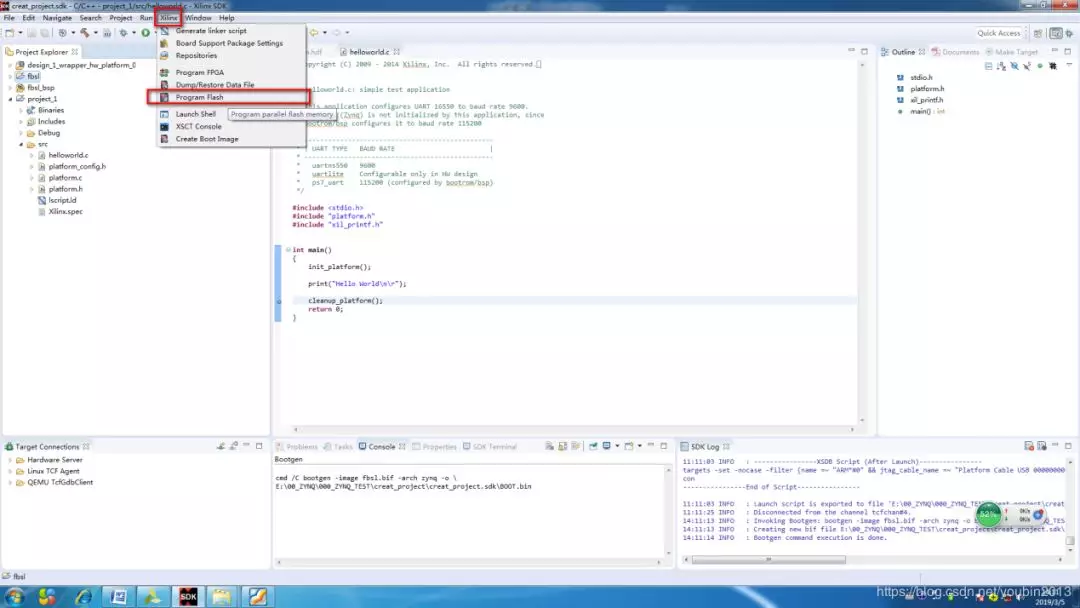

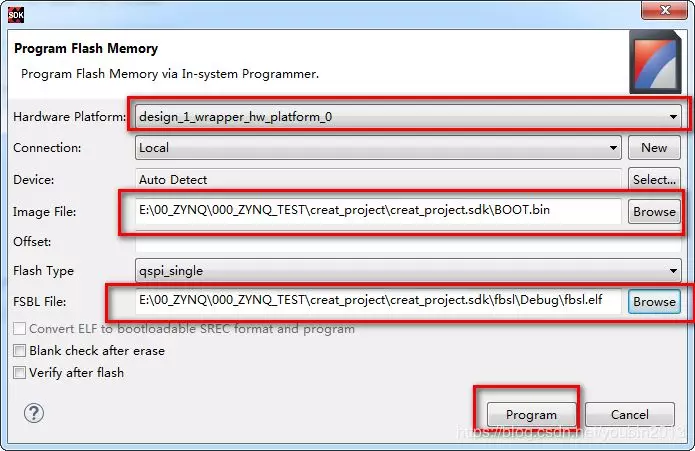

3,有了固化程序,还需要将程序下载到qflash中,需要用到SDK中的下载程序,在菜单栏中选择Xilinx下拉列表中的Program Flash,然后弹出下载对话框,如图所示。

4,对话框如图所示,需要选择固化程序文件的路径(Image File),还需要选择能够下载程序的FBSL.elf文件。

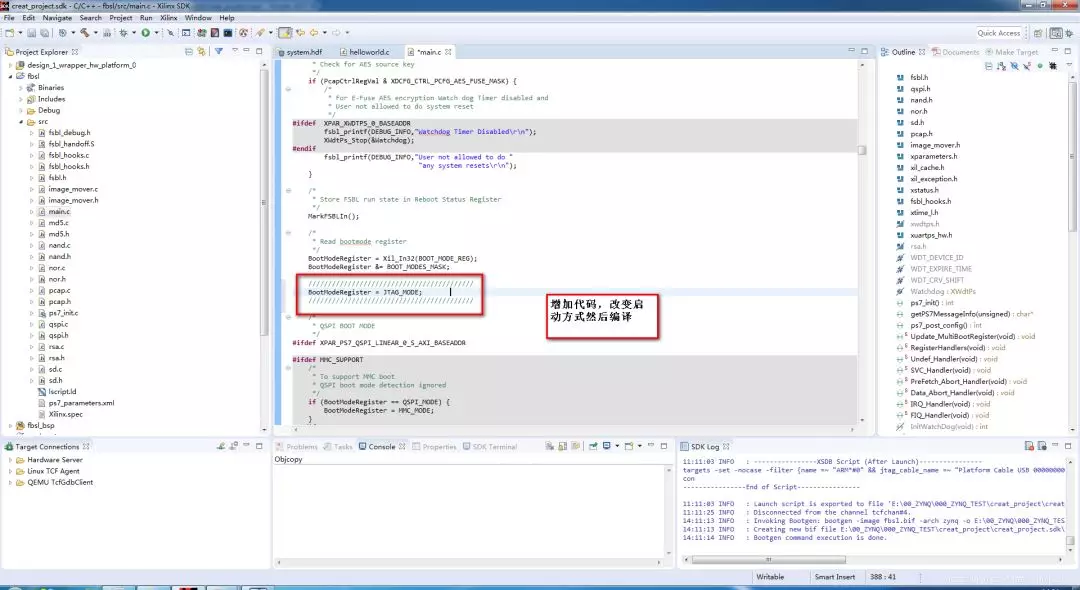

5,但是,使用的vivado版本为2017.4,在生成的FBSL.elf文件不能正常加载程序到qflash,在fbsl工程源码中可以看到启动方式为QFLASH,会对flash进行分区,无法正常下载,我们需要修改其启动方式为JTAG模式,然后编译,这样子生成的FBSL.elf文件才能做加载使用。修改源码如图所示。

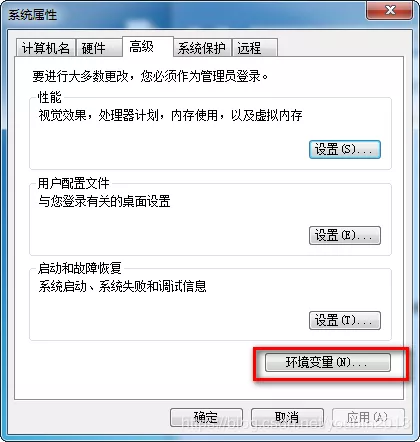

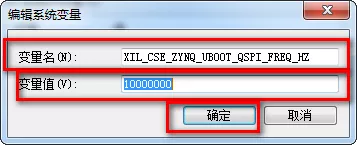

6,同时还需要添加环境变量到系统变量中,改变QSPI的时钟为10MHz,如图所示。右键点击我的电脑,点击属性,弹出对话框,选择高级系统设置;弹出对话框,点击环境变量;弹出对话框,在系统变量那一栏点击新建;弹出对话框,在变量名中输入XIL_CSE_ZYNQ_UBOOT_QSPI_FREQ_HZ,变量值中输入10000000,然后点击确定。

7,修改上面内容后进行加载,有了固化程序,还需要将程序下载到qflash中,需要用到SDK中的下载程序,在菜单栏中选择Xilinx下拉列表中的Program Flash,选择固化程序文件的路径(Image File)以及能够下载程序的FBSL.elf文件(修改后重新编译的fbsl.elf文件)。

注意:下载的fbsl.elf文件与生成固化程序的fbsl.elf文件是两个不同的文件,为了以后不需要做修改,可以将上述修改后的fbsl.elf文件单独放在一个路径中,在下载flash程序的时候选择这个路径下的fbsl.elf文件就可以了。

文章转载自: FPGA技术联盟