作者:默宸,来源:FPGA技术联盟

启动过程

设备配置包含用于初始化和配置ps和pl的所有方法及过程。在软件控制下,ps内的DevC提供用于初始化和配置ps和pl的手段和方法,在zynq中提供两个模块用于控制配置过程:

1. BootROM,一个静态存储块器块,当上电复位和暖复位后,有Cortex-A9的CPU执行这个内置程序;

2. 设备配置单元:用于控制JTAG调试访问和提供连接到AES、HMAC和PCAP模块的接口,用于实现对芯片内的pl的配置及数据的解密。

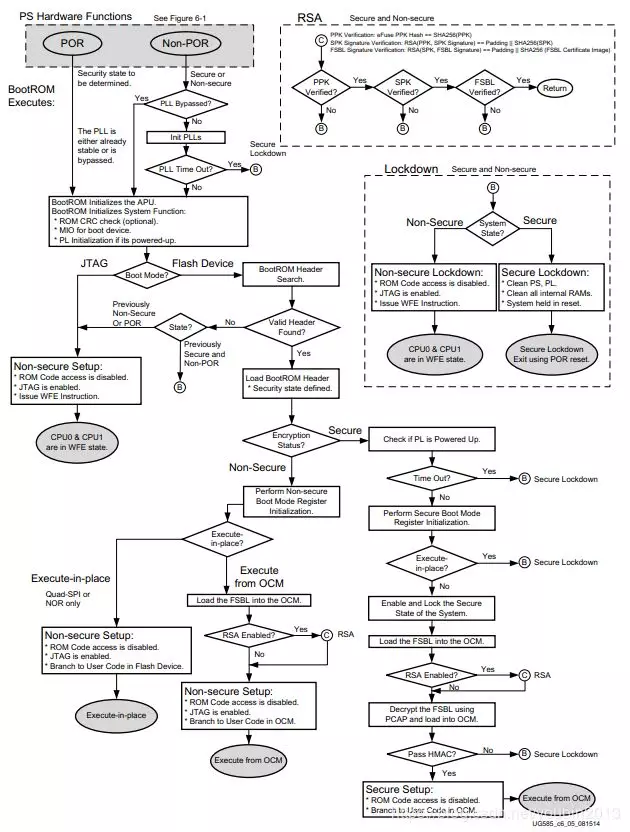

在ps的控制下,可以实现安全或非安全的配置所有ps和pl。通过zynq提供的JTAG接口,用户可以在外部主机的控制下对zynq进行配置,zynq不支持最开始就配置pl的过程。对zynq的配置过程至少包含两个阶段,但是通常要求3个阶段。

1. 阶段0:该阶段也称为BootROM,该阶段控制初始设备的启动。BootROM是上电复位或暖复位后,处理器所执行的用户不可修改的代码,该代码已经固化到zynq的BootROM中;

2. 阶段1:在该阶段,通常执行第一级启动引导程序。但是,它也可以是任何用户控制的代码;

3. 在该阶段,通常执行用户自己编写的软件程序,但是,也可以是第二级的启动引导程序,该阶段完全是在用户的控制下实现的。

zynq的BootROM

BootROM特性:

1. 提供3种不同的方法,用于配置PS:两个主模式和一个从模式,即安全、加密的镜像、主模式;非安全的主模式;通过JTAG的非安全从模式;

2. 支持4种不同的外部启动源:Quad-SPI Flash、NAND Flash、NOR Flash、SD;

3. 支持使用AES-256和HMAC(SHA-256)的PS安全配置;

4. 支持Soc调试安全性;

5. 从NOR和QSPI芯片内执行配置过程。

当上电复位后,启动PS配置过程,当禁止JTAG模式时,zynq内的Cortex-A9处理器从片内的BootROM开始执行代码,BootROM包含用于驱动NADN、NOR、Quad-SPI、SD和PCAP的基本程序代码。

在BootROM中并不执行对外设的初始化操作,在阶段1或该阶段之后zynq才对其他外设进行初始化操作,考虑到安全因素,当脱离复位状态后,Cortex-A9处理器总是PS内所有其他主设备模块内的第一个设备,当正在执行BootROM时,禁止执行JTAG,以保证安全性操作。

BootROM代码也负责加载第一启动镜像文件,zynq内的硬件支持加载多级用户启动镜像,在第一级启动之后,用户负责进一步实现用户启动镜像的加载,当BootROM将控制权移交给fsbl后,用户负责进一步实现用户启动镜像的加载,当复位操作时,才会重新执行BootROM内的代码。

BootROM支持加密和不加密的镜像,此外,当使用芯片内执行特性时,当从线性flash、NOR或QSP直接复制镜像或执行后,BootROM支持从OCM开始执行阶段1镜像。

在安全启动CPU时,从安全BootROM运行代码,并且,对进入的用户PS镜像镜像解码和认证,将其保存到OCM RAM中,然后,分支进入它,在非安全启动CPU时,从BootROM运行代码,如果使用了XIP特性时,在分支跳转到OCM ROM或Flash内的用户镜像时,禁止所有的安全启动特性,除非使用带有XIP的启动,一般将PS启动镜像限制到192KB范围内。

随后用于PS/PL启动阶段的过程,都是用户的责任,并且处于用户的控制下。在zynq中,不允许用户访问BootROM中的代码,在完成阶段1安全启动的过程后,用户可以继续执行后续的安全/非安全启动阶段,如果一开始执行的就是非安全的第一个阶段,随后只能执行非安全阶段的启动。

通过PL内硬接线的AES-256和SHA-256模块,PS实现解密和认证,由于这个原因,在安全启动任何阶段,即使只对PS进行配置,也必须给PL上电,这样,用户就可以通过片上的eFUSE单元或片上BRAM,选择器件的密钥。

在zynq内支持5种可用的启动设备,包括NAND、NOR、SD、Quad-SPI和JTAG,其中前4种启动源用于主模式启动。

1. 在主模式启动过程中,Cortex-A9处理器负责将镜像文件从外部非易失性存储器加载到片内的PS中。

2. JTAG只能用于从模式启动过程,JTAG只支持非安全启动,一个外部的电脑作为一个主设备,通过JTAG连接,将启动镜像加载到OCM,当加载启动镜像时,PS CPU保持空闲模式。

BootROM的高层次配置流程如图所示。

zynq的器件配置接口

设备配置接口结构DevC模块由3个独立操作的主模块构成:

1. 用于连接PL配置逻辑的AXI-PACP接口;

2. 设备安全性管理单元;

3. 一个XDAC接口;

设备配置接口包含一个APB接口,主机使用APB接口配置这3个模块,并且访问整个状态以及实现与PL XADC通信。

AXI-PCAP桥:

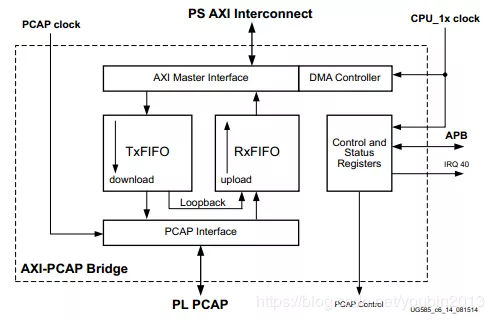

AXI-PCAP桥将32位AXI格式的数据转换成32位的PCAP协议,反之亦然,这个桥支持配置数据,以并发和非并发的方式下载和上传,如图所示。

在AXI和PCAP接口之间存在一个发送和接收FIFO缓冲区,图中的DMA引擎用于在FIFO和存储器设备(OCM、DDR存储器,或者外设存储器的一个)之间移动数据。

当通过PCAP接口移动数据时,必须给zynq的PL一端供电,通过DevC控制器寄存器的PCAP MODE和PCAP PR比特位,使能PCAP接口,如果发送加密数据,还应该设置QUARTER PCAP RATE EN比特位。

通过DevC模块内建的DMA引擎,在PCAP接口之间传输数据。为了启动一个数据传输过程,必须按照下面的顺序写4个DMA寄存器:DMA源地址寄存器;DMA目的地址寄存器;DMA源长度寄存器;DMA目的长度寄存器。

为了通过PCAP将数据传输到PL,目的地址应该设置为0xffffffff。类似的,通过PCAP接口从PL读数据,源地址应该设置为0xffffffff,必须通过PCAP接口发送加密的PS镜像,这是由于AES和HMAC引擎都驻留在PL一端。在该情况下,DMA源地址应该设置为一个外部的存储器接口,而目标地址应该设置为OCM。

DevC的DMA引擎能用于加载不安全的PS镜像,在加载以前,在杂项控制寄存器内设置PCAP LPBK比特位,这个比特位使能内部的环路,旁路掉PCAP接口,在使用PCAP前,需要再次禁止该比特位,DMA源地址应该设置为一个外部存储器,而目的地址应该设置为一个OCM或一个有效的外部存储器接口,如DDR。

PCAP接口也用来回读PL配置。为了执行回读操作,PS必须运行软件代码,使能产生正确的PL回读指令,使用两个DMA访问周期,回读一个PL配置。

设备安全性管理:

DevC包含着一个安全策略模块,提供如下功能:

1. 监控系统安全性,当检测到冲突的状态时,能确认一个安全复位,这个状态能表示不一致的系统配置或篡改;

2. 通过APB接口控制和监视PL配置逻辑;

3. 控制ARM CoreSight的调试器访问端口DAP和调试级;

4. 提供片上ROM控制。

XADC接口:

1. 读和写XADC寄存器;

2. 15个深度的写命令FIFO和15个深度的读FIFO(32位宽度);

3. 可编程的FIFO级中断;

4. 报警中断;

5. 过温度中断;

PS主设备非安全启动

在这个启动模式下,PS作为主设备。BootROM从选择的外部存储器加载一个纯文本PS镜像,如图3.2所示,在这种情况下,并不要求PL上电,可以使用PS镜像立即加载或以后加载PL比特流。

配置流程主要步骤如下:

1. 设备上电复位;

2. BootROM执行:1,读自举程序,以确定外部存储器接口类型;2,读启动头部信息,以确定加密的状态和镜像目标;

3. BootROM使用DevC的DMA,将FSBL加载到OCM或其他有效的目的地址;

4. 通过PCAP,FSBL加载PL比特流。

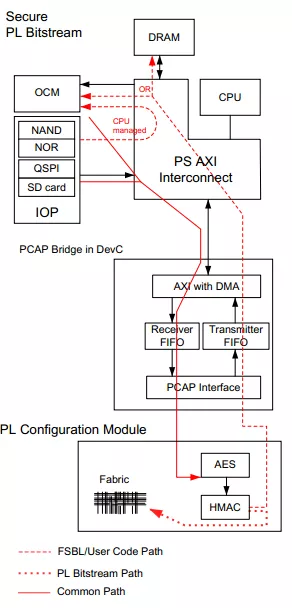

PS主设备安全启动

在该启动模式下,PS作为主设备,BootROM从所选择的外部存储器加载一个加密的PS镜像,如图3.3所示,由于AES和HMAC引擎驻留在PL中,因此要求PL上电来初始化启动序列,在尝试解密FSBL前,BootROM验证PL已经上电,当启动PS后,可以使用一个加密的比特流配置,或者断电以后再配置PL。

下面给出了配置流程的详细步骤:

1. 设备上电复位;

2. BootROM执行:1,读自举程序,以确定外部存储器接口;2,读启动头部,以确定加密的状态(安全);3,确认PL上电,开始解密FSBL;

3. BootROM使用DevC DMA引擎,通过PCAP,将加密的FSBL发送的PL内的AES和HMAC;

4. PL使用PCAP将解密的FSBL返回到PS,然后,在此将其加载到片内OCM;

5. 关闭BootROM,释放CPU用于控制FSBL;

6. FSBL使用一个加密流配置PL。