作者:安平博,Xilinx高级工程师;来源:AI加速微信公众号

引言

做图像处理没有显示怎么能行,所以用两章来介绍HDMI的协议以及编码实现。HDMI的编码,仿真和调试会花费较长时间,特别是第一次在windows环境下部署UVM环境,对于刚刚入门UVM的我来说,这块也花费了很长时间。截止目前设计和仿真的代码都已经做完。所以这章主要介绍HDMI的协议以及设计的架构,之后再用一章来介绍HDMI的实现和驱动编写。

HDMI协议简介

HDMI包含物理层和链路层结构,物理层定义了信号的物理接口,以及物理层物理层编码方式。链路层定义了帧格式,包含了图像,声音,和控制信息。

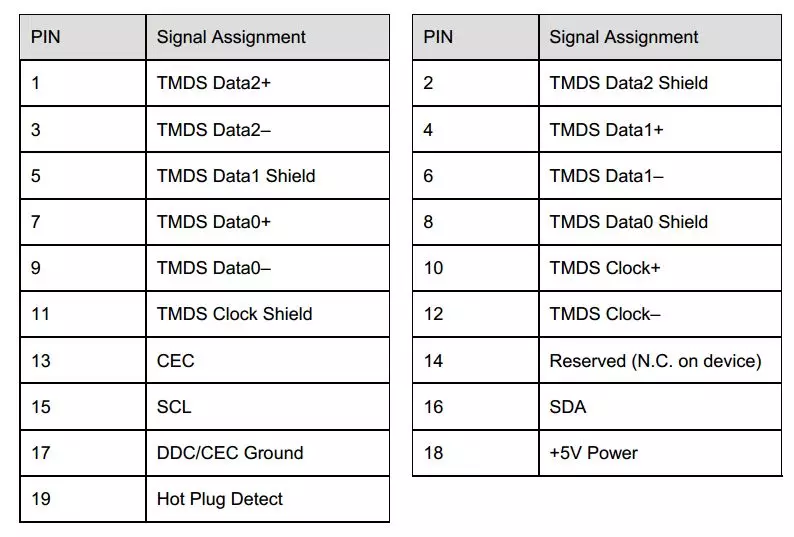

1)物理层信号

TMDS Data:采用差分传输,共有三路。

TMDS Data shield:

TMDS clock:A类型的时钟频率小于55MHz,即最大传输165M pixels/sec。

TMDS clock shield:

SCL:串口通信时钟。

SDA:串口通信数据通路。

CEC:用户可以通过CEC协议对设备进行控制。

Hot Plug Detect:对供电电源进行检测信号,提示电源超过或者不足。

图1.1 物理层信号定义

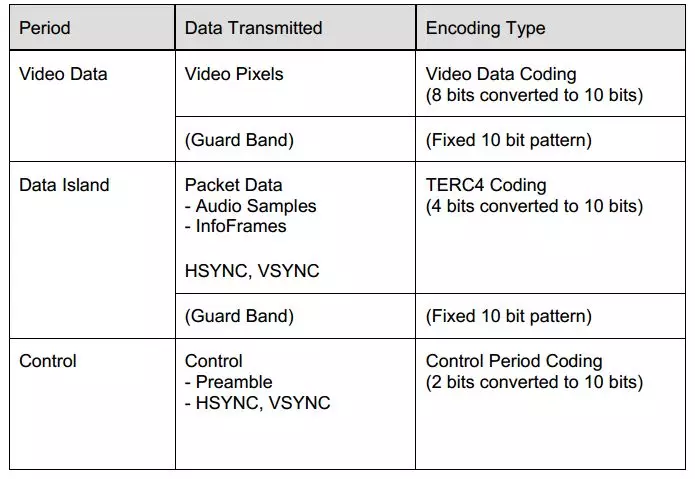

2)链路层结构

链路层主要包含如下信息:

图1.2 链路层包含信息

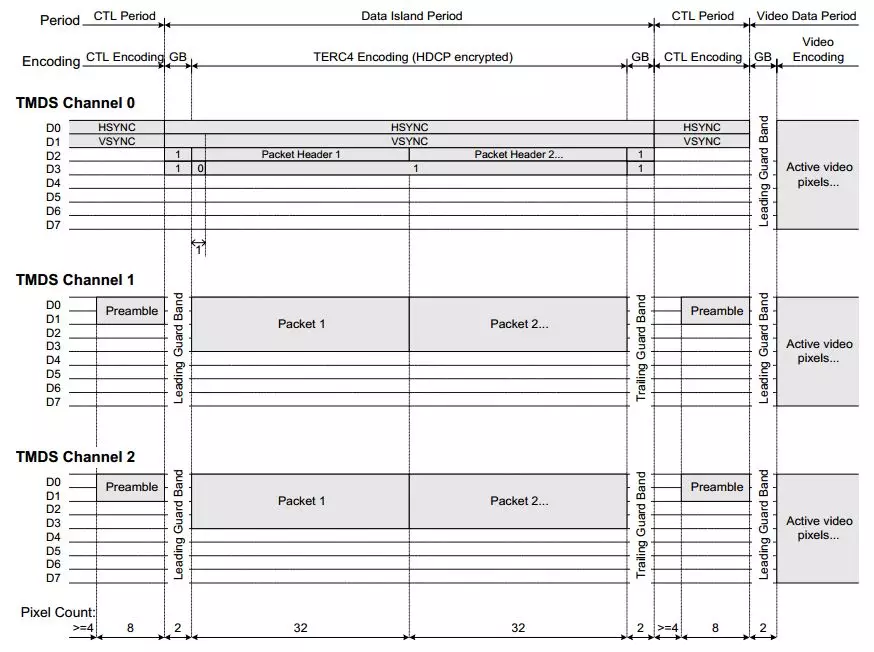

整个传输的帧时序结构如图1.3:其中HSYNC、VSYNC是图像同步信号,都为高电平,表示是有效图像数据。Preamble用于区分数据类型,具体如图1.4。video数据以2bit的leading gurad band开头,之后是连续的一行图像数据。Data island用于传输声音信息,一些音视频描述信息等。Data island被放置于非有效video图像区域。这部分不是必须的,我们进行图像处理仅仅用于显示处理,所以不进行data island字段设计。这部分介绍略过。

内容

图1.4 preamble结构

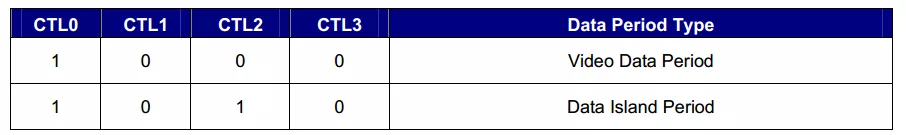

3)物理层编码

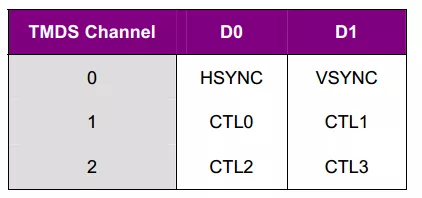

控制信号包括HSYNC、VSYNC以及CTL0……2。其具体映射到物理传输线上为:

Case(D1, D0):

0, 0: q = 10b1101010100;

0, 1: q = 10b0010101011;

1, 0: q = 10b0101010100;

1, 1: q = 10b1010101011;

Endcase

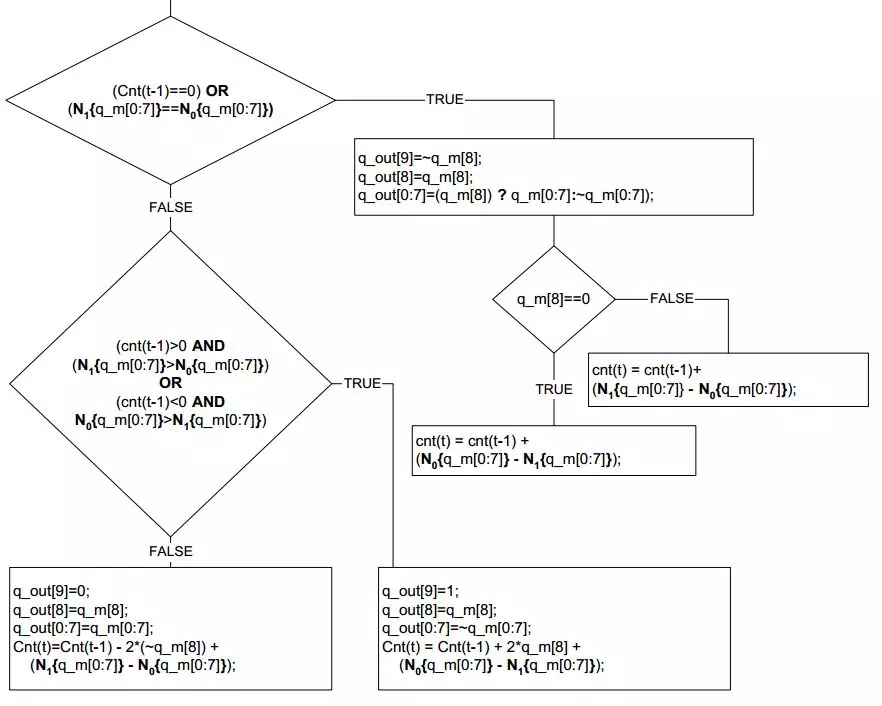

Video数据8bit被编码为10bit,这样可以降低TMDS物理路径上电位转变次数。算法如下:

图1.5 video data物理层编码

HDMI设计架构

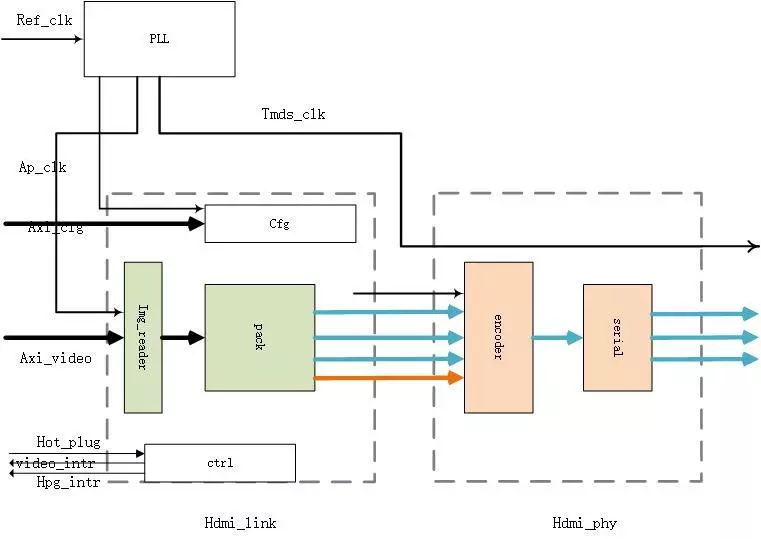

HDMI设计中不包含data island的结构解析,因为仅仅用于显示。整体结构如图2.1。包含两大部分:

1)hdmi_link

用于从ddr中获得图像数据,并封装成链路层格式。其中cfg是通过arm端实现寄存器配置,包括图像的起始地址,大小,图像长宽,blank的大小等。Ctrl是实现对HDMI的整体控制,包括使能HDMI发送,处理hotplug以及产生HDMI传输中断等。Img_reader通过axi总线从DDR中获得图像数据,pack是完成链路层格式的打包,并发送到物理层。

2)hdmi_phy

这层主要是将链路层帧结构进行物理编码,并转换为串行数据发送出去。Encoder就是对帧结构进行编码,每8bit转换为10bit数据。Serial中用到了芯片的SERDERS,将并行10bit数据转化为高速串行数据。

3)PLL

产生两种时钟信号:一种用于链路层数据打包和读取等,而tmds_clk是高速串行时钟。用于提供给物理接口。

图2.1 HDMI设计结构

验证架构

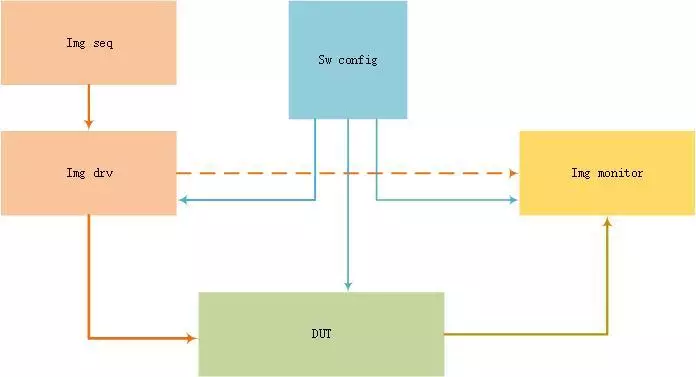

这部分用UVM来实现的,利用了UVM的基本架构。大致如图3.1。

1)img_seq,img_drv

产生图像并通过axi发送给DUT,同时将数据发送给img_monitor用于产生对比数据。

2)sw config

模拟软件行为,配置寄存器数据。

3)img_monitor

获取原始img数据产生对比文件,然后拉取DUT中link层和phy层数据,进行对比。输出对比结果。

图3.1 UVM验证架构

总结

简单介绍了HDMI协议,并设计了HDMI显示架构。完成了设计和仿真代码。下一章将会介绍仿真和调试过程。

文章转载自:AI加速