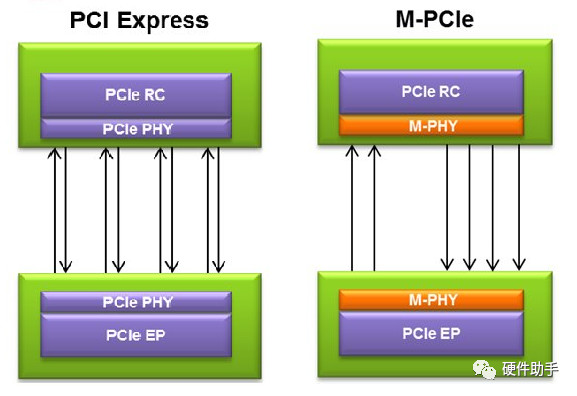

M-PCIe即Mobile PCIe,主要应用对象是智能手机等嵌入式设备。PCI-SIG在PCIe Spec V3.1中引入基于MIPI M-PHY V2.0的M-PCIe。相比于标准的PCIe总线,M-PCIe ECN主要的改动在物理层,通过引入M-PHY,旨在获得更低的功耗以适应嵌入式设备的低功耗要求。

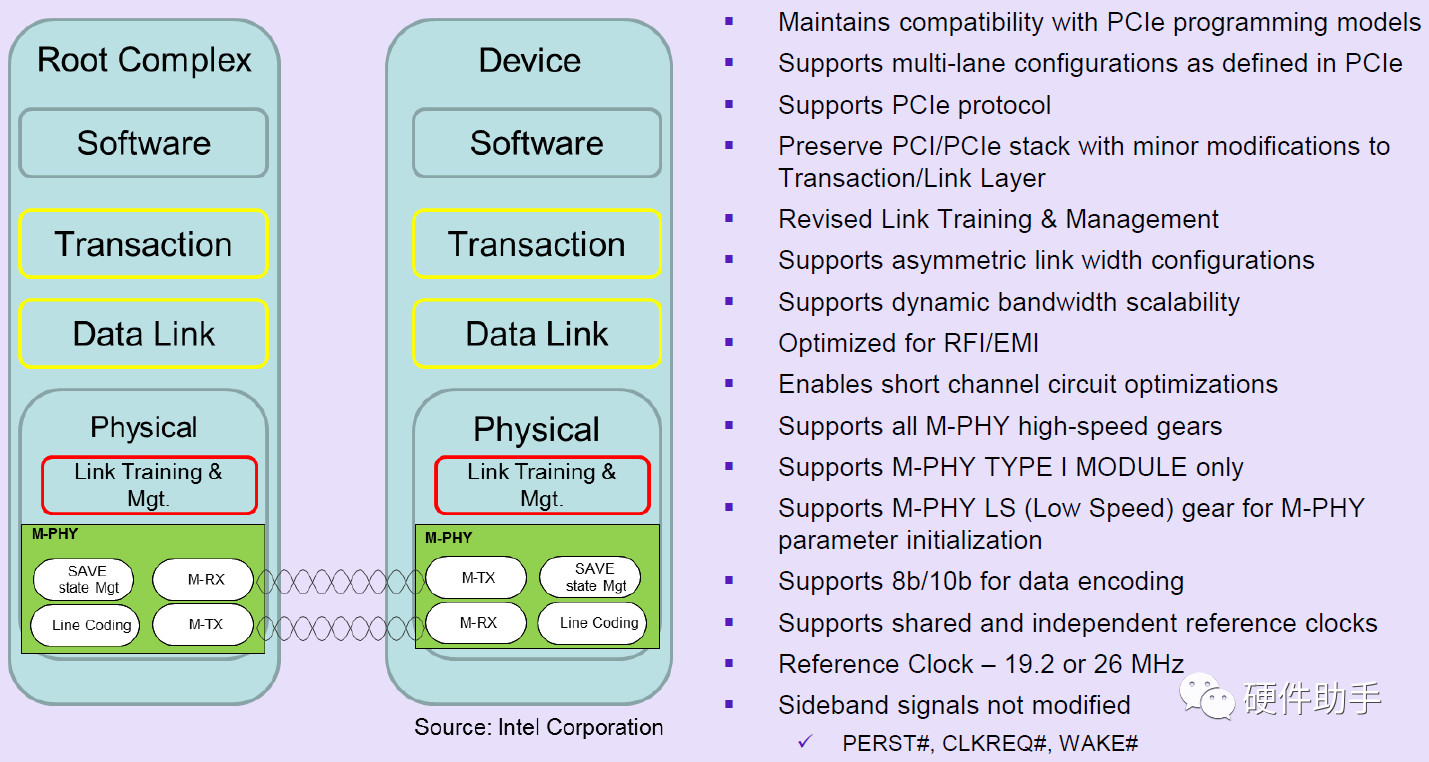

M-PCIe的主要特性如下:

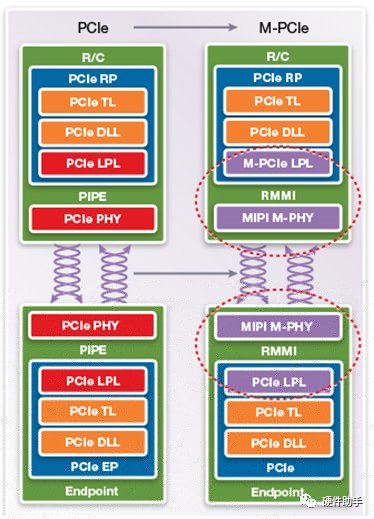

M-PCIe的上层协议层、事务层(TL)、数据链路层(DLL)和标准PCIe总线是兼容的。M-PCIe和PCIe设备的Link Training and Status State Machine (LTSSM)具有不同的设计,这主要是为了保证M-PHY独特的低功耗特性。

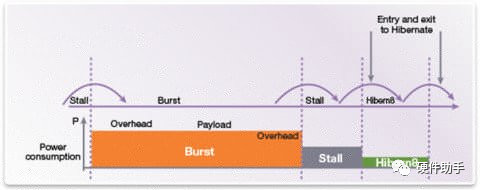

由于其工作模式与各个突发传输之间的关系,M-PHY甚至可以进一步降低功耗。在M-PHY设计中,PHY仅在实际传输时处于最大功率。在完成突发传输后,PHY进入超低功耗的“STALL”状态,此后不久就进入其最低功率的“HIBERN8”状态。通过这样的设计,可以使得M-PHY的功耗降至最低,从而延长电池寿命。

为了进一步降低功耗,M-PCIe系统可以实现非对称链路,允许链路上不同数量的发送器和接收器。PCIe强制设备具有4个发送器和4个接收器,以满足其对4个通道的PCIe-to-cellular带宽的需求。而M-PCIe允许设备将发送器的数量减少到所需的量,并且在这种情况下,功耗会更低。

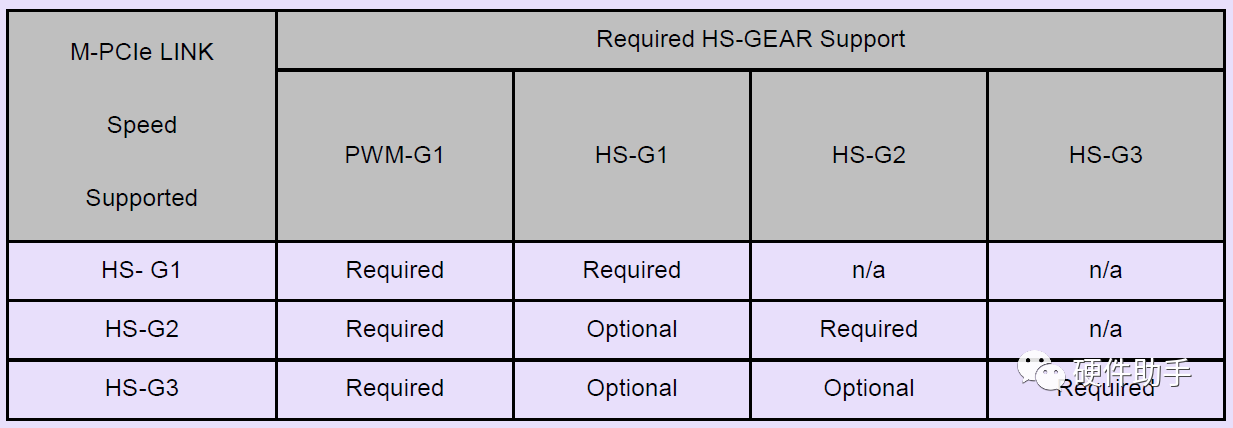

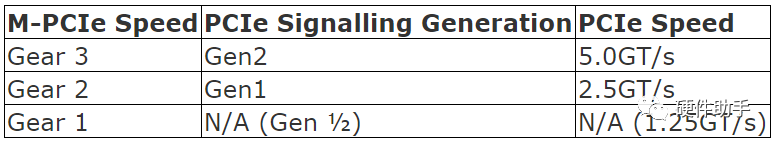

虽然M-PCIe规范允许设备比PCIe PHY消耗更少的功耗,但PCIe提供的速度也高于M-PCIe。一般而言,可以将M-PHY Gear M视为与PCIe Generation (M-1)相同的带宽。

以上就是针对M-PCIe的简单介绍,详细可参考PCIe spec和MIPI M-PHY spec。

文章转载自:硬件助手