注意:本文所有内容皆来源于Xilinx工程师,如需转载,请写明出处作者及赛灵思论坛链接并发邮件èï¼æªç»Xilinxåèä½æ人许å¯ï¼ç¦æ¢ç¨ä½åä¸ç¨éã

BY Hemang Divyakant Parikh

æå¤ç§ç±»åçæ¶åºè¿ä¾å¯å½ç±»ä¸ºèå²å®½åº¦è¿ä¾ã

- æ大åå·®è¿ä¾ï¼è¯¦è§æ¤å¤ï¼

- æå°å¨æè¿ä¾ï¼æ¬æ详解ä¹éç¹ï¼ã

- æ大å¨æè¿ä¾

- ä½èå²å®½åº¦è¿ä¾

- é«èå²å®½åº¦è¿ä¾

å¦éäºè§£èå²å®½åº¦è¿ä¾ç详æ ï¼è¯·åé âæ¥åæ¶åºæ±æ»â(Report Timing Summary) çâTPWSâé¨åã

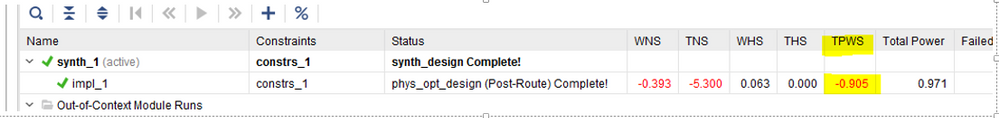

æ严éçèå²å®½åº¦è¿ä¾å¨æ¥åä¸æ¾ç¤ºä¸º WPWSã

å¦éäºè§£èå²å®½åº¦è¿ä¾ç详æ ï¼è¯·å¨ Vivado GUI ä¸æå¼èå²å®½åº¦è¿ä¾æ¥åï¼åå»âReportsâ - > âTimingâ - > âReport Pulse Widthâï¼æ使ç¨ä»¥ä¸ Tcl å½ä»¤æå¼æ¤æ¥åï¼

report_pulse_width

æå°å¨æè¿ä¾

æ¬æä» ä»ç»âæå°å¨æè¿ä¾âç¸å ³å 容ã

æ¥åæè¿°ï¼

å¨èå²å®½åº¦æ¥åä¸ï¼å°æ£æ¥æææ¶éçæå°èå²å®½åº¦è¦æ±ã

æå°å¨æè¿ä¾ç¤ºä¾ï¼

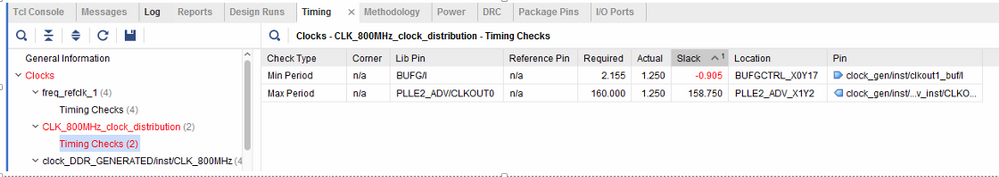

举ä¾æ¥è¯´ï¼GUI ä¸æå¼çæ¥åæè¿°å¦ä¸æ示ï¼

以ä¸ç¤ºä¾æ¾ç¤ºäºç¹å®æ¶éçæå°å¨æ (Min Period) åæ大å¨æ (Max Period) è¦æ±ã

å¯ä»¥çå°ï¼é对âMin Periodâï¼è£é (Slack) 为è´å¼ã

æ¤è¿ä¾ç°è±¡å¿

须解å³ï¼æè½é¿å

åºç°èå²å®½åº¦è¿ä¾ã

å¨æ¤ç¤ºä¾ä¸ï¼æ¾ç¤ºçé¢æå¼ (Required) 为 2.155nsï¼å®é å¼ (Actual) 为 1.250nsï¼è¿ä¸¤ä¸ªå¼å为对åºäºæ£æ¥ç±»å (Min Period) çå¼ãâSlackâåæ¾ç¤ºçå¼å³ä¸ºè¿ä¸¤è çå·®å¼ï¼Slack = Actual å¼ - Required å¼ï¼ã

解å³åæ³ï¼

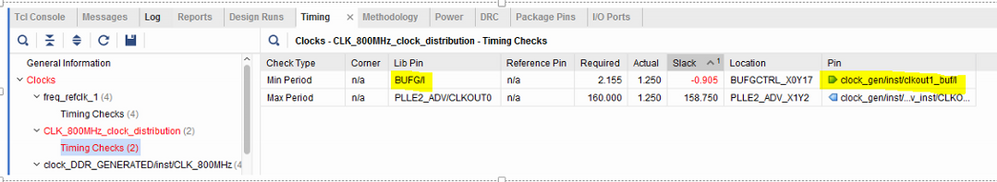

å¨æ¤ç¤ºä¾ä¸ï¼è´ Slack å¼ -0.905ns ä½äº BUFG çè¾å

¥å¼è (Lib Pin: BUFG/I) ä¸ã

è¦è§£å³æ¤è¿ä¾ï¼å¿

é¡»æ£æ¥æ¤ç¹å®å¨ä»¶ç³»åç AC å DC ç¹æ§ï¼å

¶ä¸å°æ¾ç¤º BUFG å

许çæ大é¢çã

ç±äºè¿æ¯ç¡

çå±é¢çéå¶ï¼æ¨å°éè¦è°ä½é¢çæè½è§£å³æ¤è¿ä¾ã

æ¥æºï¼èµçµæ论å