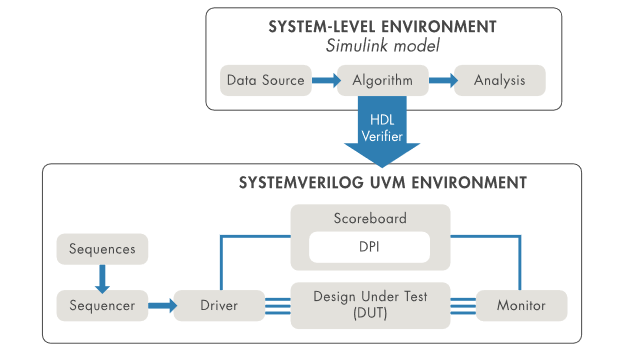

从现已上市的 Release 2019b 开始,HDL Verifier 开始提供对 Universal Verification Methodology (UVM) 的支持。HDL Verifier 能够让开发 FPGA 和 ASIC 设计的设计验证工程师直接从 Simulink 模型生成 UVM 组件和测试平台,并在支持 UVM 的仿真器(比如来自 Synopsys、Cadence 和 Mentor 的仿真器)中使用这些组件和测试平台。

Wilson Research Group 的一项最近研究发现,48% 的 FPGA 设计项目和 71% 的 ASIC 设计项目依赖 UVM 进行设计验证。通常,算法开发人员和系统架构师在 MATLAB 和 Simulink 中开发新算法内容。然后,设计验证 (DV) 工程师在为 RTL 测试平台手工编写代码时使用 MATLAB 和 Simulink 模型作为参考,这一过程极其耗时。现在借助 HDL Verifier,DV 工程师可以从已经在 Simulink 中开发的系统级模型自动生成 UVM 组件,如序列或记分板。在为诸如无线通信、嵌入式视觉和控制等应用中使用的 ASIC 和 FPGA 设计而开发测试平台时,此方法可以减少验证工程师所花费的时间。

“借助 Simulink,我们在手工编写生产 UVM 测试平台、测试序列和记分板上花费的时间可以减少大约50%,从而有更多时间专注于突破性创新应用。”Allegro MicroSystems 的 ASIC开发经理 Khalid Chishti 说,“我们针对汽车应用设计的 ASIC 依赖 UVM进行生产验证,为这些设备开发算法曾是一项繁琐的任务,而 MATLAB 和Simulink 对此进行了简化。”

HDL Verifier 增添了一些新功能,例如,从 MATLAB 和 Simulink 中生成 UVM 组件、SystemVerilog 断言和 SystemVerilog DPI 组件,现在可向负责 ASIC 和 FPGA 生产验证的设计验证团队提供更多扩展性支持。这些设计验证团队原本通过在 SystemVerilog 中手工编写代码,进而在 HDL 仿真器中开发严格测试平台,现在,他们能够从现有 MATLAB和 Simulink 模型直接生成验证组件,并重用这些模型加快创建生产验证环境的速度。

图示:HDLVerifier 根据 Simulink 模型生成UVM组件 ©MathWorks

“根据 Wilson Research 和 Mentor Graphics 的 2018 年功能验证研究,DV 工程师在开发测试平台中花费在 ASIC 和 FPGA 项目上的时间,大约占他们工作时间的五分之一。”MathWorks 首席 HDL 产品营销经理 Eric Cigan 说,“HDL Verifier 能够从现有 MATLAB 和 Simulink 模型生成 UVM 和 SystemVerilog DPI 组件,不仅可以提高 DV 工程师的生产效率,而且会增进系统架构师、硬件设计师与 DV 工程师之间的合作。”

HDL Verifier R2019b 现已在全球上市。点击了解产品更多信息:https://ww2.mathworks.cn/products/hdl-verifier.html