8月3日-12日,赛灵思软件与 AI 专家团特举办四期系列线上公开课,深入探讨如何在调整部署平台架构,满足应用不断增长的挑战与其独特需求的同时,一如既往地使用 TensorFlow 和 Caffe 等高层次框架,采用 C、C++ 和 Python 等熟悉的编程语言进行开发。

参加本次 Vitis™ 和 Vitis AI 开发环境系列公开课,您将可以深入了解基于赛灵思技术的人工智能推断解决方案、开源性能优化库、综合开发工具和设计方法。

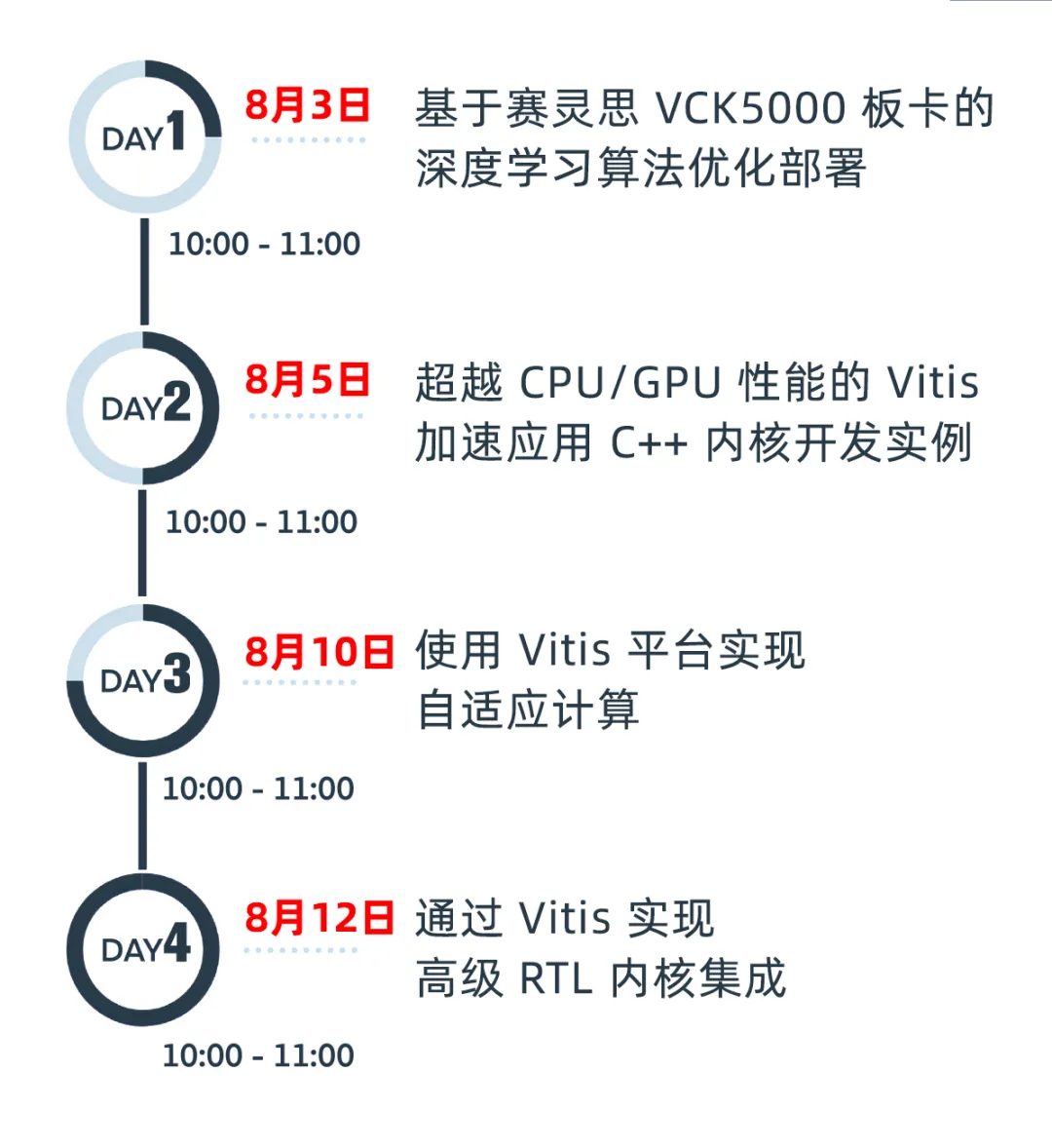

课程为期四天,请预留您的日程安排哦

课程详情

8月3日 10:00 - 11:00

基于赛灵思 VCK5000 板卡的深度学习算法优化部署

通过介绍 VCK5000 平台上的 CNN、NLP 等不同 AI 硬件架构以及现场演示,帮助用户更快速地了解如何在 VCK5000 平台上进行算法部署。

张帆,软件与 AI 技术市场部资深工程师

现任赛灵思软件与人工智能(AI)技术市场部资深工程师,负责赛灵思AI解决方案在全球不同细分市场的创新和推广。

8月5日 10:00 - 11:00

超越 CPU 及 GPU 性能的Vitis加速应用 C++ 内核开发实例

设计 C++ 内核的简单程度超乎您的想象……本次研讨会不仅将讨论 C++ 内核的一些关键优化手段,还将展示如何充分利用 FPGA 固有并行性的优势。我们会通过实现一个 NP 算法模型将Xilinx FPGA的性能与 CPU 和 GPU 进行比较。

李昀,软件与 AI 加速技术市场专家

2004年加入赛灵思,拥有超过十年的 FPGA 设计、工具、HLS和客户支持经验。李昀毕业于北京理工大学,拥有信号与信息处理专业博士学位。

8月10日 10:00 - 11:00

使用 Vitis 平台实现自适应计算

Vitis 的平台方法论可以帮助加速算法应用适配到不同硬件,也可以让硬件平台支持多种算法应用。加入我们,了解为什么 Vitis 平台可以帮助你加快设计速度,以及怎样设计的的平台。

苏同麒,软件与 AI 加速技术市场专家

2006 年加入赛灵思,拥有超过十年的 FPGA 设计、工具、嵌入式系统架构和客户支持经验;毕业于同济大学,获得电子科学学士学位。

8月12日 10:00 - 11:00

通过 Vitis 实现高级 RTL 内核集成

作为一种重要的硬件设计方法,RTL设计流程在Vitis中继续得到了增强。通过一个简单明了的流程,你可以用Vitis轻松有效地移植你现有的RTL设计或开始新的RTL设计。本节内容将通过一些设计实例,展示使用Vitis来完成一些基本的RTL内核设计和集成流程。

原钢,资深 AI 技术市场专家

在集成电路研发及设计服务领域拥有多年经验,2017年加入深鉴科技,2018年加入赛灵思,负责赛灵思人工智能相关方案的市场推广以及技术支持工作。

报名渠道现已开放,点击预约课程吧:https://app.ma.scrmtech.com/meetings-api/sapIndex/SapSourceData?pf_uid=1...