作者:David Brubaker,赛灵思高级产品线经理

随着 5G 基础设施和实现设备不断进入实际部署,5G 已从概念变为现实;很显然,5G 经济不会只是3G 或 4G 的复制品。

新的挑战需要灵活应变的解决方案,既要能够处理多样化的需求,同时也要能够随市场需求的变化而持续演进发展。Zynq® UltraScale+™ RFSoC DFE因其架构上集成了比传统软逻辑更多的硬化 IP 逻辑, 使得其在保持赛灵思一贯的灵活应变价值的同时,还能媲美定制 ASIC 在成本和功耗上的竞争力,因此能轻松应对这些挑战。

5G 面临的前沿挑战

日益提高的无线电性能和复杂性

无线电单元 (RU) 对更大带宽的需求,不仅是为了增加数据速率。运营商还需要为现有和新的频段解决复杂的无线电配置问题。为满足这些需求,无线电应从设计上支持尽可能宽的瞬时带宽 (iBW)。例如,早期 5G 无线电支持高达 200MHz 的带宽,但未来的无线电需要支持高达 400MHz。

尽管 5G 现已成为默认的无线标准,但 4G 出货仍将以大批量延续多年。在升级或安装 5G 网络时,运营商必须提供 4G 覆盖。因为信号塔空间是按单元和重量租用的,同时支持 4G 和 5G 的多模 RU 有助于降低资本支出和运营成本。

5G 无线电的另一个复杂之处是分布式单元 (DU) 接口。典型划分是 7.1、7.2 和 7.3;RU 必须给予全面支持。

5G 多样化用例及不断演进发展的标准

3G 主要围绕语音和短信;运营商的盈利模式是出售以分钟计算的通话时间和短信数量。4G 有一个用例,那就是移动数据,它促成了智能手机的兴起,运营商由此开始按月出售按 GB 计算的数据。

5G 则如图 1 所示,拥有三种主要用例:增强型移动宽带 (eMBB)、超高可靠低时延通信 (URLLC) 和大规模机器类通信 (mMTC)。如果单独优化每一个用例,则会导致各种无线电解决方案大相径庭;而 5G 将它们融合成统一的标准。

图 1:5G 用例

今天的 5G 全部围绕 eMBB。运营商争相部署 5G,以吸引客户使用速度最快的网络。

因为 URLLC 和 mMTC 属于新用例,还没有发达市场或发达经济体实施它们。URLLC 宣传的主要应用是自动驾驶,但 5G 网络不会在该领域发挥重要作用。这个过程要求实时运行。一种可行的 URLLC 用例是将车辆或机器设备运行在采矿和救灾等对人为操作而言过于危险的环境中。

mMTC 用例适用于每平方公里存在上百万个互联设备的情况。对于智能家居设备,WiFi 工作表现良好,5G 不会取代。mMTC 用例对于工业、商业和政务应用(例如智能工厂、智能城市)来说将更加重要。

不断演进发展的标准

随着 2009 第 9 版的发布,4G LTE 标准最终确定,并在随后的 8 年里,通过 5 个 3GPP 版本的推出不断演进,直至演进到 4G LTE Advanced。

5G 的第一阶段和第二阶段在第 15 版和第 16 版中完成定义,覆盖了基础 eMBB、mMTC 和 URLLC。第 17 版的制定工作已经启动,第 18 版也已经进入规划。5G 标准将在今后十年里随市场需求而演进发展。

5G 市场突变

我们可以将 5G 面临的又一大挑战广义地称作市场突变。回顾 4G 市场,可见其相当僵化。4G 只有一个用例,且市场由传统运营商构成,他们向消费者销售数据,并从传统硬件 OEM 厂商那里购买网络基础设施。

如今,O-RAN 联盟和电信基础设施项目都在通过实现供应商多元化,颠覆既有的商业模式。颠覆性 5G 运营商,如 Dish、Rakuten 和 RJIO 正在向他们的同行和既有运营商发起挑战。

在使用 mMTC 和 URLLC 功能提供完整的企业级解决方案的专用网络中,将会发生颠覆和真正的创新。

图 2:5G 将助力实现专用网络中的创新

结果是实现了有新运营商和新供应商参与其中且富有活力的 5G 经济,如图 3 所示。

图 3:5G:新的商业模式、市场和竞争

Zynq RFSoC DFE 助力满足当前和未来的 5G 需求

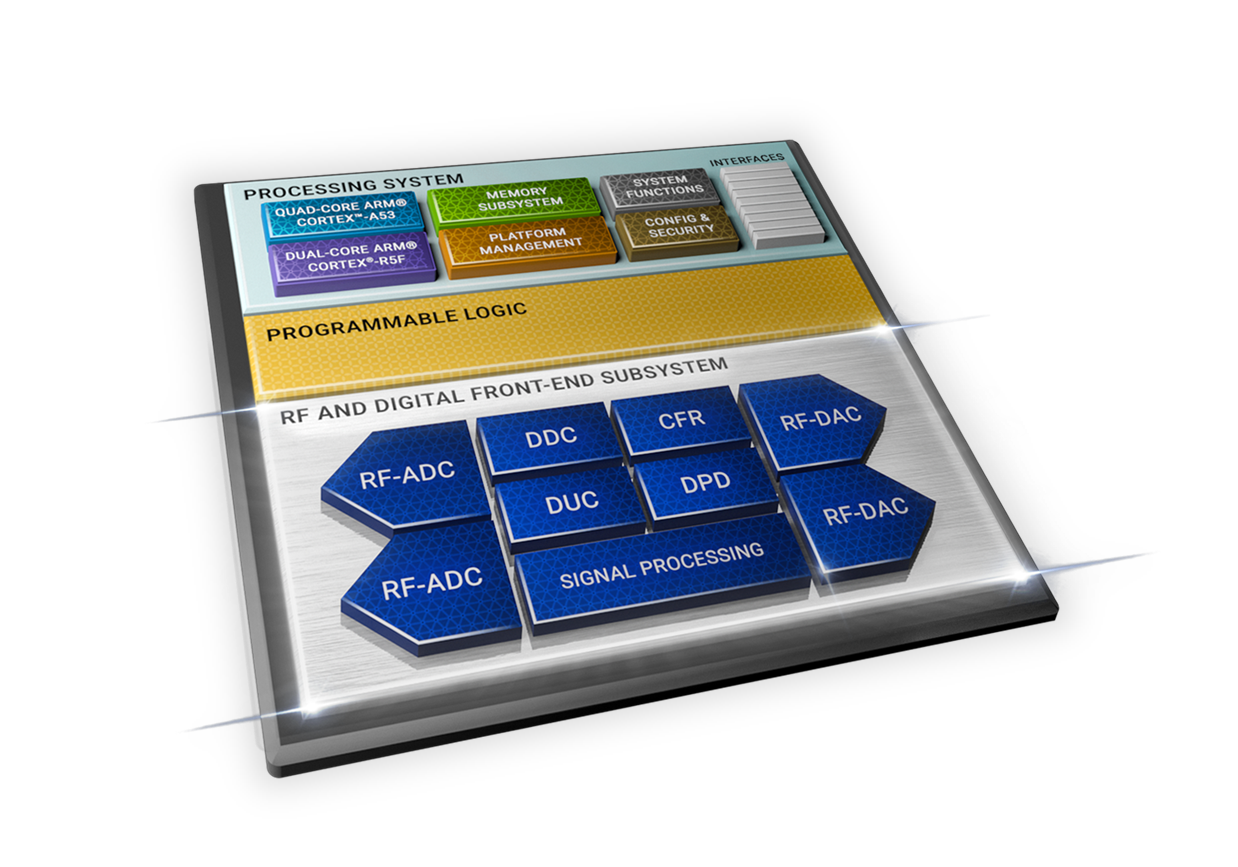

Zynq RFSoC DFE 在硬化的或类 ASIC 的结构上实现了已知的计算密集型 DFE 功能。这些结构经过配置,能同时用于 4G 和 5G 新无线电 (NR) 标准。

图 4:Zynq RFSoC DFE 集成了带有硬化 IP 的完整 DFE 子系统

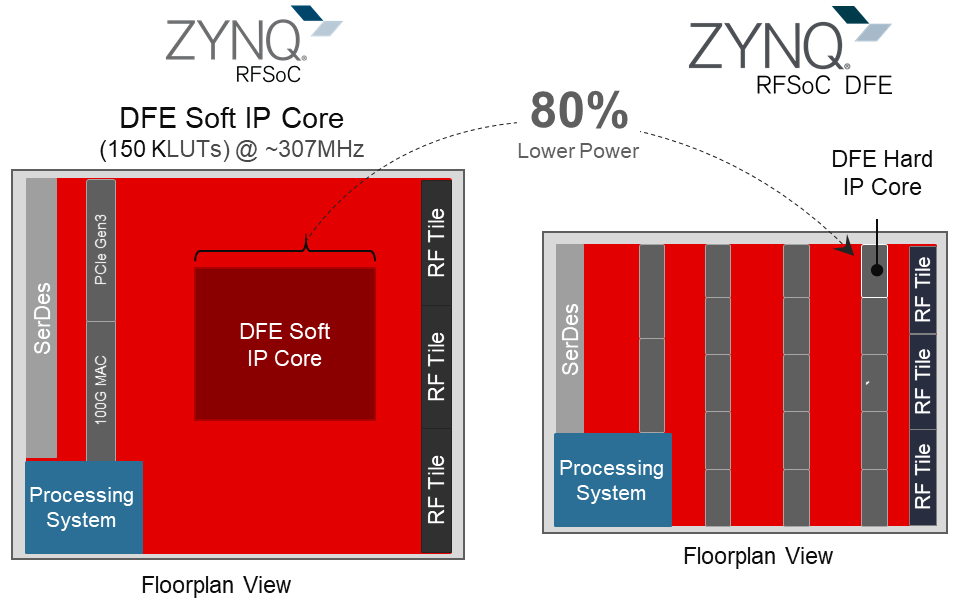

这些硬化单元占用的芯片面积减小,与图 5 所示的传统 FPGA 软逻辑相比,能节省功耗高达 80%。因为每个硬化的 IP 核在物理尺寸上都小于软逻辑,与 Zynq UltraScale+ RFSoC Gen 3 器件相比,增加核心就能提供 2 倍 DFE 处理能力。

图 5:硬化 IP 实现方案的优势

在充分利用 DFE 硬化 IP 块的情况下,Zynq RFSoC DFE 的功耗比实现在 第三代Zynq RFSoC 器件上的等效实现方案低 50% 左右。

如图 6 所示,硬化 IP 块以与数据流保持一致的方式,按规律布局在 Zynq RFSoC DFE 上。每个 IP 功能都由多个实例组成,支持器件根据应用来缩放。为提供最大的灵活性,用户能在数据路径上的任何点绕过任意块和添加逻辑。

图 6:Zynq RFSoC DFE 功能原理图

Zynq RFSoC DFE 支持 FR1(高达7.125GHz)下 iBW 最大 400MHz 的多频段、多模式无线电。在用作 FR2 的 IF 收发器时,支持最大 1600MHz 的 iBW。

总之,赛灵思 Zynq UltraScale+ RFSoC DFE 延续了 Zynq UltraScale+ RFSoC 的成功基础,将所有关键的计算密集型数字处理块包含在符合标准的硬化配置内,同时为未知的未来需求和市场需求内置自适应逻辑,既提供了可媲美 ASIC 的优势,又保持了赛灵思一贯以来的灵活应变能力和市场投放速度。