描述

该设计咨询涵盖如下 UltraScale+ GTH/GTY 收发器问题,即 GTPOWERGOOD 在上电后可能无法断言有效。

所有 UltraScale+ GTH/GTY 收发器中均包含 *_delay_powergood.v 模块。

GTH/GTY 设计的部分构建中来自 *_delay_powergood.v 模块的 GTPOWERGOOD 可能保持处于低电平,而同时 FPGA 电源轨正常且 GT 原语输出 GTPOWERGOOD 断言有效。

此故障的症状是 GT Wizard IP 未脱离复位状态(例如,复位未完成和/或 PLL 未处于锁定状态,即使跨复位周期/电源重启也是如此)。

解决方案

在 UltraScale Transceiver Wizard IP 的 Vivado 2019.2 版本中,*_delay_powergood.v 模块已更新。

对于面向 Vivado 2017.2 和 2019.1.3 之间版本的 UltraScale+ GTH/GTY 设计:

如果在 *_wait_cnt_reg* 路径上报告了保持时间违例,请应用经过修改的 *_delay_powergood 模块或策略补丁。

如无保持时间违例,则无需重新生成 Wizard IP。

要应用策略补丁,请执行以下操作

本答复记录随附了策略补丁文件。请使用适用于设计对应的 Vivado 版本的补丁文件。

补丁安装:

请按照随附 README.txt 文件中的说明安装补丁,以便解决该问题。

用户应根据 README 自述文件检查补丁版本,以便确保更新至最新补丁版本。

要检查现有设计的时序,请执行以下操作:

1) 打开工程或已布线的 DCP。

2) 使用以下 Tcl 命令将约束写出至文件:

write_xdc -exclude_physical all_constraints.xdc

3) 编辑生成的 all_constraints.xdc 并注释掉关联的 delay_powergood set_case_analysis 和 set_false_path 约束:

##set_false_path -through [get_pins -filter {REF_PIN_NAME=~*Q} -of_objects [get_cells -hierarchical -filter {NAME =~ *gen_pwrgood_delay_inst[*].delay_powergood_inst/gen_powergood_delay.pwr_on_fsm*}\\]] -quiet

##set_case_analysis 1 [get_pins -filter {REF_PIN_NAME=~*Q} -of_objects [get_cells -hierarchical -filter {NAME =~ *gen_pwrgood_delay_inst[*].delay_powergood_inst/gen_powergood_delay.pwr_on_fsm*}\\]] -quiet注:以上粗体 * 因通道数而异(例如,1、2 等)。

4) 使用以下 Tcl 命令复位时序并应用经过修改的 XDC:

reset_timing

read_xdc all_constraints.xdc

5) 使用 Report Timing Summary 运行时序检查。

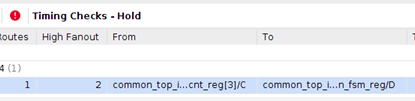

6) 检查在 *_wait_cnt_reg* 路径中是否有任何保持时间违例报告,例如:

7) 如果在 *_wait_cnt_reg* 路径上报告了保持时间违例,请应用经过修改的 *_delay_powergood 模块或策略补丁。

注: