本文转载自: XILINX开发者社区微信公众号

本篇博文来自赛灵思高级产品应用工程师 Hemang Divyakant Parikh

什么是方法论报告?

“方法论 (Methodology)” 报告是 Vivado 工具中的一项功能,它使用 UltraFast 设计方法论 (UFDM) 以及 Versal ACAP 设计方法论来帮助精简设计进程和提升 QoR。

方法论分析是一种特殊形式的设计规则检查,专用于检查是否符合设计方法论,并识别进程中出现的常见错误。只有在遵循 UFDM 准则进行操作的前提下,该工具的算法才能发挥最优作用。如不遵循这些准则,方法论报告就会发出标记。不解决违规行为可能导致工具 QoR 结果极差。

方法论分析遵循一组具体规则,这些规则用于指定在运行 Report Methodology 命令期间执行的各种方法论检查。

注:下列每个阶段后都需要运行方法论报告:synth_design、opt_design 和 place_design,执行 route_design 后则必须运行此报告,这样有助于您理清头绪,并在设计验收之前妥善解决设计问题。

此报告将返回有关下列对象的严重警告 (critical warning) 和警告 (warning):

严重的方法论警告 (CW) 将指出功能问题或 QoR 问题。如不审查这些警告并解决实际问题,那么对后续出现的问题进行调试就可能极为耗时,有时需要几天甚至几周时间。

打开方法论报告时,您可能会看到设计存在成百上千条警告和严重警告。您无需对此高数值过于担忧。如果您确定这些警告或严重警告在当前时间点并未导致任何问题,则可对这些警告或严重警告使用豁免 (waive)。请参阅 (UG906) 以获取有关如何通过 GUI 或 Tcl 创建豁免的更多信息。

注:如果您在报告中看到 ID 为 TIMING-6、7、14、24 或 35 的警告,请优先审查这些警告,并将其解决,以避免在设计周期的最后阶段出现其他问题。

包含下列博文:

本篇博文系主博文,下含另 6 篇博文用于演示方法论报告如何帮助提升设计 QoR 并为您节省问题根源调试时间。

下属博文都是根据客户真实问题编撰的,其中演示了调试每一种问题的传统方法,并以对比方式来显示方法论报告如何利用其严重警告和警告来帮助解决这些问题。

1. 时序已满足,但硬件功能出现错误

2. 方法违例对于 QoR 的影响

3. 时序已满足,但硬件中存在 DDR4 校准失败

4. 罕见的比特翻转

本篇博文中的分析是根据真实客户问题撰写的,该客户发现在现场出现罕见的比特翻转。本篇博文演示了用于缩小根本原因范围以及修复此问题的部分调试技巧。

5. DDR4 IP 校准后硬件故障,指示存在时序问题,但时序报告中无任何违例

6. 设计无法连贯布线

本篇博文中的分析是根据真实客户问题撰写的,该客户的 DFX 设计无法连贯布线,存在布线重叠。本篇博文演示了用于缩小根本原因范围以及修复此问题的部分调试技巧。

方法论报告如何帮助您完善设计

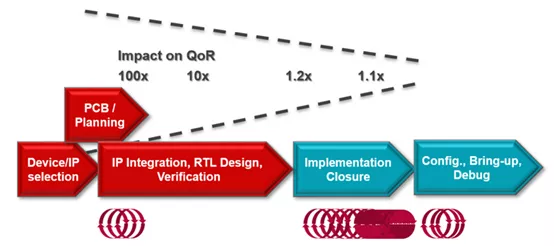

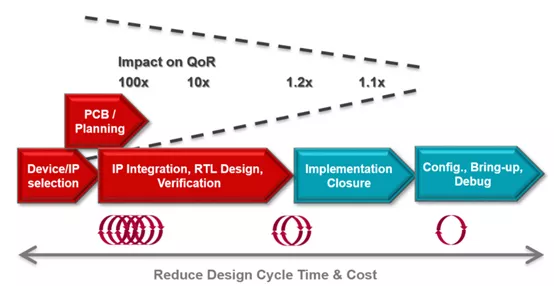

遵循此方法论报告进行操作将有助于您显著缩短设计周期时间并降低成本。以下图形表示法显示的是在设计周期上遵循 UFDM 和不遵循 UFDM 各自的影响:

图 1:不遵循正确的 UFDM 方法情况下的成本、调试时间和设计周期时间

图 2:遵循正确的 UFDM 方法情况下的成本、调试时间和设计周期时间

注:此报告不含干扰信息或杂项信息。阅读此报告并理解每一项违例至关重要。其重要性不亚于设计验收时的“时序汇总 (Timing Summary)”报告和 DRC 报告。在后续 Vivado 版本中,我们计划向用户普及方法论报告,提升其用户友好度。

实用链接

以下提供了一些实用链接,以帮助用户进一步了解 UltraFast 设计方法技巧和方法论报告:

UG949 - https://china.xilinx.com/support/documentation/sw_manuals/xilinx2021_1/c...

UG906 附录 A -

https://china.xilinx.com/support/documentation/sw_manuals/xilinx2021_1/c...

UG835 - https://china.xilinx.com/support/documentation/sw_manuals/xilinx2020_1/u...

UG1292 - https://china.xilinx.com/support/documentation/sw_manuals/xilinx2021_1/c...

UltraFast 设计方法视频 -

https://www.youtube.com/watch?v=U_16tKynK7Y&list=PL35626FEF3D5CB8F2

UltraFast 设计方法 QuickTake 视频 -

https://www.xilinx.com/video/hardware/ultrafast-design-methodology-for-v...