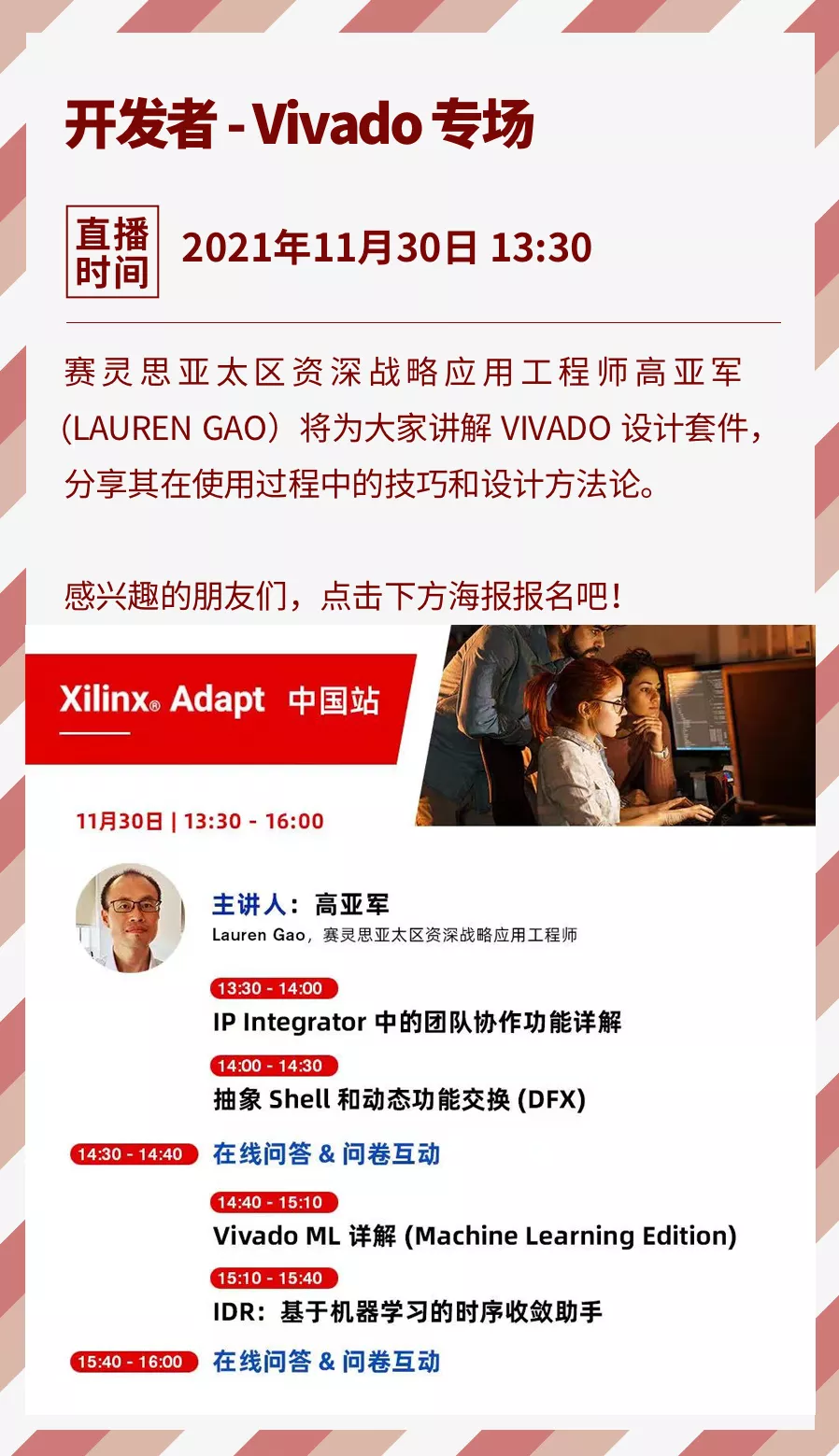

IP Integrator中的团队协作功能详解

随着赛灵思芯片产品复杂性的增加,使用这些高级功能的设计也随之变得更加复杂,更多的团队成员需要参与到设计过程中。IP Integrator 使设计团队能够通过 Block Design Container 等功能,提高生产力和可重用性。

本场演讲将深入探讨这些功能,并详解它们为设计开发团队带来的便利。

抽象Shell和动态功能交换(DFX)

抽象 Shell 技术在标准 DFX 流之上工作,并提供许多好处。本场演讲将围绕抽象 shell 技术进行阐述,讲解其如何通过启用每个可重新配置分区的并行编译,显着缩短 FPGA 设计编译时间、减少 Vivado 的内存占用;如何绕过静态区域中包含的 IP 的许可证检查,以及如何提高多用户环境中的设计安全性。

Vivado ML 版本详解

从减少设计迭代、降低设计复杂性,到实现资源的自适应和高效使用,Vivado® ML 版本实现了重大飞跃。本场演讲中,您将了解到 Vivado ML 的机器学习算法如何助力改善编译时间和结果质量( QoR )。

IDR:基于机器学习的时序收敛助手

IDR( Intelligent Design Runs )是新的主动时序收敛功能。它能利用许多复杂的时序收敛部件并将其打包在一起,以创建简单的“按键式”解决方案。

在本场演讲中,我们将向您详细介绍哪些设计最适合使用此功能、如何访问并使用 IDR,以及它如何在底层工作。