立即获得无需设计的动态性能增益

为EV12AQ600/5提供即时、无需设计的动态性能增强

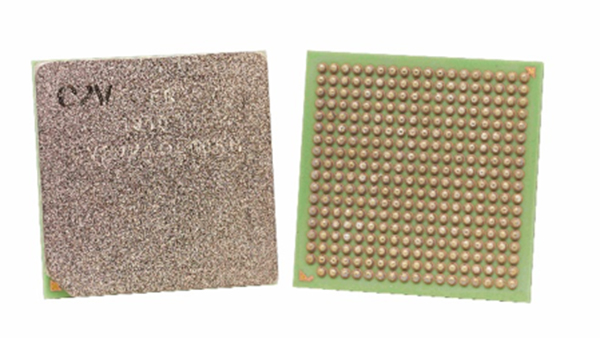

Teledyne e2v今天宣布即将推出具有集成的许可证密钥的EV12AQ600/5选项,可直接使用Teledyne集团公司旗下SP Devices开发的新型ADX4后处理算法。ADX4杂散抑制IP可动态抑制由四个ADC内核之间的增益、偏移和相位不匹配导致的杂散频率分量。时间交错是提高ADC采样率的可靠的架构方法。然而,在10位分辨率以上和宽带应用中,通过校准避免产生频谱失真非常具有挑战性。

对于EV12AQ600/5,四个核心的时间交错将采样率从1.6提高到6.4 GS/s。ADC核心之间的不匹配误差降低了无杂散性能。ADX4可提供高达10 dB的无杂散动态范围(SFDR)提升。这种提升在宽带应用中尤其明显,因为它不需要硬件设计的更改。用户可方便地将ADX4代码模块烧写进后处理FPGA中,甚至可以在工作现场进行。

关于ADC时间交错

高分辨率数据转换器正在快速发展,以获取更宽的瞬时带宽。实现更高采样率的一种理论上简单的方法是对现有内核应用时间交错。多个ADC核心在公共采样时钟的不同相位上进行时钟控制,从而允许获取更高密度的信号采样。这种增加的采样密度提供了一种有用的性能扩展,并且可以很好地使用高达8位的分辨率。通过标准的混合信号校准和电路布局方案,跨内核匹配相对更容易管理。

对于10位及以上的分辨率,尤其是在千兆赫兹范围内工作,则越来越难以确保匹配。因此,会出现采样伪影,导致失真并限制测量的动态性能。这些高频不匹配误差在模拟设计领域很难缓解。因此,对于6.4 GS/s时间交错ADC,要在3 GHz输入信号下实现72 dB SNR(理论最大12位),需要优于12 fs的跨核相位匹配。

值得庆幸的是,在过去的二十年里,DSP资源的成本已经显著下降,如今采用算法方法来减少杂散在经济上是可行的。Teledyne SP Devices专门设计和制造高分辨率超高速数字化仪,几十年来积累了有关先进分立转换器的丰富经验,并精通这方面的相关技术。

与单点或多点校准不同,ADX4数字误差校正可以在误差随频率变化时提供杂散抑制,使得不需要的混叠杂散被抑制到噪声本底中。

实现ADX4

获得ADX4动态增强非常容易。通过所需的供应链,客户只需将订单转移到EV12AQ600/5器件的-ADX4选项。此外,他们需要将ADX4模块添加到Xilinx FPGA代码负载中。这样就大功告成了。

ADX4供应

以下组件列表显示了当前随ADX4许可证密钥提供的EV12AQ600/5选项。考虑双通道模式工作的客户可直接联系Teledyne e2v,咨询ADX2许可证密钥选项的未来供应情况。

有用的链接

Teledyne e2v EV12AQ600/5-ADX4数据手册

视频链接:了解时间交错的EV12AQ600 ADC不匹配误差修正

关于Teledyne e2v

Teledyne e2v公司的技术创新引领着医疗健康、生命科学、太空、运输、国防安全及工业市场的发展。Teledyne e2v以独一无二的方式保持领军地位,包括密切关注客户在市场和应用领域面临的挑战。通过与客户密切合作,提供创新标准以及半定制和全定制的解决方案,提高客户系统的价值。

关于Teledyne SP Devices

Teledyne SP Devices设计和制造世界领先的模块化数据采集和信号生成仪器。公司产品采用享有专利的校准逻辑、最新数据转换器和最先进的FPGA技术,实现了高采样率和分辨率的无与伦比的组合。产品具有一系列特定应用功能和嵌入式实时信号处理功能。这有助于客户克服性能瓶颈,缩短产品上市时间,并在广泛的应用领域提供系统级优势。SP Devices的产品广泛应用于各个行业,包括分析仪器、遥感、科学仪器、医学成像等。有关更多信息,请访问SP Devices官方网站: www.spdevices.com.