本文转载自: 米联客微信公众号

软件版本:vitis2021.1(vivado2021.1)

操作系统:WIN10 64bit

硬件平台:适用XILINX A7/K7/Z7/ZU/KU系列FPGA

1.1概述

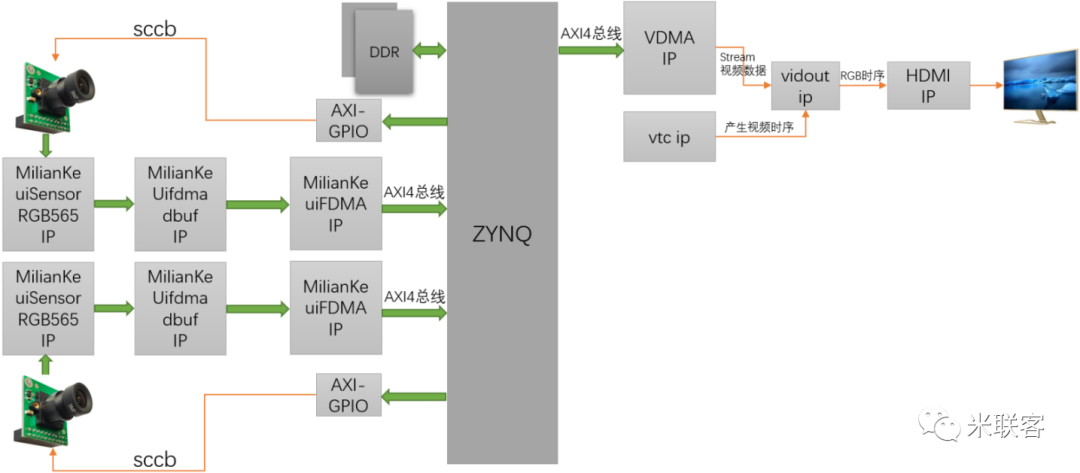

米联客uifdma是基于AXI4总线接口开发的一种DMA数据管理IP,该IP可以统一视频数据、普通ADC数据、PLDDR接口和PSDDR接口,具有更加广泛的通用性。并且该IP是米联客对所有开发者开源的。

本文实验目的:

1. 掌握ui-fdma和ui_fdmadbuf在视频采集方案的应用

2. 掌握多个AXI-FDMA同时传输视频的同步解决方法

3. 掌握uifdma_dbuf视频格式中Stride参数的使用

4. 掌握uifdma_dbuf和VDMA之间如何进行帧同步,如何实现3帧图形缓存,确保图形不撕裂。

1.2系统框图

1.3搭建SOC系统工程

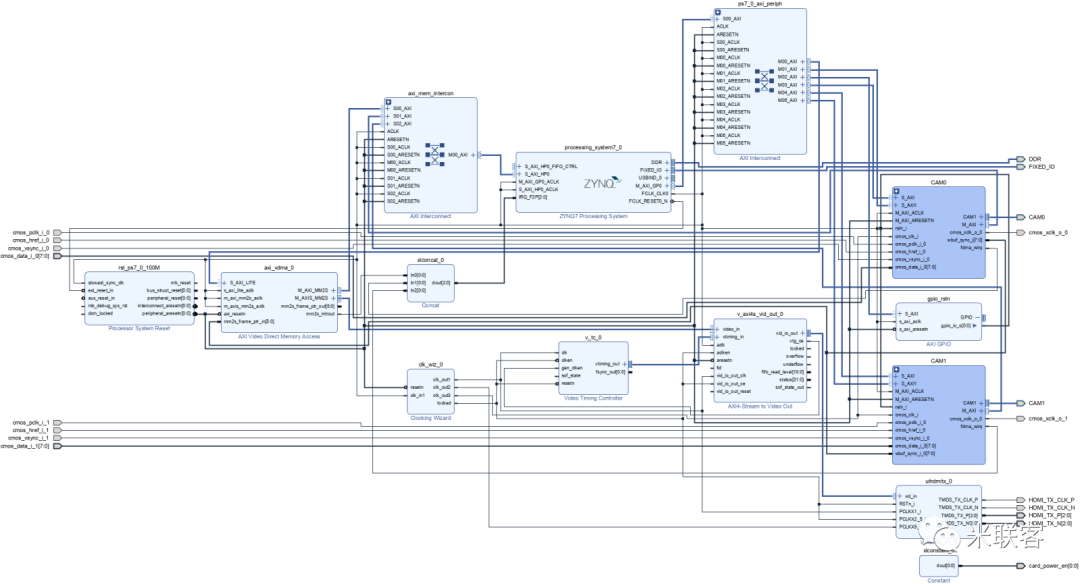

1.3.1PL图形化编程

系统输出部分的搭建请,阅读“米联客2022版ZynqSocSDK高级篇”一文中“5.4搭建SOC系统工程”这一章节,本文增加VDMA输入部分。下面给出完成的工程,并且就新增加的输入部分加以介绍。

上图中高亮部是FDMA的帧同步计数器,CAM0的帧同步计数器提供给CAM1和VDMA 输出 IP使用。VDMA 输出 IP工作于SLAVE circle 模式,所以CAM1和VDMA 输出都是从模式同步受控于CAM0的帧计数器,这样可以确保视频不出现撕裂。

1:CAM0中FDMA IP设置

关键设置:

1`WBaseaddr 0x08000000 设置缓存的起始地址

2`WDsizebits 设置缓存的大小,2^23次方代表8MB大小

3`WBufsize 设置图像采用三缓存

4`WXsize设置行像素640

5`WXStride设置行Stride参数为1280,改参数用于2个视频在一个显存中显示

6`WYsize设置场像素为480

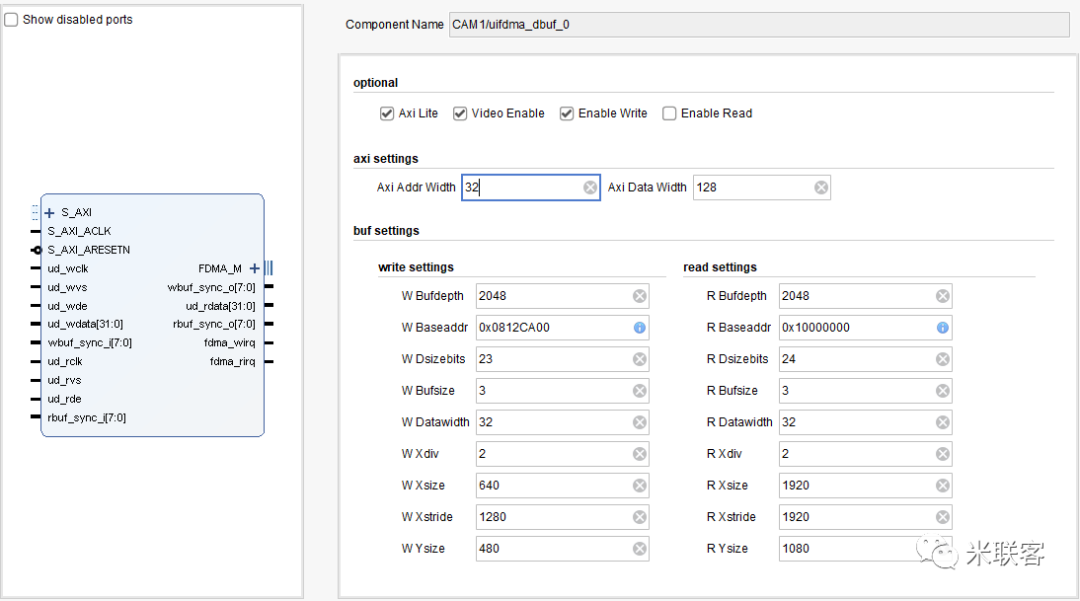

2:CAM1中FDMA IP设置

1`WBaseaddr 0x0812CA00 设置缓存的起始地址,通过设置该地址可以让图像在指定的偏移位置显示

2`WDsizebits 设置缓存的大小,2^23次方代表8MB大小

3`WBufsize 设置图像采用三缓存

4`WXsize设置行像素640

5`WXStride设置行Stride参数为1280,改参数用于2个视频在一个显存中显示

6`WYsize设置场像素为480

4:多路视频同屏显示原理

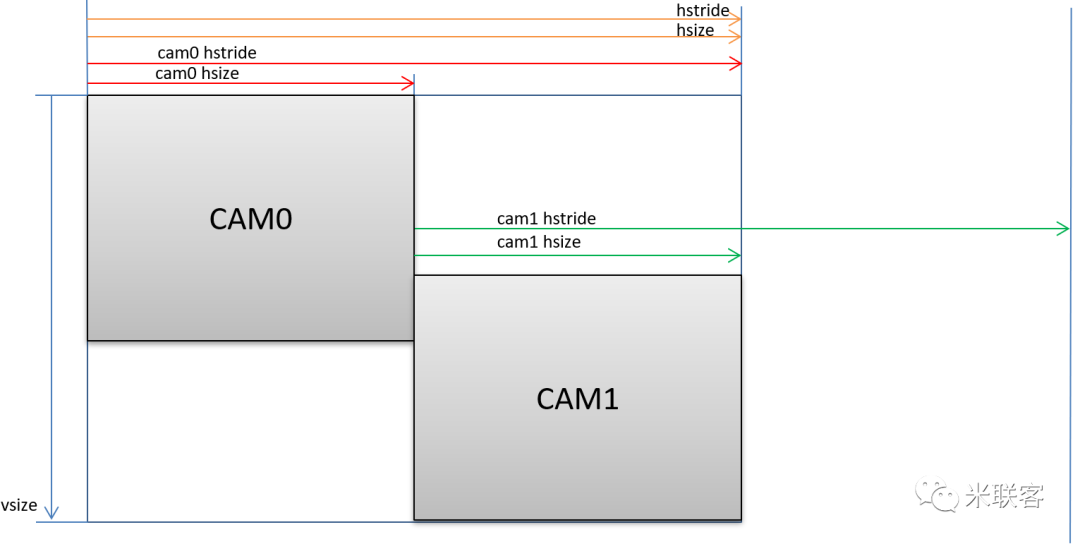

为了把2个图像显示到1个显示器,首先得搞清楚以下关系:

hsize:每1行图像实际在内存中占用的有效空间,以32bit表示一个像素的时候占用内存大小为hsize*4

hstride:用于设置每行图像第一个像素的地址,以32bit 表示一个像素的时候h_cnt* hstride*4

vsize:有效的行

因此很容易得出cam0的每行第一个像素的地址也是h_cnt* hstride*4

同理如果我们需要把cam1在hsize和vsize空间的任何位置显示,我们只要关心cam1每一行图像第一个像素的地址,可以用以下公式h_cnt* hstride*4+offset

比如我们这里背景输出到显示器的分辨率为1280*720,cam1的分辨率是640*480需要移动上图的右下脚,offset=(1280-640)*4*(720-480)

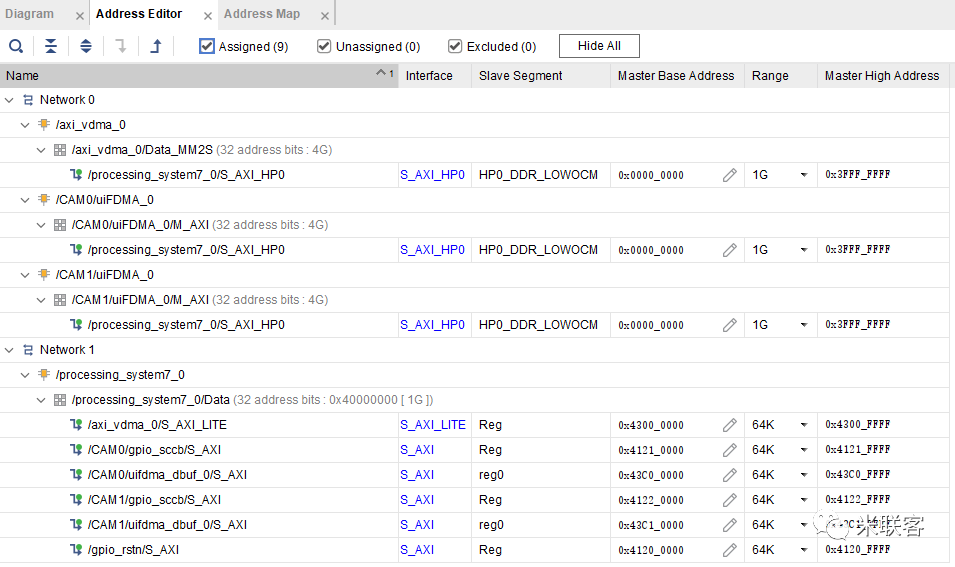

1.3.2设置地址分配

以sccb方式初始化摄像头的地址空间截图

1.4搭建Vitis-sdk工程

创建soc_base sdk platform和APP工程的过程不再重复,如果不清楚请参考“米联客2022版ZynqSocSDK入门篇”中第一个工程 “01Vitis Soc开发入门”这个实验。

1.5程序分析

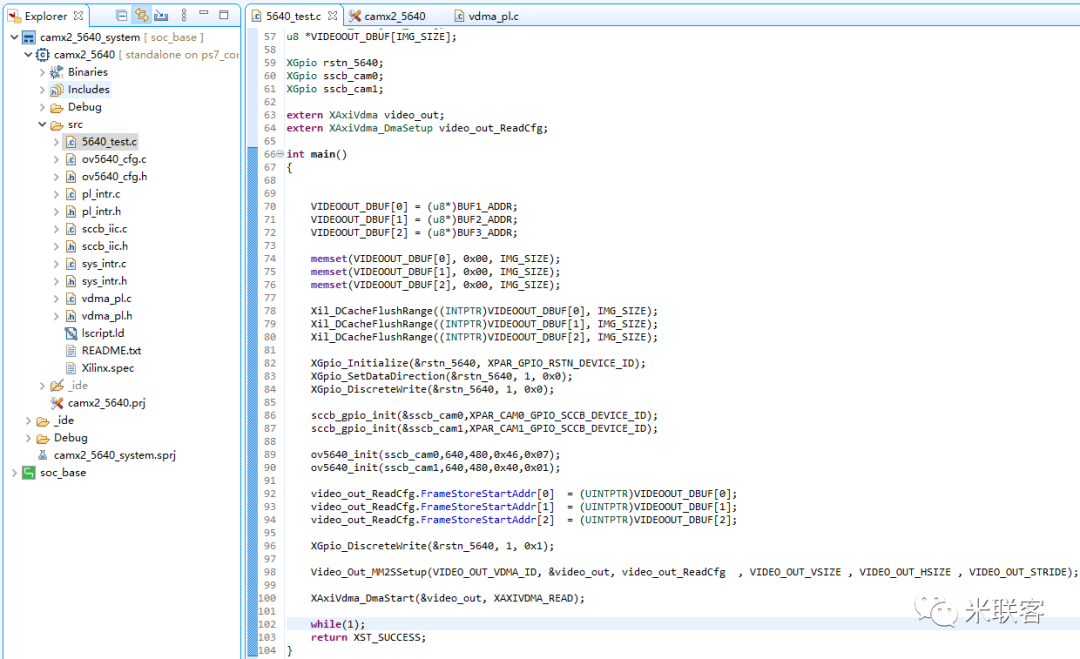

1.5.1 主程序分析

1:地址空间的分配

#define BUF_BASE_SIZE 0x08000000

#define BUF_RANG_SIZE 0x800000

#define BUF1_ADDR BUF_BASE_SIZE + BUF_RANG_SIZE*0

#define BUF2_ADDR BUF_BASE_SIZE + BUF_RANG_SIZE*1

#define BUF3_ADDR BUF_BASE_SIZE + BUF_RANG_SIZE*2

#define VIDEO1_OFFSET (640+1280*240)*4

为了保存2路视频图像,我们需要为2路视频图像分别设置2个缓存地址空间,同时未来能让2个图像显示在一个屏幕上,我们还需要对2路图像缓存地址做合理分配,其中Stride值在这里就大大有用了。

地址为0x08000000=128MB,每个缓存的空间大小为0x800000=8MB

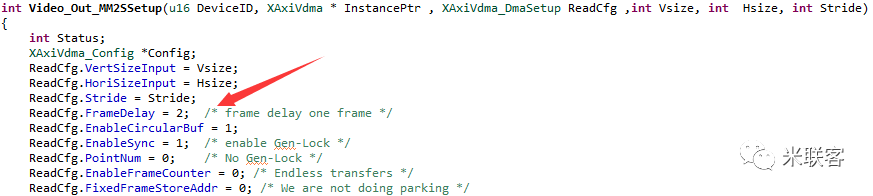

1.5.2 VDMA寄存器的参数配置

VDMA采用circle模式,为了确保视频图像输出的不撕裂,需要对帧延迟做正确设置:

VideoOut通道,是从模式,和CAM0通道同步,由于CAM1可能延迟1帧于CAM0,所以如果设置延迟1帧,可能和正在写入的CAM1通道内存重叠,导致CAM1图像撕裂,因此最佳设置是延迟2帧。

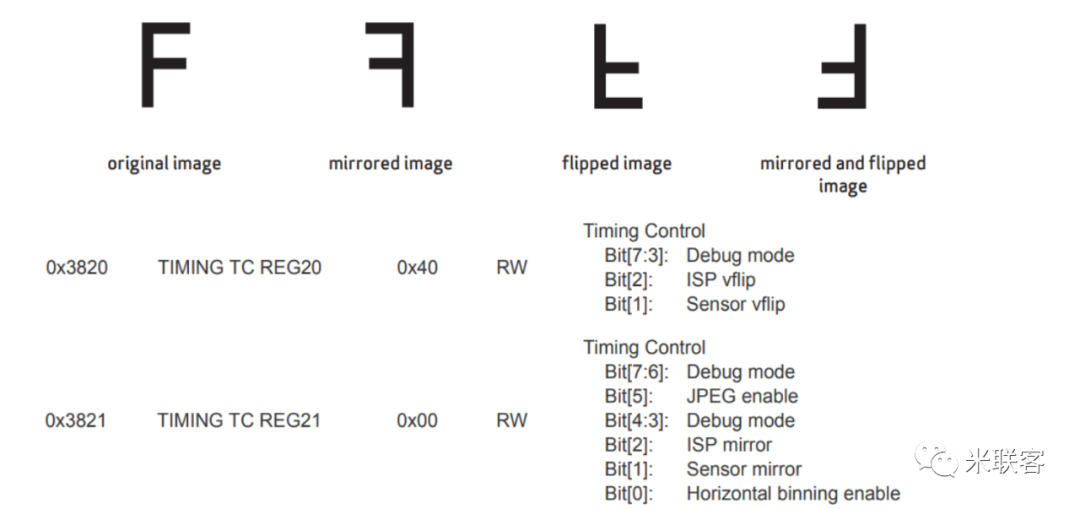

1.5.3:OV5640的镜像参数

本文中的摄像头模块采用了最新的FEP-CEPX3-CARD模块,该模块2个摄像头是对称放置,为了让2个图像都是同一方向,需要把其中的一路图像设置镜像

ov5640_init(sscb_cam0,640,480,0x46,0x07);

ov5640_init(sscb_cam1,640,480,0x40,0x01);

我们可以简单了解下OV5640和镜像相关的2个寄存器:

以看出来,只是两个寄存器:0x3820控制上下翻转,0x3821控制左右翻转。

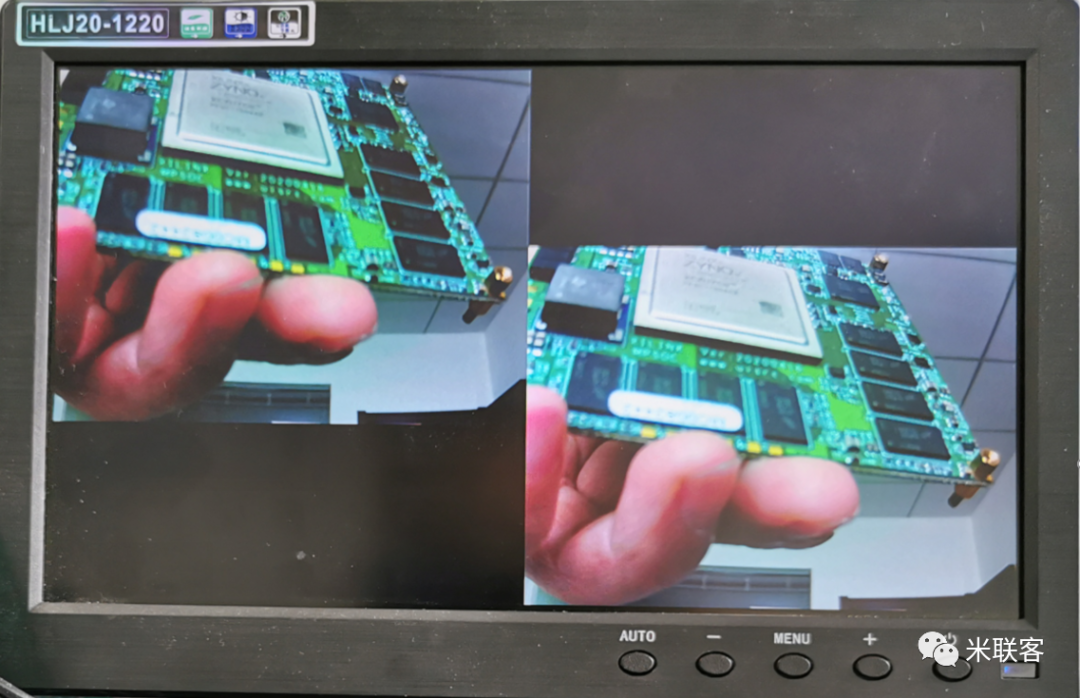

1.6双目采集方案演示

1.6.1产品介绍

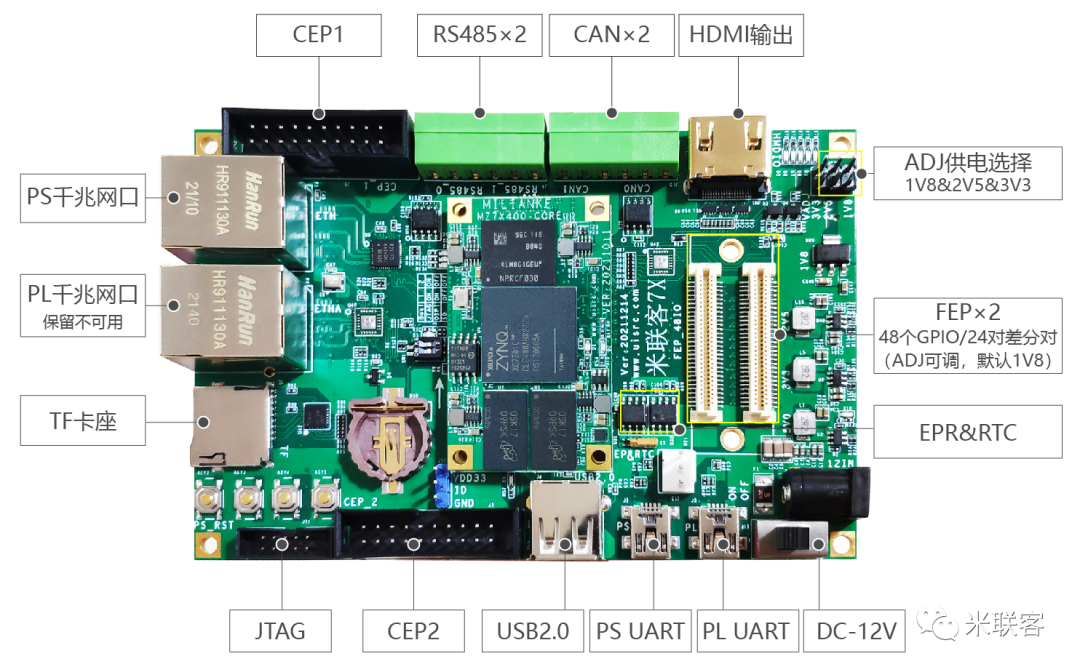

米联客7X开发板采用底板+核心板分体模式设计,兼顾稳定+便捷。核心板7X-7020采用XC7Z020-2CLG400I,具备85K逻辑资源,内存为2片512MB DDR3,8GB EMMC,128Mbit QSPI FL ASH。适合需要大量FPGA逻辑资源实现更多FPGA接口,或者算法的领域。

1.6.2硬件准备

本实验需要用到JTAG下载器、USB转串口外设,另外需要把核心板上的2P模式开关设置到JTAG模式,即ON ON(注意新版本的米联客7x,支持JTAG模式,对于老版本的核心板,JTAG调试的时候一定要拔掉TF卡,并且设置模式开关为OFF OFF)

1.7.62实验结果