ADC 服务的一些应用包括超高速多载波蜂窝基础设施基站

RS码是一种常用的纠错编码,本文主要介绍如何在vivado环境下利用RS IP核实现RS码的编译码。

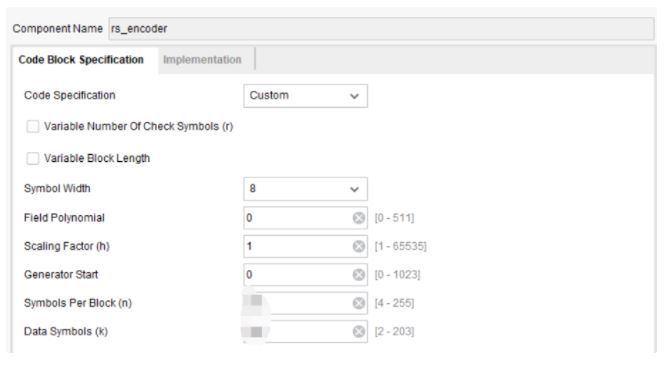

RS Encoder

首先对IP核的基本参数进行设置,需要配置数据的位宽,以及RS码的(k,n)参数。

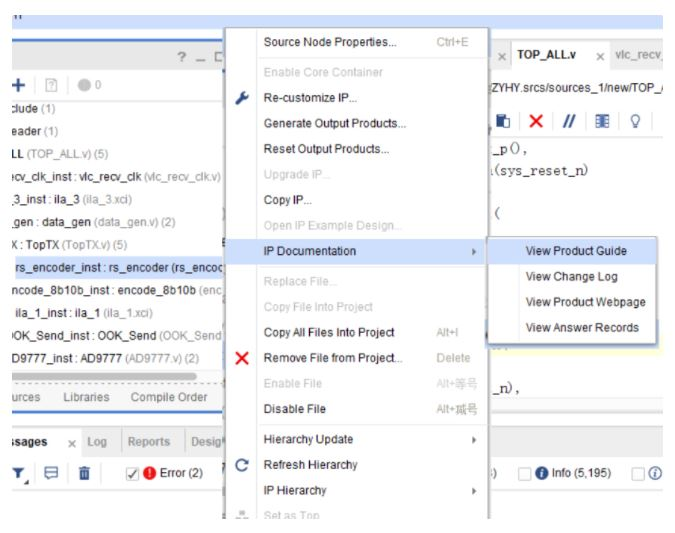

打开IP核的数据手册

RS Encoder核的所有引脚如下图所示,在进行例化时即按照该表中的引脚进行例化。

Signal一栏表示该IP核的所有引脚

DirecTIon一栏表示该引脚的输入输出状态

OpTIonal一栏表示该引脚是否可选择例化,No表示必须对该引脚进行例化,Yes表示该引脚可以选择不例化。一般进行例化时只对必须要进行例化的引脚进行操作

DescripTIon一栏是对该引脚的功能进行描述

需要注意的是s_axis_input_tready引脚为输出引脚,m_axis_output_tready引脚为输入引脚,不要被命名给搞混。

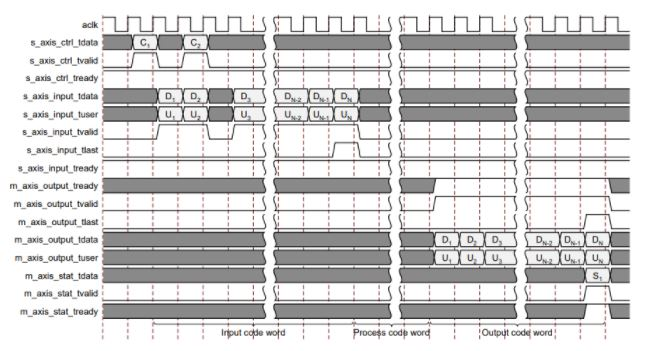

确定IP核的基本引脚后,就可以按照时序图来对IP核进行编辑,RS Encoder的时序图如下图所示:

按照时序进行控制:

输入端主要包含三个信号:s_axis_input_tdata、s_axis_input_tvalid、s_axis_input_tlast。s_axis_input_tdata为输入的待编码数据,s_axis_input_tvalid信号在数据输入有效时拉高,s_axis_input_tlast信号当一个数据段的最后最后一个数据到达时拉高。m_axis_output_tread一般保持高电平即可。

输出端主要用到三个信号:m_axis_output_tdata、m_axis_output_tvalid、m_axis_output_tlast。m_axis_output_tdata为编码后的信号,IP核输出为系统码,输出前面部分对应着输入的数据,后面部分对应的冗余数据;m_axis_output_tvalid在输出有效时拉高;m_axis_output_tlast在一个编码数据段的最后最后一个数据到达时拉高。

仿真结果如下图:

RS Decoder

RS译码核的操作与编码核类似,也是通过看手册中的引脚图和时序图进行操作,不做过多描述。

按照IP核的引脚表进行元件例化。

按照时序图对信号进行操作,从时序图中可以看到,我们的译码输入长度和输入长度相同,依然是带有冗余数据的,因此我们需要按照输入数据的长度进行裁剪。

仿真结果如下图(只截取了所需信号):

文章来源:FPGA之家

评论

求代码,我这边RS编解码不同步,不知道该怎么办