Vitis™ AI 环境是一种基于 AMD 赛灵思器件、开发板和 Alveo™ 数据中心加速卡的全栈式 AI 推断开发平台。从边缘到数据中心,它为 AI 加速提供丰富的 AI 模型、优化的深度学习处理器单元 (DPU) IP、工具、软件库以及示例设计。

随着人工智能算法的演进发展,更多开发者希望能够在 AMD 赛灵思平台上迅速部署 AI 模型,加速实现 AI 推断性能。本次开发者网络研讨会系列将分为三个章节,将分别演示如何集成深度学习处理单元、完成定制模型部署以及在不同平台上加速实现 AI 推断性能。

点击选择您的偏好时间,注册您最感兴趣的主题。如您无法参加实时直播,也可以先进行注册,我们会向您发送直播回放链接。

1. 借助 Vitis AI 平台部署基于 HLS 内核的用户定义模型算子

为提升 AI 算法的性能,Vitis AI 2.5 版引入了对 PyTorch 和 TensorFlow 模型自定义网络层更高级的支持。

本次网络研讨会将为开发者展示采用 HLS 内核在 Versal® AI Core 系列 VCK190 开发套件上灵活插入其自定义层并实现方案的工作流程。

2022 年 11 月 03 日

立即注册

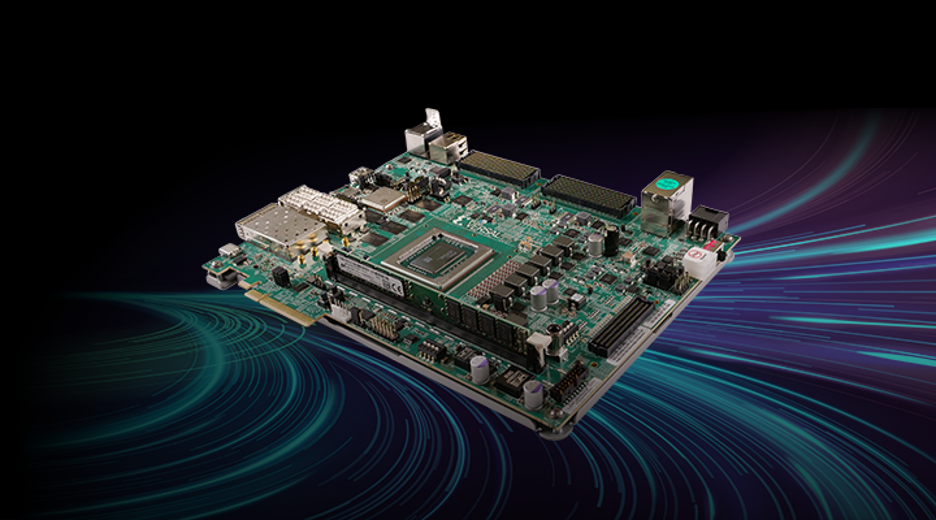

2. 面向 Versal ACAP VCK5000 开发卡的 WeGO 和用户自定义模型部署流程

全图形优化器 (WeGO) 通过集成 Vitis AI 开发套件与原生 AI 框架,提供了在云端深度学习处理单元 上部署 AI 模型的简化解决方案。

在本次网络研讨会上,我们将使用 Versal ACAP VCK5000 开发卡演示如何在Versal 平台上启动 TensorFlow 和 PyTorch 受训模型及其推断任务。

2022 年 11 月 10 日

立即注册

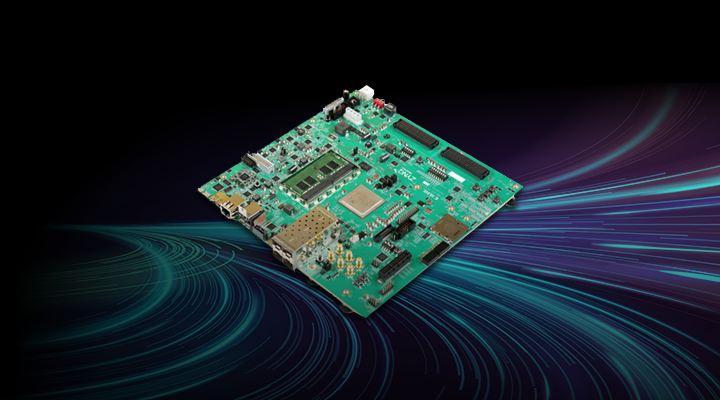

3. 如何在Zynq UltraScale+ MPSoC ZCU102 评估套件上运行 Vitis AI 深度学习处理单元 DPU IP

深度学习处理器单元 (DPU) 目标参考设计 (TRD) 提供了如何将 DPU IP 与 Vitis AI 环境相结合,构建和运行深度神经网络应用的指导。

本次网络研讨会将演示如何通过 Vivado® IP 集成器和 PetaLinux 对 TRD 的硬件和软件环节进行设计。我们将使用 Zynq® UltraScale+™ MPSoC ZCU102 评估套件作为参考,并通过运行 OpenPose 和 ResNet50 等示例模型进行讲解。

2022 年 11 月 17 日

立即注册

更多研讨会活动详情请点击:https://www.xilinx.com/about/events/2022/vitis-ai-development.html