作者:Nick Liu ,来源:Comtech FPGA

随着数据带宽需求的持续增长,数据传输从并行变成串行,收发器的速率越来越高,无论在单板内或者通过光纤和背板传输,都会带来一系列信号完整性问题。信号完整性,是指系统电路在信号传输过程中保持信号时域和频域特性的能力。如果信号经过信号线传输后依旧能保持其正确的功能特性,即信号在电路中能以正确的时序、幅度、相位等做出相应的动作,就表明该电路有较好的信号完整性。反之,就是信号完整性是有一定的问题的。信号完整性问题如何解决,如何保证误码率满足协议要求,从芯片选型、电路设计,再到PCB Layout的全过程都需要考虑。

一、高速Serdes信号完整性的问题和影响

1、高速Serdes信号完整性的问题

通常电信号在PCB上传输的时候主要涉及两个方面反射和插入损耗设计要求考量。

a、反射

反射是指在电信号传输时,每一时刻都会遇到一个传输线的瞬时阻抗,当该瞬时阻抗发生变化时,一部分信号将会反射,另一部分将会继续向前传输;或者说反射就是回波,信号功率的一部分传输到线上并达到负载端,但是有一部分反射会回到源端。

反射主要是由阻抗不匹配和stub引起的。例如线宽不一样,就会引起阻抗不匹配,信号传输中经过的耦合电容、过孔等位置都是会引起阻抗不匹配。

b、插入损耗

插入损耗是由介质损耗、导体损耗、导体表面粗糙度等原因引起来的损耗。不同的介质具备不同的插入损耗。背板设计的时候通常采用M4/M6板材取代FR4板材,虽然M4/M6板材成本也比较高也会比较贵,但是对应插入损耗远远优于FR4板材。

2、高速Serdes信号完整性的问题影响

我们发送的数据有高中低等多种频率,其中信号频率越高,插入损耗就越大。信号经过线路的传输,高频成分被衰减得更多,会导致码间干扰的产生。

码间干扰,又称ISI(Inter symbol interference),顾名思义是不同信号(码元)之间的干扰。码间干扰造成的后果是前一个bit的波形延伸到了后一个bit位置。在发送侧我们发送的bit是0-1-1-0,经过传输后最后一个1的波形延伸到后面一个0的位置,会造成0的电压变高,判决时候可能判决成1,这样本来发送的0-1-1-0,在接收端判决成0-1-1-1。这就是码间干扰。码间干扰的主要原因就是高频成分损耗大,低频成分损耗小。

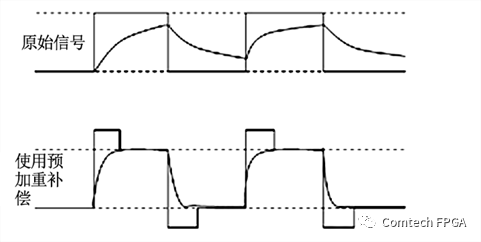

图一 码间干扰

二、AMD-Xilinx FPGA解决传输中的信号完整性方案

AMD-Xilinx FPGA在发送端使用了输出摆幅、预加重、去加重等技术,其中输出摆幅通常是用来增加信号的幅度;在接收端使用了均衡技术。

1、预加重后加重技术

为便于信号的传输,而对某些频谱分量的幅值相对于其他分量的幅值预先有意予以增强的措施。

预加重是在电平转换开始前有意过量驱动。信号传输线表现出来的是低通滤波器特性,传输过程中信号的高频成分衰减大,低频部分衰减小,预加重技术的思想就是在传输新的始端增强信号的高频成分,以补偿高频分量在传输过程中的过大衰减。信号的高频分量主要出现在信号的上升沿和下降沿处,预加重技术就是增强信号上升沿和下降沿的幅度。

图二 预加重信号变化

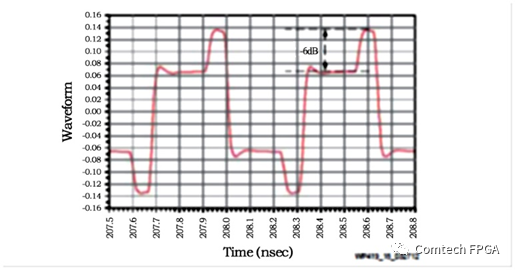

我们从时域上看去加重对波形的影响,看上去波形更奇怪一些,所以去加重有些像无线通讯中的一个术语“预失真”。

图三 预加重时域波形

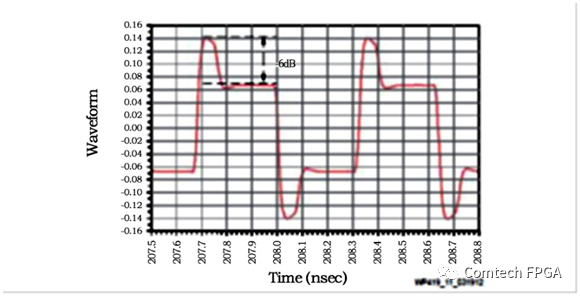

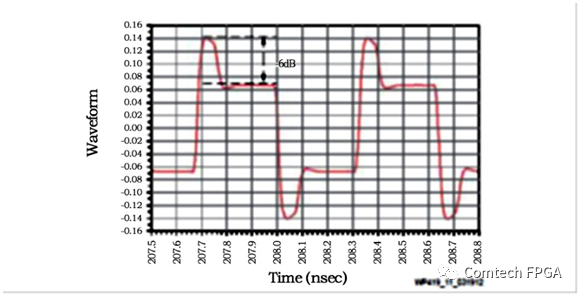

图四 后加重时域波形

我们可以看到pre-cursor和post-cursor处理的位置不同。预加重是在信号变化前处理,后加重是在信号变化后处理。

图五 使用预加重前后眼图对比

从图中我们可以看到,左边是经过去加重的接收眼图,右边是没有经过去加重的接收眼图。我们可以看到眼图的“眼睛”变得更大了。

2、 接收均衡技术

对于GTX/GTH收发器,基于系统级的功耗和性能的权衡,有两种类型的自适应滤波可用:

·功耗优化和低通道损耗的低功耗模式LPM

·均衡更低损耗通道的判决反馈均衡模式DFE

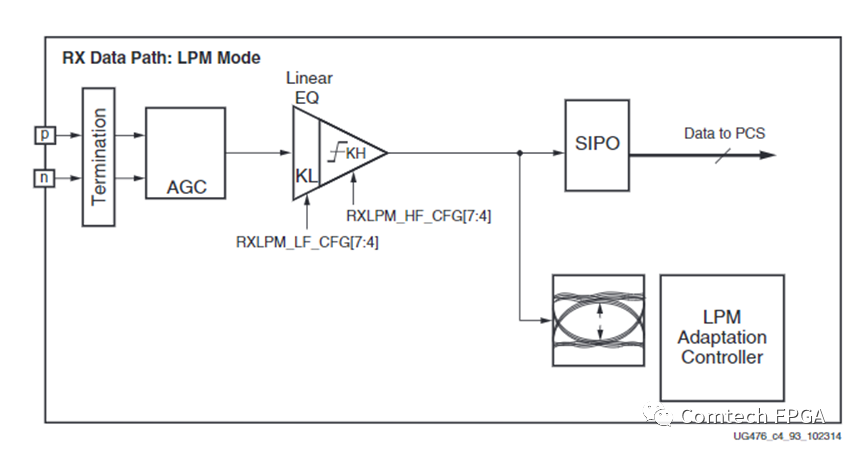

a、LPM

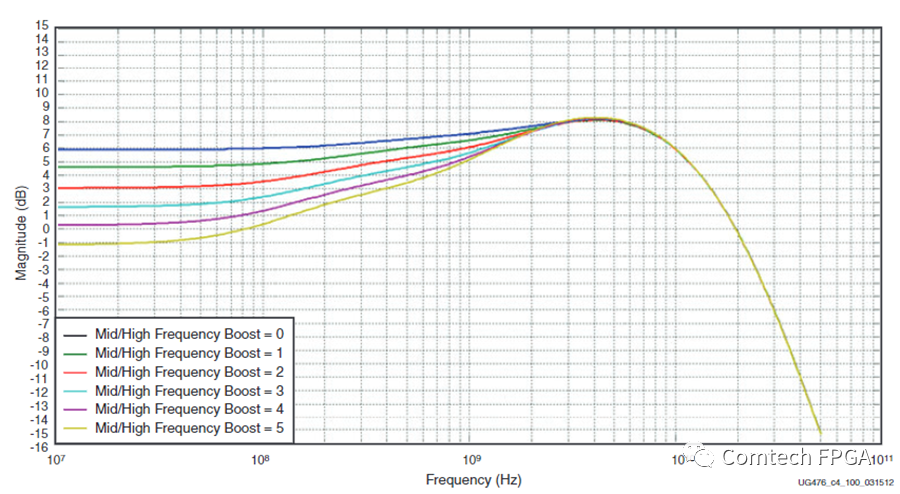

LPM模式下应用接收的线性滤波器,可衰减低频信号分量,放大奈奎斯特频率附近的分量,并衰减更高频率,这样就抵消了通道的低通特性。

图六 Serdes LPM Mode

可以调整连续时间线性均衡增益以优化低频衰减与高频放大的比率。缺点则是放大高频分量的同时噪声和串扰也被放大。

在GT Wizard中选择LPM 模式参数已经是自动调整模式,不需要我们去设置。

LPM模式的功耗比DFE模式小10%-15%,在通道损耗小于12db时候建议使用LPM模式。板内互联情况下通道衰减基本上都小于12db,使用LPM模式是一个比较好的的选择。

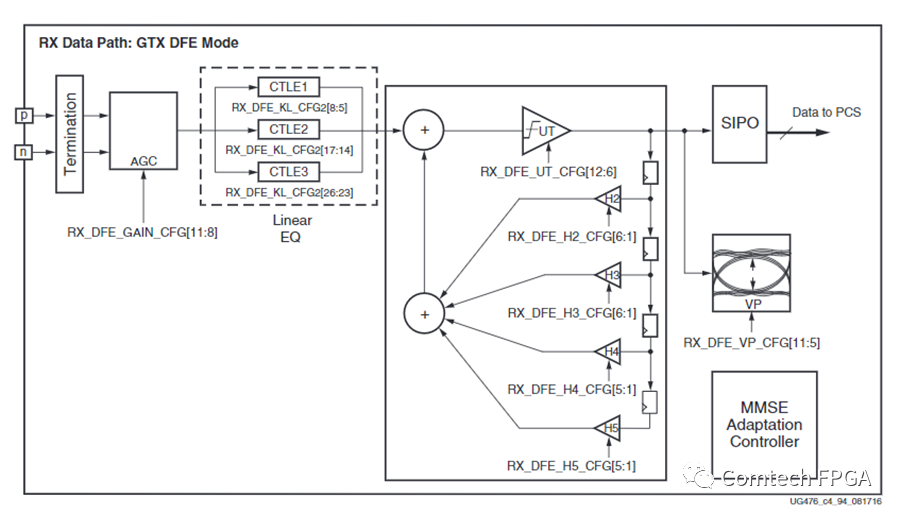

b、DFE

DFE模式通过提供更接近的调整滤波器参数,提供更好的传输通道补偿。但是,DFE模式不能移除发送bit的预加重,只能补偿post-cursor。线性均衡GTX/GTH RX DFE模式是一个离散时间自适应高通滤波器,该滤波器系数TAP由自适应算法设置。

图八 AMD-Xilinx FPGA Serdes DFE Mode

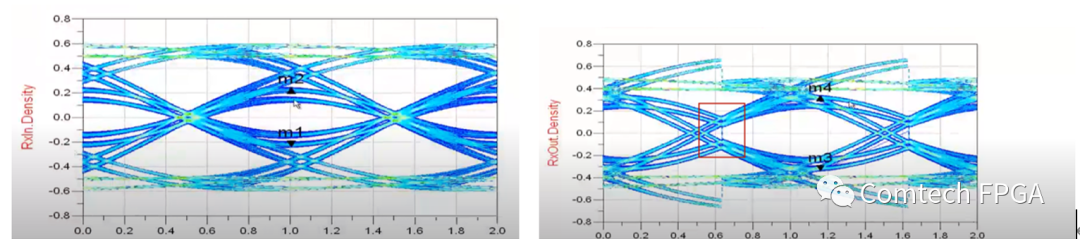

图九 使用DFE前后对比

左图不使用DFE均衡,右图是使用DFE均衡后,眼图张开的比左图要大,红圈位置是数据的变化沿,DFE延迟0.5个UI,因此在下一个数据的跳变沿就开始减去前一个bit带来的影响,而不是只在数据的采样位置才作用,这样眼图都变大了,所以DFE的眼图看起来有不连续性。

c、LPM和DFE模式的选择

DFE模式推荐用于中长距离应用,在奈奎斯特频率下的信道损耗为8dB或者以上。DFE和CTLE相比不会放大噪声和串扰,数据经过衰减很大的通道后接收的数据信号幅度已经很小了,这个时候高频的噪声和串扰对信号影响就会很大。

目前DFE的参数在FPGA中都是算法自动调整,不需要我们去设置。在使用8B10B编码的协议而且数据没有加扰的情况下,如果线路上长时间发送固定码型会使得DFE自动调整算法漂移,引起负面效果。因此在8B/10B编码而且数据没有加扰的协议里面是不建议使用DFE的。而更高速的协议都是64B/66B、128B/130B编码, DFE一般用在这种场合。

另外,在高速收发器通过背板连接的应用中,因为过孔和连接器阻抗不匹配引起反射,通道的衰减就像图中浅绿的线,在某些频率点衰减很大。在这种情况下CTLE的效果就比较差,DFE的效果就会比较好。

如果您正在研究AMD-Xilinx FPGA serdes相关设计,打算开始一个新的设计,欢迎联系科通,我们帮您共同实现!