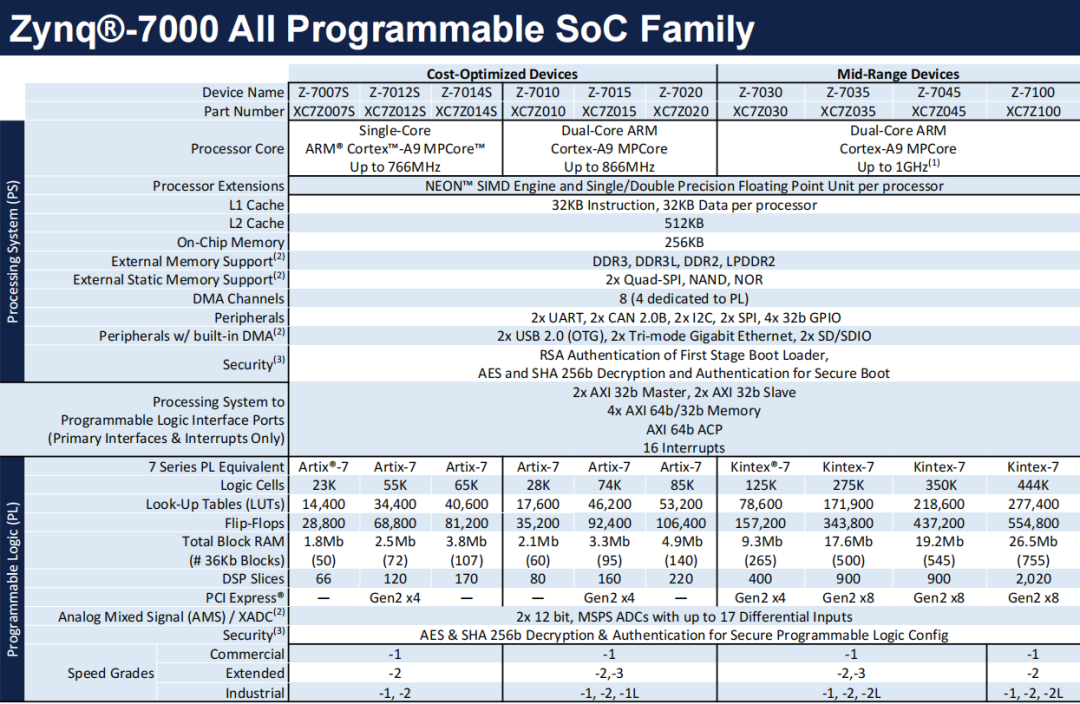

Zynq-7000系列芯片的逻辑资源(PL)是不同的,Z-7020以下是基于A7 FPGA的,Z-7030以上是基于K7的,资源数量有所不同。而我们使用的Zedboard是Z-7020的。

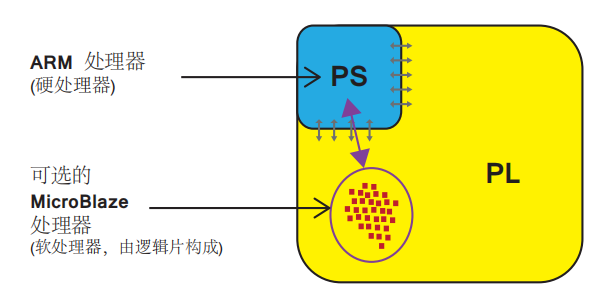

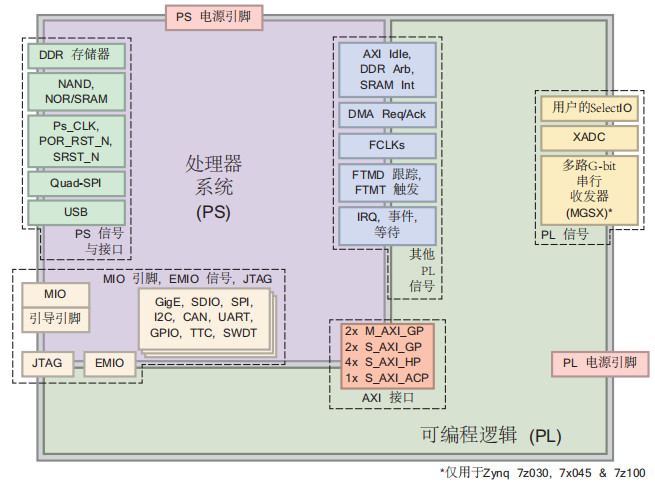

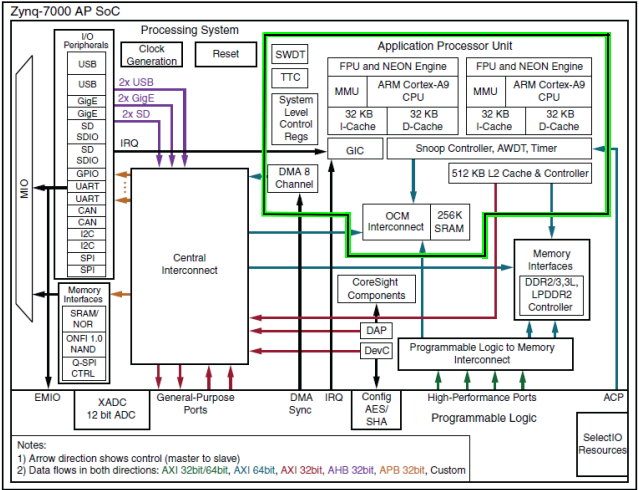

Zynq中所说的PS是指ARM处理器,PL是指FPGA部分,它们之间的主要连接方式是高带宽低延迟的AXI接口,这也是Zynq上主要的数据通信机制,AXI_ACP是用于PL的一个cache一致性主机端口,AXI_HP用于PL的四个高性能/大带宽主机端口,AXI_GP是通用端口,两个主机端口,两个从机端口。

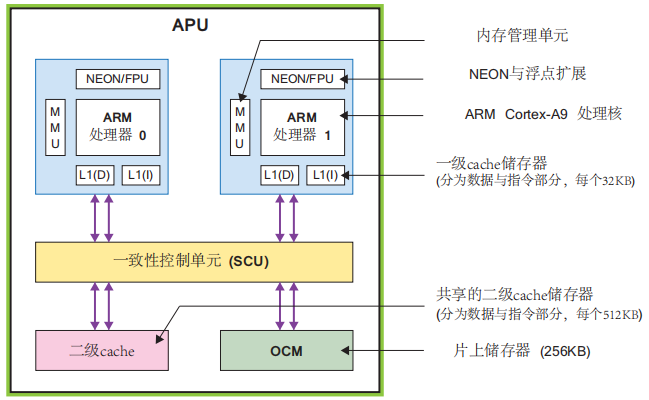

其中APU主要由两个ARM处理核组成,每个都关联了一些可计算单元:一个NEONTM媒体处理引擎和浮点单元,一个内存管理单元和一个一级cache存储器等。其中NEON指令是对标准ARM指令集的拓展,可直接使用,NEON引擎实现了单指令多数据(SIMD)功能来实现媒体和DSP类算法的加速。

从编程的角度来看,对ARM指令的支持之前是由xilinx的SDK软件来实现的,不过现在都统一到vitis软件中了,它包含了开发部署在ARM处理器上的软件所需的全部内容。目前最新的版本是vitis 2022.2,我们使用的是2021.2。

本文转载自:雷达通信电子战