作者: Brian Liu,来源:Comtech FPGA

1、前言

FPGA实现ISP(Image Signal Processor)过程中,在图像接收、处理、传输过程中往往会接触到各种各样的图像格式,比如接收图像可能是原始RAW数据,驱动LCD显示器需要RGB格式,HDMI/SDI显示需要YUV格式等。各种图像格式之间可能涉及到相互转换,本文简单介绍几种常见的图像格式以及Xilinx FPGA实现方式。

2、Bayer图像

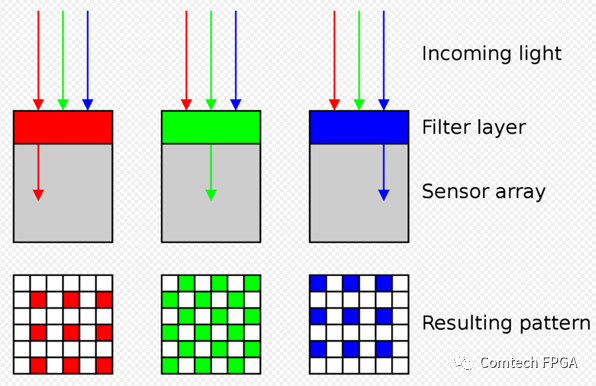

典型Bayer图像的成像过程如下图所示。

图2-1 CFA示意图(图片来自wikipedia)

随着技术的发展,也有一些其他滤镜的Sensor出现,如RGBW、EXR、X-Trans等,如下图所示。

图2-2 RGBW、Fujifilm “EXR”、“X-Trans”示意图(图片来自wikipedia)

通过上图可以发现,这些滤镜中,绿色的分量最多。这是因为人眼对绿色最为敏感,所以保留最多的绿色分量。

3、 Demosaic

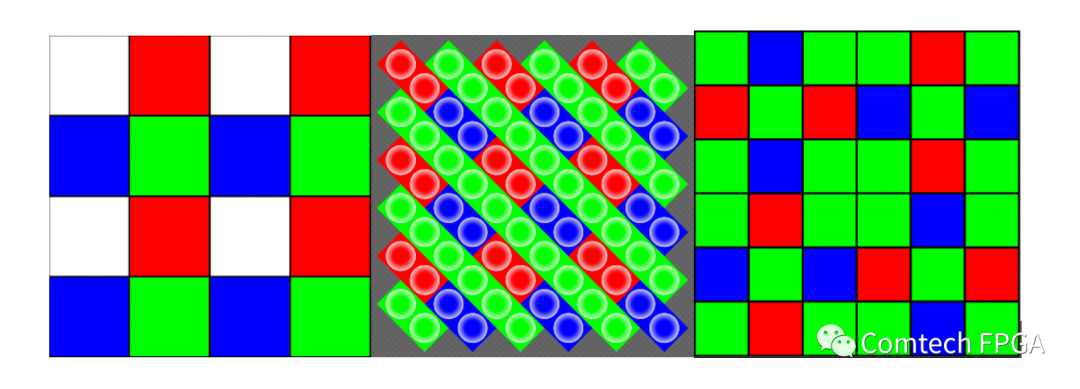

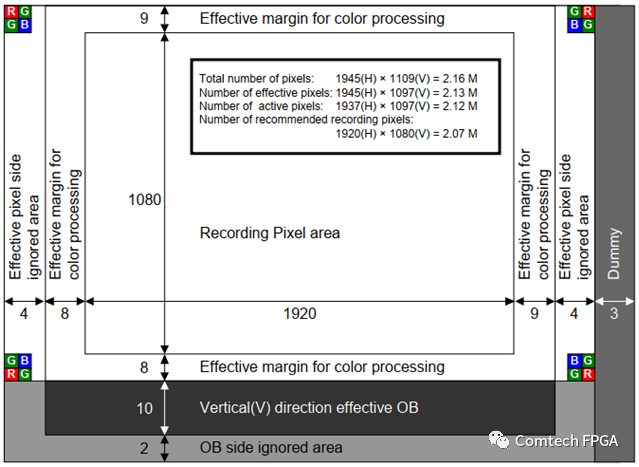

Bayer图像采集到FPGA以后,每个像素只有一种颜色分量。以Sony IMX290为例,输出图像的bayer格式如下图所示:

图3-1 Sony IMX290 Pixel Arrangement

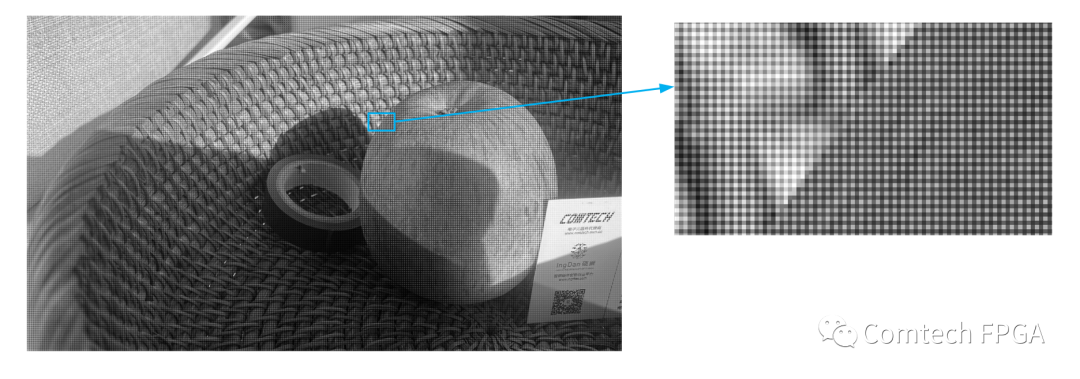

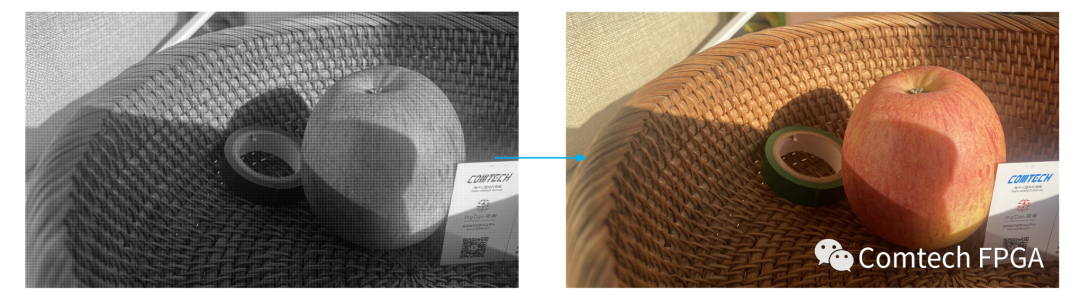

此时,如果将采集到的1920x1080图像以灰度展示,由于CFA的原因,图像会呈现一种马赛克现象,如下图所示:

图3-2 Bayer image

每一个像素仅包含光谱的一部分,需要通过插值来填充每个像素的RGB分值。为了从Bayer格式得到每个像素的RGB格式,需要通过插值对每个像素填补缺失的两个颜色分量。插值的方法有很多(包括近邻、双线性等)。

插值后可以得到RGB图像:

图3-3 Bayer to RGB

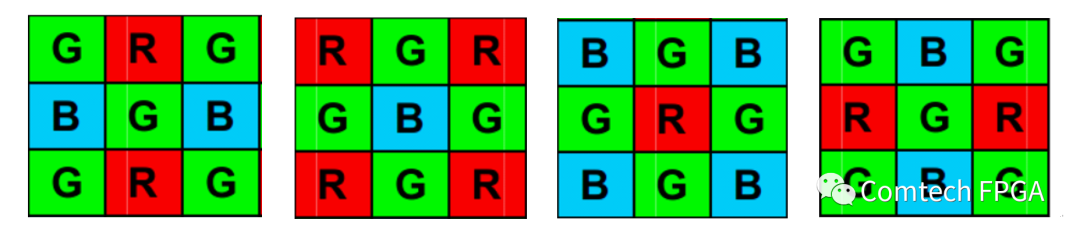

需要注意的是,Bayer图像根据第一个像素的颜色分量有4种排列方式,分别为GRBG、RGGB、BGGR、GBRG:

图2-4 Bayer 4种排列方式

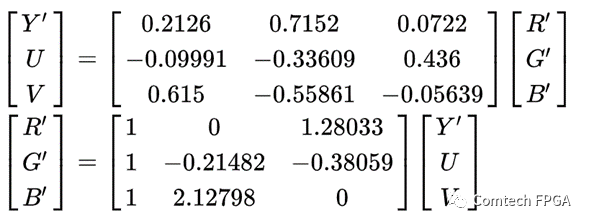

4、 RGB/YUV颜色空间转换

图4-1 BT.601标准

图4-2 BT.709标准

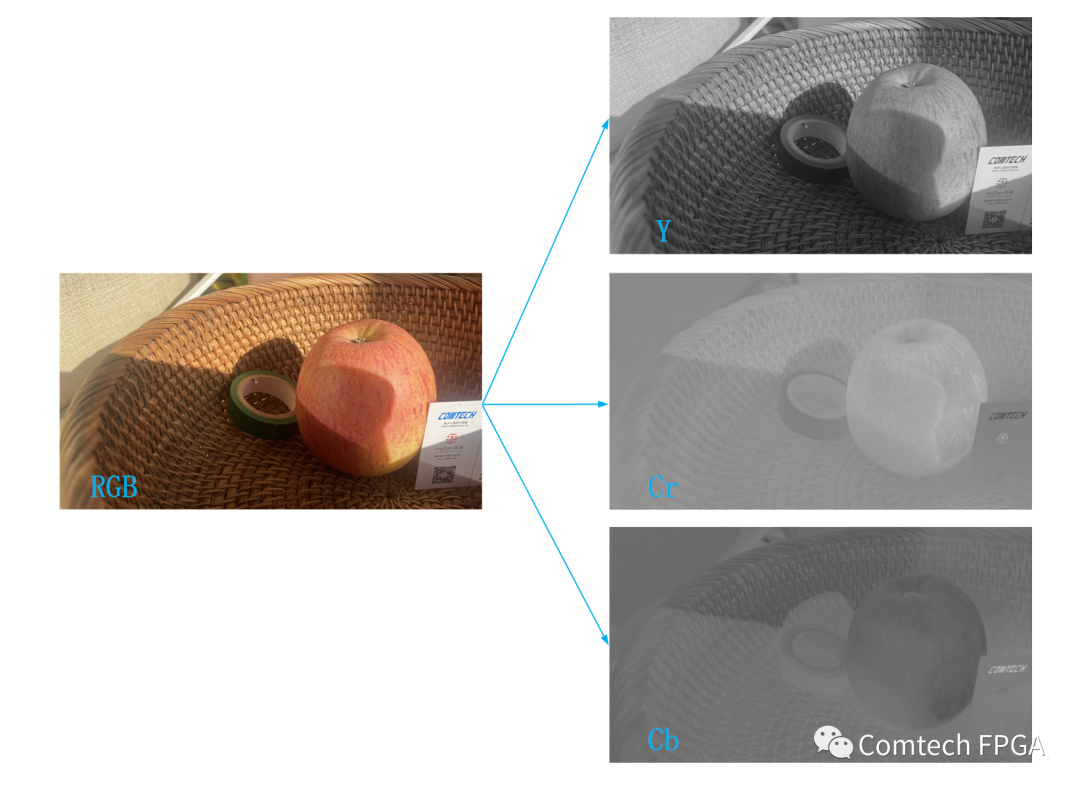

图4-3 RGB to YUV444

5、延伸

Cb=U*r+128;

Cr= V*r+128;

图5-1 饱和度设置效果

6、AMD-Xilinx FPGA实现

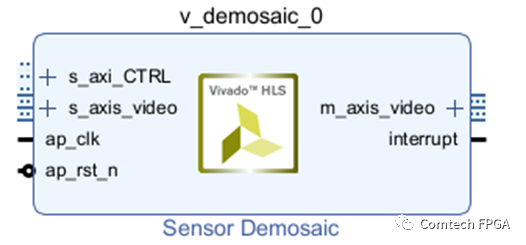

IP接口如下图所示:

图6-1 Xilinx Demosaic IP core

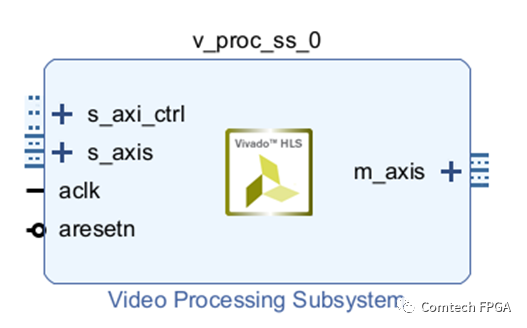

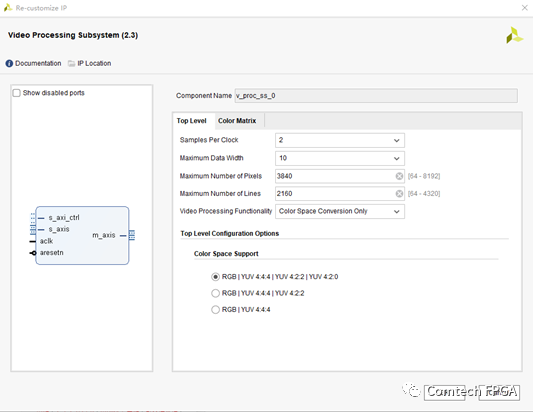

IP接口以及配置方式如下图所示:

图6-2 Xilinx VPSS IP core

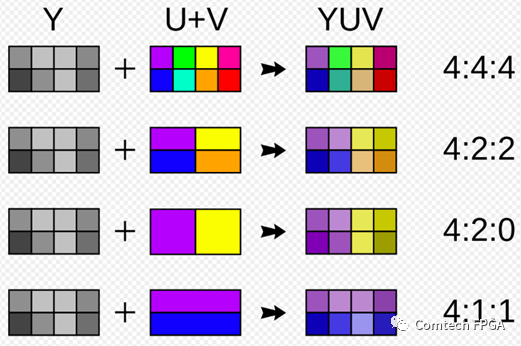

Xilinx提供的VPSS(Video Processing Subsystem),可以很方便地对RGB、YUV444、YUV422、YUV420进行互转。RGB与YUV的互转公式如下:

YUV to RGB:

B = Y + ((Cb * 2081) >> 10)

Cr = V - (1<<(HSC_BITS_PER_COMPONENT-1))

Cb = U - (1<<(HSC_BITS_PER_COMPONENT-1))

R = Y + ((Cr * 1733) >> 10)

G = Y - ((Cb * 404 + Cr * 595) >> 10)

RGB to YUV:

V = (1<<(HSC_BITS_PER_COMPONENT-1)) + (((R-Y)*898)>>10)

Y = (306*R + 601*G + 117*B)>>10

U = (1<<(HSC_BITS_PER_COMPONENT-1)) + (((B-Y)*504)>>10)

其中HSC_BITS_PER_COMPONENT = C_MAX_DATA_WIDTH (这里C_MAX_DATA_WIDTH可以由用户通过GUI设置。)

综上,使用这两个IP即可基于Xilinx FPGA快速实现Bayer与常见颜色空间转换。