本文转载自: 明德扬FPGA科教微信公众号

本文讲一下随路时钟,什么是随路的时钟呢?

第1节 随路时钟的概念

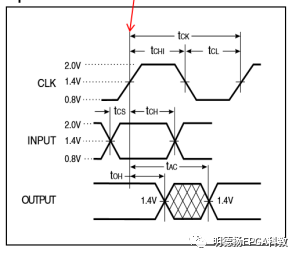

如图1是一个SDRAM的接口时序图,大家如果做外部接口,使用过各种芯片,一般也能看到类似这样接口时序图。CLK是时钟信号,INPUT代表输入SDRAM的各种信号,OUTPUT表示SDRAM输出的各种信号线。其实芯片接口就是一些寄存器,既然是寄存器,那么这些寄存器想要稳定寄存数据,就会对数据信号有建立时间和保持时间相关的要求。

图1 SDRAM接口时序图

如图1所示,在CLK的上升沿时,要求INPUT必须提前tCS到达,并且延迟tCH,所以该接口寄存器的建立时间为tCS,保持时间为tCH,最后通过数据手册可以获取这些参数对应数值。那么在设计时序时就要考虑建立时间和保持时间对数据的影响,即INPUT要在时钟上升沿的建立时间之前稳定,并且在上升沿之后最少稳定保持时间对应的时间。这是SDRAM的一个接口时序要求,也与多数的芯片接口时序类似。

这是芯片接口需要满足的时序要求,那我们在做实际项目的时候,如何去满足这个下游器件的时序要求呢?

第2节 实际应用中,如何做到满足

2.1建立时间、保持时间的影响因素

那在设计当中如何做才能满足这个时序要求,首先分析一下影响建立时间和保持时间的因素有哪些呢?

其实影响建立时间、保持时间的因素是很多的,例如说FPGA内部的寄存器传输延时、寄存器到管脚的延时和PCB板上的走线延时等等,这些延时最终都会影响时钟与数据的关系,从而就会影响到下游器件的输入数据到底能不能满足芯片接口时序的建立时间和保持时间要求了。

2.1.1 理想波形

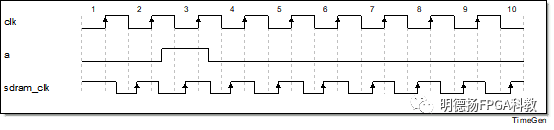

如图2是一个理想的波形,信号a的波形在时钟的上升沿发生变化,在第2个时钟上升沿到达时,信号a从低电平变为高电平,在第3个时钟上升沿到达时,信号a由高电平变为低电平。在两次变化过程中,没有任何延迟。能够在时钟变化时立即发生相应的变化,这种理想的波形,它的数据会立即到达下一个寄存器,会发现时钟上升沿之前的时间周期就是时钟周期T,而且在时钟上升沿之后稳定的时间是0。由此,很明显理想观点是不满足保持时间要求的。

图2 理想的时序图

2.1.2 带有寄存器延时、寄存器到管脚延时的波形

如果信号a在传输时经过寄存器延时、寄存器到FPGA管脚的传输延迟Tco后,那么可能看到FPGA管脚上出来的信号相位关系就变成如图3所示。

图3 引入寄存器延迟和寄存器到管脚延时

clk是时钟,信号a可能对时钟会有一定的延时。由图3中可以看到,信号a会在时钟的第2个上升沿之后的一段时间才发生变化,这是由于寄存器延时造成的。在时钟上升沿第3个去采样时候,才发现信号a会提前时钟周期T-Tco这么长的时间变为稳定。上升沿之后保持了Tco,有时候延时多久就保持多久,对不对?

2.1.3 加上走线或其他延时(Tpcb)

实际波形如下:

增加延迟,信号可能会相对时钟往后延迟,在时钟上升沿之前的时间会保持多久?在时钟2时信号a变高,经过寄存器延时(tco)之后,在经过走线延迟等等,信号传递时钟3,因此时钟上升沿前的时间为(T-tco-tpcb),上升沿后保持的时间为(tco+tpcb)。那这是正常的延时情况。

那么只要满足T-tco-tpcb这个延时大于建立时间要求,并且tco+tpcb这个延时大于保持时间要求。那电路就是正常的,那如何才能做到这一点呢?但时钟周期,PCB走线延迟一般都是固定的,对于特定的FPGA芯片,寄存器延迟也是固定的,只有信号从寄存器传输到芯片管脚的延迟可以改变。

第3节 两种有效解决方法

3.1 添加时序约束,设置输出延时set_output_delay

有两种做法,一种是添加时序约束,Set output delay。这个约束会告诉综合软件下游器件的建立要求是多少和PCB走线延迟是多少,由于时钟周期和PCB走线延迟是固定的,对于特定的器件,寄存器延时也是固定的,根据T-TCO-TPCB,综合软件就会通过调整寄存器到管角的延时,这个延时放大或放小,从而使下游器件能采集到这个数据,满足下游器件的建立时间和保持性要求。

3.2 添加随路时钟

另一种方式添加随路时钟,什么是随路时钟再看一下。

如上图所示,信号a是在clk时钟域产生的信号。Sdram_clk是与clk同源、频率相同、相位不同的时钟信号。当sdram_clk 输出作为sdram的工作时钟,通过调整sdram_clk的相位就能调整时序,从而满足建立时间和保持时间的要求。假如这是CLK,用PLL产生一个SDRAM的CLK,这两个CLK的使用频率是一样的。比如说一开始有个150M的FPGA时钟clk ,FPGA的时钟clk通过PLL产生一个相位有一定偏差的150M时钟sdram_clk。可以看到clk上升沿的时候,隔了很久,sdram_clk的上升沿才出现,而这两个时钟的时钟频率一样、相位不一样。

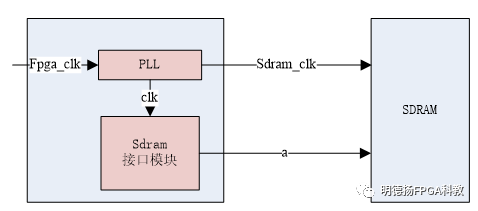

那么sdram_clk如何产生呢?可以通过PLL来产生,PLL可以保证频率相同、相位偏移量,所以该系统的结构如图:

第一个时钟clk可能就给Sdram接口模块作为系统时钟,sdram_clk直接就给SDRAM芯片作为数据采集的时钟了,那这样就有什么后果呢?

由于信号a是在clk时钟产生的,使得信号a是相对于时钟clk有一定的延时的。sdram_clk相对时钟clk有一定延时,有一定项目偏差。只要调整sdram_clk相位,就可以使得信号a在时钟sdram_clk的上升沿满足建立时间和保持时间的要求。比如可以调整sdram_clk,让sdram_clk上升沿刚好在信号a变化的中间。也就是说项目开始可以通过调节锁相环PLL的sdram_clk相位,使得下游芯片使用sdram_clk的上升沿去采集信号a时,能够同时满足建立时间和保持时间要求。只要调整好,那么这个系统就可以正常工作。

Sdram_clk就是随路时钟,随时钟把数据一起送到下游芯片。通过调整Sdram_clk相位,让接口信号和时钟满足下游接口芯片的建立时间和保持时间要求,这就是随路时钟的方法。

第4节 两种方法优缺点及取舍

4.1 第一种方法优缺点

那这种方法有什么优缺点,如何取舍,第一点就是常规做法,就是一个时序约束的做法。产生两个时钟,但调试还是比较麻烦的。并且有一点就是我们用的时间,对不对?它是有时间有限度的,因为调整是TCO,它一定是有限度的,就是任意调都可以是吧?比如说是调不了的,这时候就需要用Sdram_clk随路时钟的方法去做了。

4.2 第二种方法优缺点

随路时钟调试起来简单,PLL设置简单,出错可能性小。不断的调整相位,总能找到一个点让时序满足。但是也明显的,需要有个PLL来产生这个时钟,会消耗锁相环硬件资源。如果使用这种方法,就不用设置output delay之类的约束,直接用调整相位方式找到同时满足建立时间和保持时间要求的点就ok 了,所以随路时钟这种方法很多项目都喜欢用。

第5节 接收方向

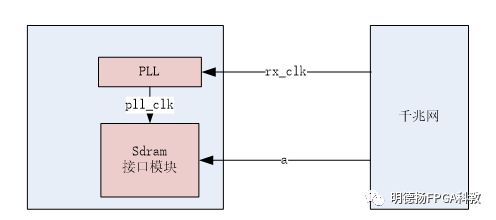

SDRAM是TX(输出)方向的,输入方向是同样的道理。比如说千兆网模块就是接收数据的,如下图所示。

它有个时钟rx_clk,假设信号a为输入数据,时钟信号与数据a对齐。这个时候如果我直接用rx_clk去采集信号a,可能就就不满足了寄存器的建立时间和保持时间了,那怎么办呢?以下两种方法:此时就可以时钟信号,

5.1 方法1

设置输入延时set_input_delay。FPGA根据时序情况,增加寄存器延时、时钟延时等,从而满足FPGA本身的建立时间和保持时间要求。比如说set input delay,FPGA 根据调整,去增加寄存器延时等方式,来满足自身建立时间和保持要求。

5.2 方法2

另一种方式也可以跟SDRAM一样,用rx clk通过锁相环生成一个与rx_clk频率相同,相位不同的pll_clk作为千兆网接口模块的时钟信号。用pll_clk去采集信号a的数据,这样不断调整pll_clk相位,使得pll_clk时钟上升沿位于信号a中间,此时就可能满足寄存器建立时间和保持时间要求了。这个时候就不用设input delay 了,就不用设时序约束了,这个时候就ok 了。所以这种方法特别是做接口调试的时候特别有用。像千兆网、SDRAM、DDR2这种东西,全部都可以用这种方式去做。

要注意的是由于这种方式,使用了一个锁相环PLL的,锁相环PLL对其输入时钟是有要求的,要求输入的时钟必须来自于FPGA芯片的时钟管脚,否则综合软件会报错,这是唯一的要求。