作者:Gary Pan,来源:AMD Xilinx开发者社区

CPRI是无线通信里的一个标准协议,连接REC和RE的通信。

Xilinx有提供CPRI IP核。

区别于其它通信协议,如以太网等,CPRI是一个同步系统。

这就意味着两端的Master和Slave应当是同源时钟的,两边不存在频差,并且内部延时也都是固定的,每次运行可以通过计算获得,供上层应用使用。因此,可以让Master有一个参考时钟使用,而Slave则利用GT从串行数据中恢复出来的时钟,经过外部一个Cleanup的PLL,产生参考时钟送回来,供Slave参考使用。这样,两端就能同源了。

注意,由于Xilinx的GT模块限制,这里外部需要提供一个,在还没有恢复钟送到,就能自主产生相同频率(但有ppm差异)时钟的PLL;等到Slave收到数据,同步并产生恢复时钟后,外部的这个PLL也能将频率渐渐对齐到恢复时钟(即对端Master真正频率上面),最终实现整个同步系统。

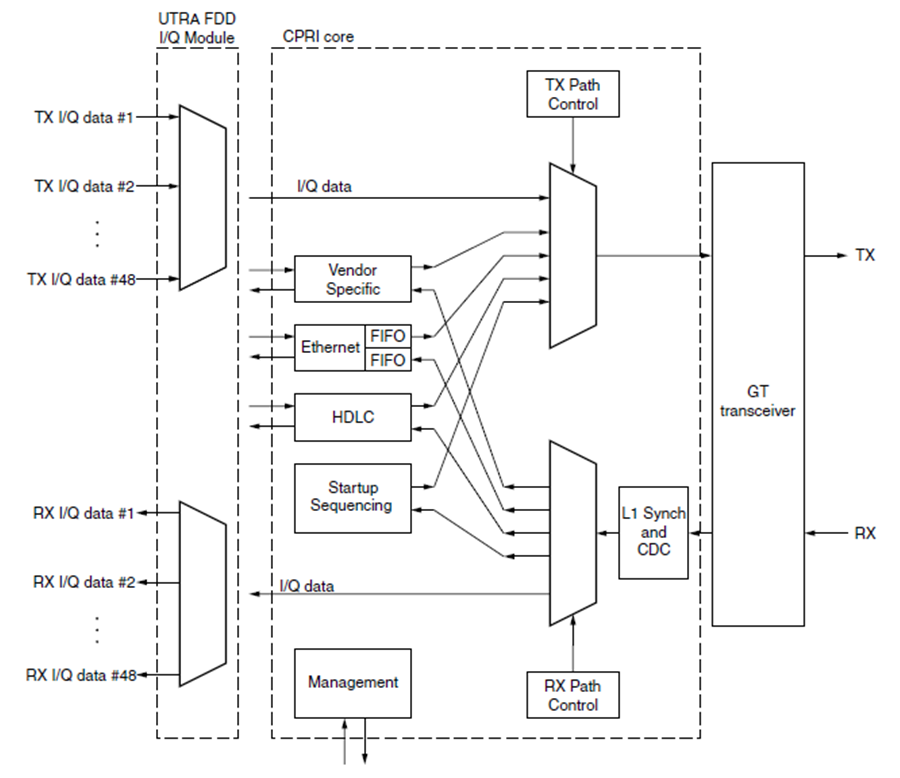

CPRI的内部结构如下图所示。CPRI数据,主要指的是IQ数据通道,另外还有控制数据,包括Vendor Specific,Slow C&M(即HDLC数),Fast C&M(即Ethernet数),这些数据共同分享CPRI物理层通道。

接下来,分析CPRI的数据帧格式,以帮助我们进一步了解这些不同类型的数据,是如何共同复用CPRI通道的。

无线通信中,UTRA-FDD的Chip Rate为3.84MHz(fc)。因此在CPRI的协议中,一个基本帧(Basic Frame)的时间长度就是1/fc=260.416667ns。

那么,CPRI的基本帧的结构就如下图所示,如果是614.4Mbps的CPRI应用,那Y就只会等于0,数据为Z.X.0打头,有16个bytes数组成,第1个byte一般做控制用,后15个bytes就是IQ数据。

如果是2457.5Mbps的CPRI应用,带宽更大,Y就可以为0,1,2,3,按照下图所展示的发送顺序发数,一个基本帧里有Z.X.0,Z.X.1,Z.X.2,Z.X.3,四个控制字,和60个bytes的IQ数据。

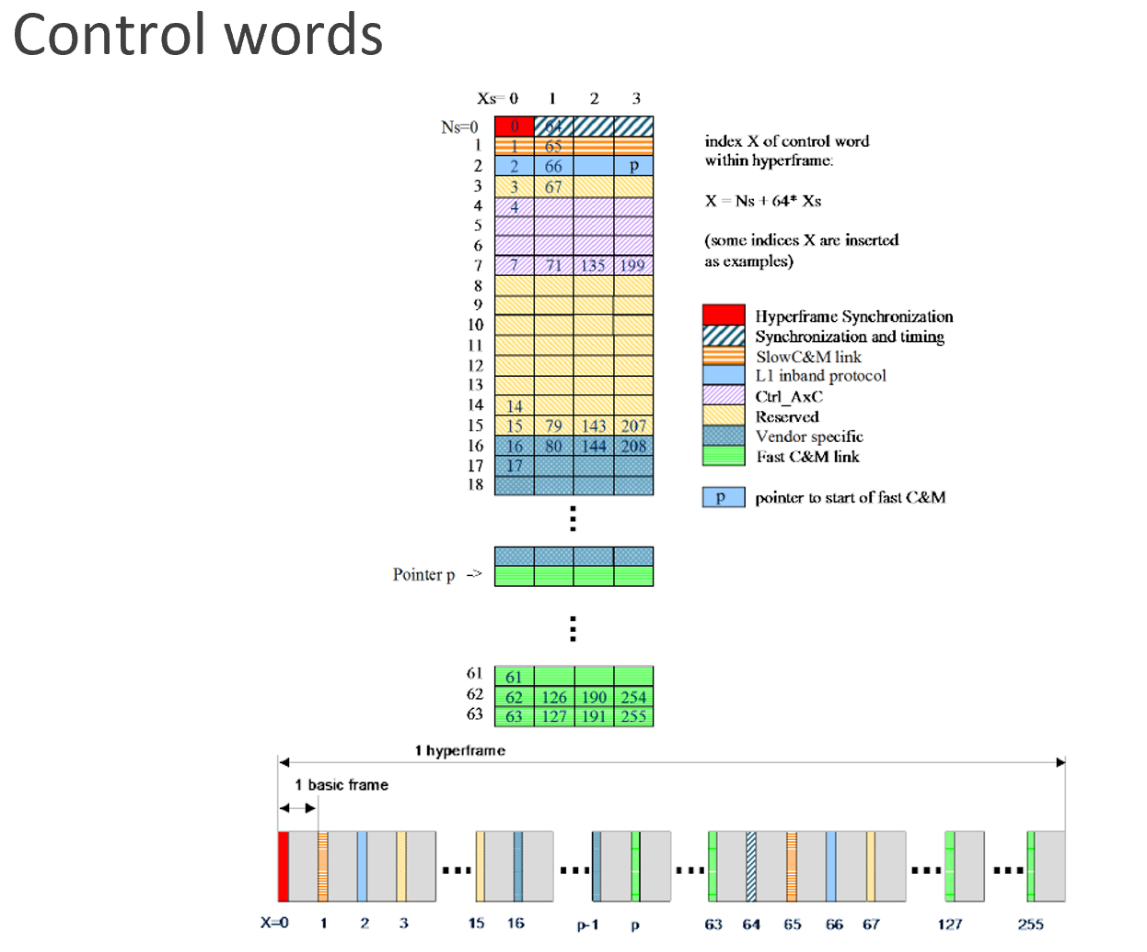

进一步,CPRI每隔10ms是一个完整的无线帧,其中由150个超帧(hyperframe)组成,每个超帧又由256个上面的基本帧组成。

之前已经提到过,每个基本帧的第1个byte一般做控制用;下图就展示了一个超帧,里面含有256个基本帧,这样一个超帧里就有256个bytes可作控制用途,非IQ数据的Control Words。

并且,由图里的位置,可以看到每个control words的用途,如Z.0.0是用作同步的帧头数据;Z.1.0作为Slow C&M,也就是HDLC数据用;而Z.2.0,Z.66.0,Z.130.0,Z.194.0这一排四个控制字,会在协议通信,对照信息的时候,都有各自不同的用途定义。

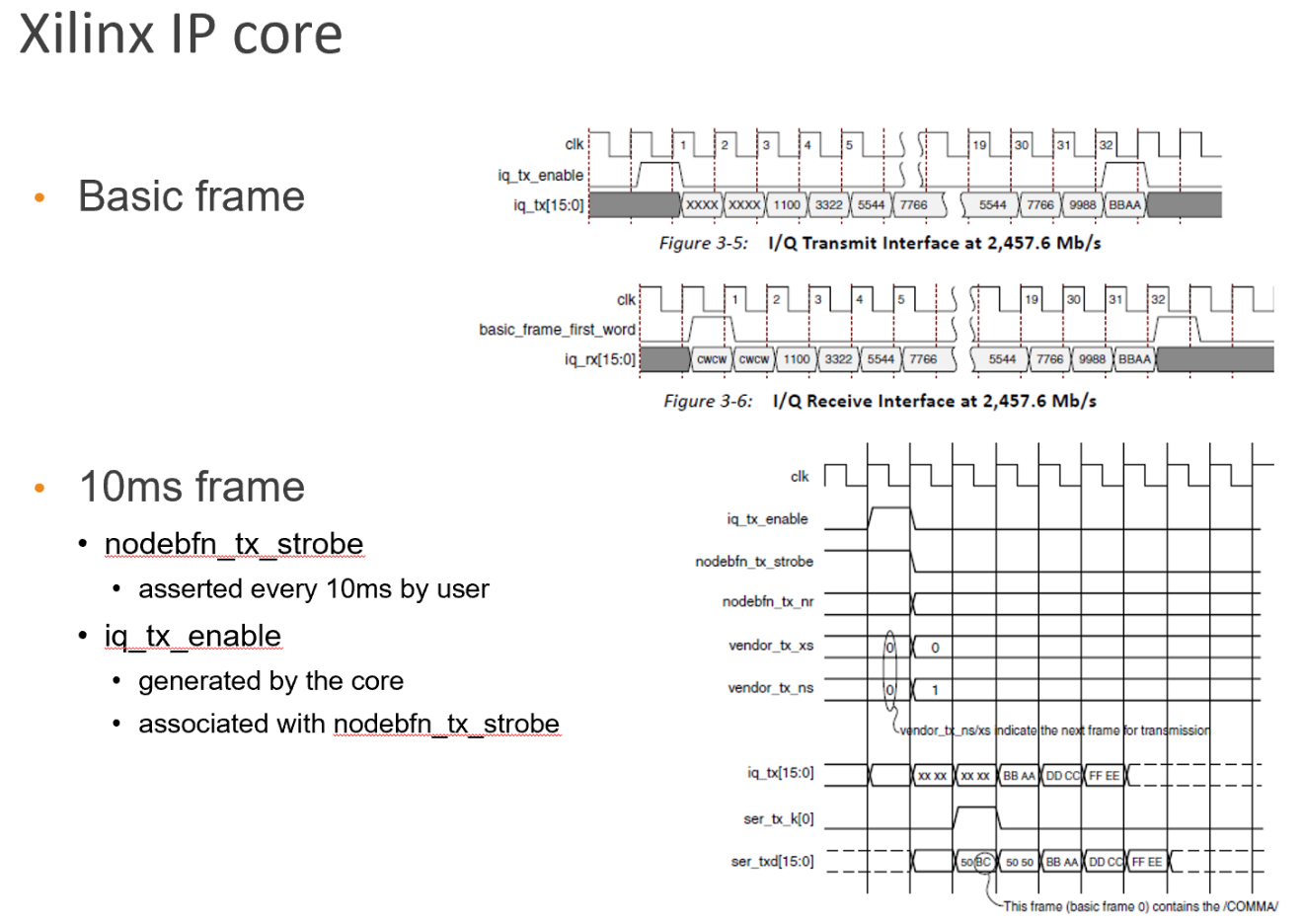

于是,我们结合Xilinx IP,看下CPRI是如何收发数的。由于CPRI是一个完全同步的系统,用户在使用CPRI IP的时候,需要主动每隔10ms,给IP一个nodebfn_tx_strobe输入。IP会根据用户此输入,对应每隔一个基本帧的时间,给出一个iq_tx_enable输出。

基本帧的开头几个bytes为control words,来自于各个对应控制数据接口;用户不用在IQ数据接口(iq_tx,iq_rx)管这几个数,后面则是正常的IQ数据收发。

了解了CPRI的数据业务如何使用之后,再来看下CPRI的初始化流程。

CPRI IP支持自协商,根据用户选择的IP的可支持速率,从高到低依次下降,与对方互通,直到通信成功为止。

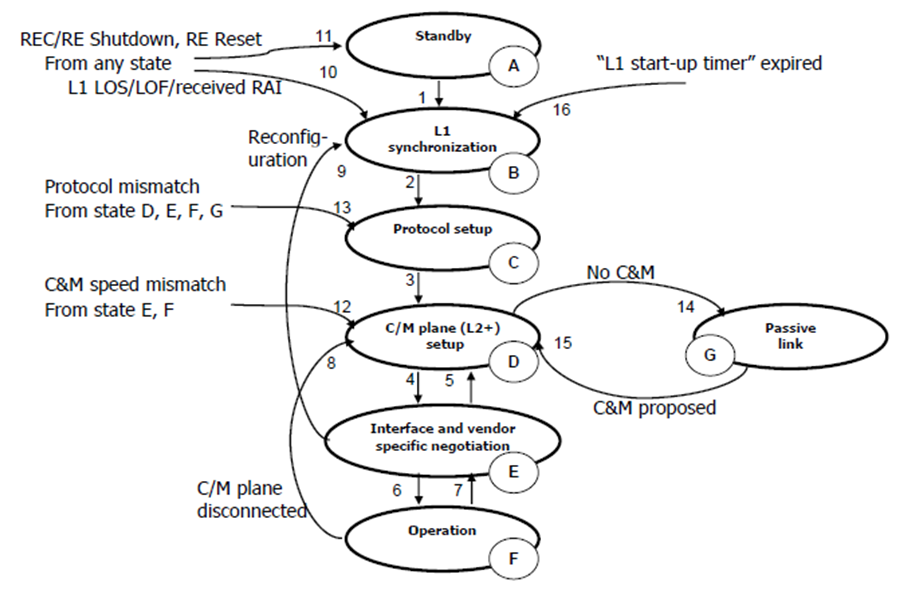

初始化状态机的运行可以观察IP的stat_code[3:0]输出信号。该状态机参考CPRI协议设计,如下。因此其具体细节,建议直接参照CPRI协议。

例如,如果初始化状态机卡在状态B不前进,那意味着此时IP无法实现与对端任何通信,可能是GT初始化有问题,或者link没有成功,可以先做下近端环回实验。注意,如果这是一个Slave的CPRI IP,需要先使能Slave Transmit Enable,再做环回。

或者卡在状态C的话,按照CPRI协议,是Protocol Setup两边没有对应上,需要检查IP的相关设置,或者看下两边收发的Z.2.0这个数是否是相一致。

最终,这个stat_code状态走到F或者G,IP达到了link状态,可以开始进行正常的业务数据收发工作了。