作者:Grace Sun,AMD工程师;来源:AMD开发者社区

仿真是设计流程中进行功能性能验证的重要步骤。Vivado IDE集成了Modelsim, VCS, Xcelium等第三方仿真器的目标选项,可以使用户直接从Vivado界面内启动第三方仿真器的仿真,这种方式自动化程度高,便捷且不易出错。但出于习惯,定制灵活性,验证环境等原因,很多用户会在Vivado IDE之外单独启动第三方仿真器用自己创建的脚本进行设计的仿真。对于包含有Xilinx IP的设计来说,由于IP涉及到的文件及库众多,没有一定的辅助,实际操作起来非常容易出错。本篇文章旨在帮助用户更深入理解IP的仿真模型及如何仿真。

IP仿真模型概览

大部分Xilinx IP只会生成单一语言的RTL源文件,也就是某些IP只提供Verilog的仿真文件,某些只提供VHDL仿真文件。Vivado工程选项里有一个Simulator Language的属性,默认值是Mixed,两种语言都可以支持,通常用户不需要去修改这个选项值,当你的仿真器license只支持单一语言时,可以通过调整这个选项(Verilog或者VHDL)达到匹配目标语言的目的。

下面这个表格罗列了不同情况下IP仿真模型的选用。

Simulator language和Target language的设置都在工程的Settings对话框里,如下图所示:

也可以通过Tcl命令进行设置,例如:

set_property target_language VHDL [current_project]

set_property simulator_language Mixed [current_project]

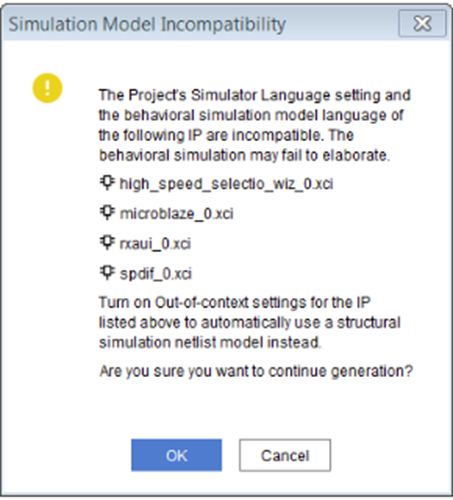

简而言之,只要IP有提供behavioral model,simulator language在Mixed的情况下总有对应的行为级模型可用。而当设置的simulator language与IP所能提供的模型语言不一致,无合适的behavioral model可用时,你会收到类似以下的弹出提示:

在保证OOC综合打开的情况下,工具会自动用IP OOC综合生成的综合后仿真网表来代替behavioral model进行行为级仿真。此网表以_sim_netlist.v|vhd命名,也就是所谓的Structural Model,在IP Output Product中可见。示例如下:

顺便提一下,这个structural model也可以由用户手动生成,即当你只有IP的综合后DCP时,可以用open_checkpoint导入dcp,在此基础上用write_verilog/write_vhdl导出综合后仿真网表。相关命令的具体用法请参考其帮助文档。

需要指出的是,在没有仿真语言限制的条件下,优先推荐使用behavioral model。structural model虽然文件单一,但会带来仿真性能和网表复杂度的影响。

为设计导出仿真脚本

Vivado提供了一条Tcl命令export_simulation来快速获取仿真所需要的设计文件,并为目标仿真器生成仿真脚本。

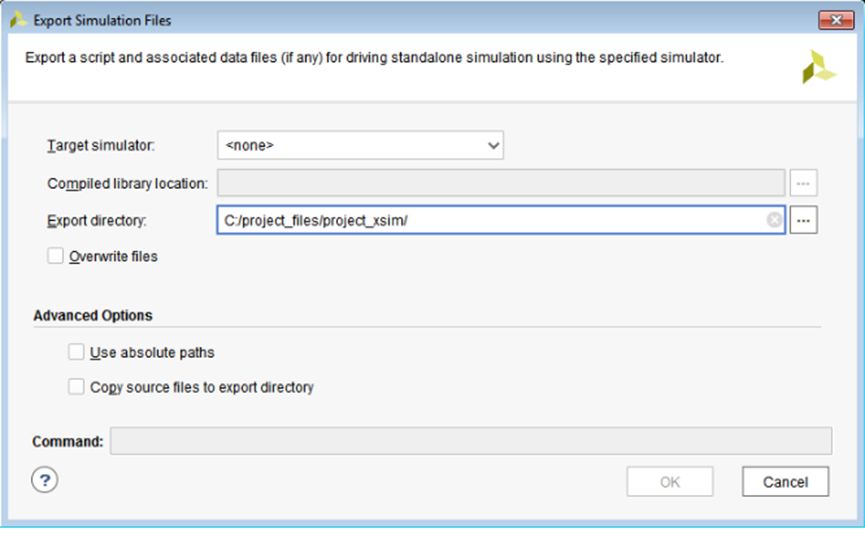

在Vivado IDE的工程模式下,你可以通过菜单File > Export > Export Simulation来启动此命令的对话框设置选项,如下图所示:

每一项选项的具体含义请参照帮助文档。在进行IP仿真之前,不可或缺的一步是用compile_simlib为第三方仿真器编译仿真库,从而可以设置compiled library location。

各选项设置完毕单击OK,会在Export Directory生成一级

以Questasim为例,会在<export dir>/questa/下生成compile.do,elaborate.do以及simulate.do脚本。除了生成do文件之外,工具还会自动拷贝一些仿真需要的文件,包括:

在单独启动的Questasim中,直接cd到目标文件夹,顺序执行compile.do,elaborate.do以及simulate.do就可以启动仿真。

export_simulation旨在帮助用户快速收集仿真所需的设计文件,并生成顶层 RTL 设计或子设计的仿真脚本。用户可以将其作为一个蓝本,按需编辑修改,合入整体的仿真定制脚本中。有几点提醒注意:

1. 它不会从当前工程中读取属性来查询 Verilog宏定义和包含目录,而是仅从export_simulation选项获取指令。如有特定编译选项需求,必须手动编辑生成的脚本,指定适当的选项才能获得所需的结果。

2. 在做导出前,请确认工程中的IP和BD均已成功完成generate output product操作,如果export_simulation获取不到相关文件会报错。

另外需要提到的是,在GUI的工程模式下,利用Export Simulation Files对话框来导出设计的仿真文件,Vivado会自动在export_simulation之前先运行export_ip_user_files -no_script命令,以确保支持IP(core container以及非core container)和BD仿真的所有文件均可用。你可以在对话框点击OK后切换至Vivado底部的Tcl Console窗口,查看打印的实际运行的Tcl命令。

这里,工具指定-no_script选项是为了防止为顶层设计中使用的各个IP 和 BD 生成单独的仿真脚本,因为那样会显著增加命令的运行时间。

export_simulation 命令生成的脚本和文件指向 ip_user_files 目录中的文件。如果您不借助对话框而是手动执行export_simulation Tcl命令,那么也必须先运行export_ip_user_files命令,否则可能会出现仿真错误。

下面给出了对不同对象导出仿真脚本的示例Tcl命令:

导出顶层设计

要为顶层设计创建仿真脚本,请提供仿真文件集对象。 在以下示例中,sim_1 是仿真文件集,export_simulation 为设计中的所有 RTL 实体、IP 和 BD 对象创建仿真脚本。

export_ip_user_files -no_script

export_simulation -of_objects [get_filesets sim_1] -directory C:/test_sim -simulator questa

导出具体的IP或BD

以下命令中对象为IP:

export_ip_user_files -of_objects [get_ips blk_mem_gen_0] -no_script -force

export_simulation -simulator xcelium -directory ./export_script \

-of_objects [get_ips blk_mem_gen_0]

以下命令中对象为BD:

export_ip_user_files -of_objects [get_files base_microblaze_design.bd] -no_script -force

export_simulation -of_objects [get_files base_microblaze_design.bd] \

-directory ./sim_scripts

以下命令中对象为设计中所有的IP和BD:

export_ip_user_files -no_script -force

export_simulation -simulator xcelium -directory ./export_script

单个IP仿真文件和脚本的导出

上文提到,export_ip_user_files -no_script可以防止对单个IP生成仿真脚本。如果去除这个选项,我们也可以只运行export_ip_user_files命令来获取单个IP的仿真文件和脚本。

用法示例:

export_ip_user_files -of_objects [get_ips char_fifo]

其他的选项诸如-lib_map_path请参考export_ip_user_files -help。

以一个简单的FIFO IP为例,在导出文件夹下可以看到ip,ipstatic以及sim_scripts目录。

ipstatic包含IP不同定制共享的一些不变的静态文件,如fifo_generator_v13_2_rfs.v。ip文件夹包含其他动态生成的文件。

sim_scripts则是包含了为IP生成的仿真脚本。默认情况下,Vivado会生成所支持的所有仿真器的脚本。

以此自动生成的目标仿真器的脚本为参考,用户可以比较快速地定位IP仿真所需要的文件,库及编译命令,以便按需合入定制脚本中。

本文主要阐述了利用export_ip_user_files和export_simulation为顶层设计,IP以及BD创建目标仿真器的仿真脚本的方式,这可以在很大程度上减轻构建IP仿真脚本的工作量,有助于更高效地在第三方仿真器中运行含有IP设计的仿真。