作者:Meng Fancheng,AMD工程师;来源:AMD开发者社区

MSIX中断介绍

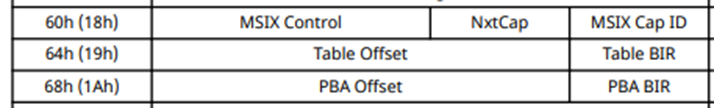

不同厂商的MSI-X结构所在配置空间的位置不同,如图1所示,XILINX Versal 系列PCIE IP MSIX结构的起始地址为60H,是否支持MSIX功能以及MSIX Table Offset,PBA Offset,Table BIR和PBA BIR等字段内容都是由硬件决定的,但是是否使能MSIX功能,以及MISX表的内容通常都是由软件决定的。如果要使用MSIX功能,则必须要确认MSIX功能已开启,如果未使能则需要使用setpci指令打开此功能。有些驱动成功加载后会自动使能此功能,例如Xilinx的QDMA驱动,因为QDMA是必须要使用MSIX中断的,所以当某个PF使能DMA功能,又成功加载了qdma驱动,该PF的MSIX功能就是开启状态。

图1 MSI-X 功能结构

对于msix功能的结构,用户需要关注MSIX Control, Table Offset,PBA Offset,Table BIR和PBA BIR。Xilinx中的MSIX Control对应于PCIE协议中的Message Control字段,Message Control字段的定义如图2所示,Function Mask不需要额外配置,其默认值为0,如果将此bit位设置为1,会将MSIX的vector都进行屏蔽。Table size指的是MSIX table的大小,由硬件决定,软件无权限改写。第15 bit位MSI-X Enable是最需要关注的一个bit位,当在硬件在选通MSIX功能时,并不意味着 MSIX功能处于开启状态,因为在PCIE协议中,MSI-X Enable的默认值是0,即此功能在默认状态下是关闭状态,需要软件使能此功能和bus master功能后,硬件才能成功向主机侧发送中断。

图2 MSI-X的控制信息字段

通过检索MSI-X表所在的BAR和偏移地址,即可找到表映射到的存储器地址,协议规定表所在的bar的偏移地址必须映射到了存储空间中,后续驱动需要将MSIX table写到此存储器中。硬件需要读取此表的内容来填写memory write的TLP包,如果MSIX表未映射存储器的某个地址段,硬件则读取不到表的内容,此时如果拉高IP的发送中断信号,IP有可能会发送一个地址和data都为0的memory write包,此时主机在接收到此包后也无法将其识别为产生中断的包。

图3 MSI-X表偏移地址/表所在的BAR

MIS-X表的结构如图4所示,其中的Msg Addr表示的是MSIX vector的低32位地址,为了保证双字对齐,Msg Addr的前两个bit必须为0。Msg Upper Address表示的是MSIX vector的高32位地址,此字段全为0时表示只使用了32位地址。Message Data表示的是MSIX vector的数据字段,PCIE在发包时,地址是根据Msg Addr和Msg Upper Address填写的,包的数据是根据Message Data填写的。Vector Control的0bit是Mask bit,如果此bit置为1,可以将此vector mask住,通常来说Vector Control可以全填0。

图4 MSI-X表结构

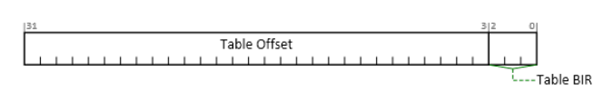

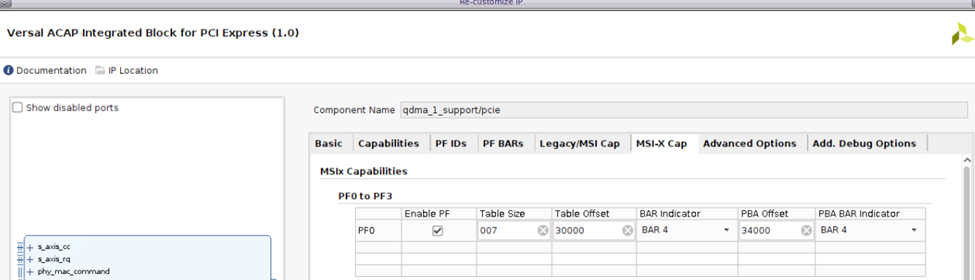

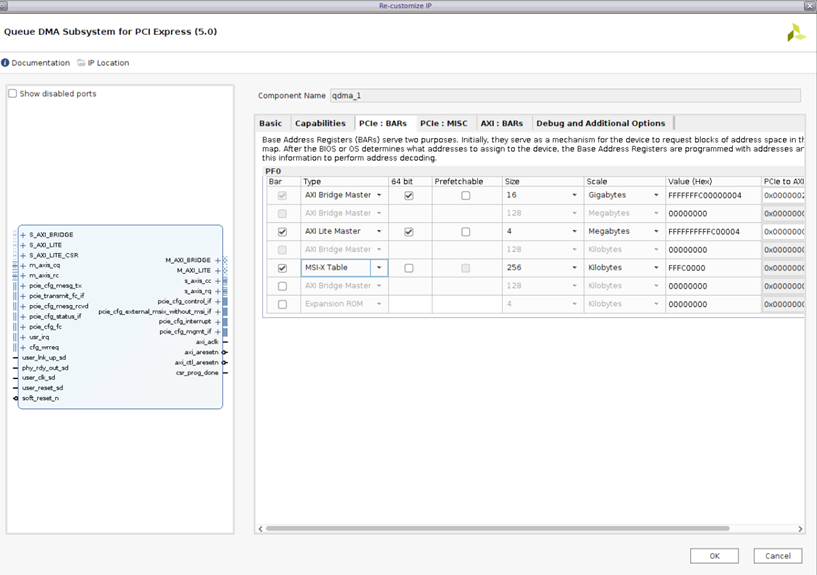

AXI Bridge IP的配置

在打开VERSAL的QDMA IP后,将Functional mode改为AXI bridge模式,点击PCIe :MISC配置页,如图6所示,在MSI-X Capabilities选项中,勾选需要使用MSIX 功能的PF。之后需要打开PCIe: BARs配置页,如图7所示,将PCIE的某个bar选择为MSI-X table,AXI Bridge默认使用的是MSIX external without MSI模式,至于MSI-X表和PBA的偏移地址则需要在IP界面配置,如图5所示。

图5 MSI-X cap配置页

图6 PCIe :MISC配置页

图7 PCIe :BARs配置页

MISX中断的生成

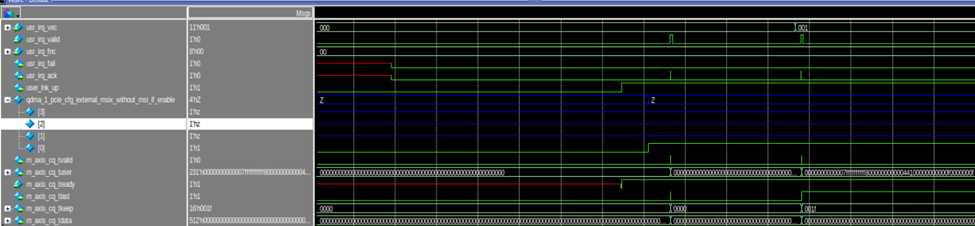

在生成中断时,需要将usr_irq_vec进行赋值,当usr_irq_vec的值为0时,对应的就是表4的entry0,修改usr_irq_vec的值即可产生对应于不同entry的中断,同时拉高usr_irq_valid即可控制产生中断,当IP成功发送中断后,usr_irq_ack会拉高,如图8所示。如果IP未能成功发送中断,usr_irq_fail会拉高,用户需要检查msix_enable信号在PCIE link up后是否被RP使能,如果PF0的msix被使能,那么如图8所示,qdma_1_pcie_cfg_external_msix_without_msi_if_enable的0 bit会拉高。

图8 MSIX中断仿真图