1 DP(DisplayPort)接口介绍

DisplayPort是由美国视频电子协会(VESA)在2006年5月提出的一种新型的数字显示接口规范,旨在支持内部和外部数字显示器连接。

DisplayPort图像显示接口不仅传输率高,而且可靠稳定,其接口传输的信号由传输图像的数据通道信号以及传输图像相关的状态、控制信息的辅助通道信号组成,具体包含DisplayPort数据传输主要通道(Main Link)、辅助通道(AUX Channel)与连接(Link Training)。

DisplayPort 的外部应用包括 PC、显示器和投影仪之间的显示连接,还适用于高清内容应用程序(如光驱播放器、移动设备、个人录像机和电视)之间的连接。

2 智多晶SA5T-100 FPGA介绍

2.1 SA5T-100 FPGA概述

西安智多晶微电子有限公司的SA5T-100 FPGA属于Seal(海豹)5000系列器件,本系列器件建立在一个优化、高性能28nm工艺基础之上。通过使用低成本设计,并将新架构与多个优化功能的嵌入式模块融合来实现高速FPGA,使系统设计师在降低成本的同时又能够满足不断增长的高性能应用要求。对无线和有线通信、工业控制,图像处理,人工智能,数据处理中心及云信息等行业中的低功耗,高性能的大小型应用,本系列FPGA无疑是最理想的选择。

2.2 SA5T-100 FPGA特性

超大的逻辑资源

⚫ 101,978等效逻辑单元

⚫ 多达300个用户I / O

高性能可编程逻辑单元

⚫ 采用6输入查找表(6-LUTs)

⚫ 双5-LUTs选项

低功耗器件

⚫ 先进28nm高性能铜CMOS工艺

⚫ 核电压1.0V

嵌入式和分布式存储

⚫ Fmax = 500 MHz

⚫ 嵌入块存储容量为18Kbit/36Kbit, 总容量高达5,616Kbits

⚫ 高达2,040Kbit的分布式存储

增强的乘法器块

⚫ Fmax = 500 MHz

⚫ 内置多个9x9/18x18/25x18具备预加法的串行乘法器, 算数逻辑单元(ALU),两层叠加实现DSP处理密集型应用

灵活的片内时钟

⚫ 最多32个全局时钟

⚫ 高达24个延时锁相环(DLL)用于高速I/O接口

⚫ 高达7个内置通用PLL、提供倍频、分频、相位转移、展频等系统时钟

⚫ 精度为±5%的片上振荡器

集成高速串行接口(SerDes)

⚫ 集成2个4通道高速SerDes

⚫ 数据速率6.6 /10.3 Gbps

3 智多晶DP IP规格介绍

⚫ 支持TX/RX controller

⚫ 支持VESA DisplayPort Standard V1.1a and V1.2a.

⚫ 支持1、2、4 lanes

⚫ 支持每lane线速率1.62、2.7、5.4Gb/s.

⚫ 支持1、2、4像素宽度接口

⚫ 支持RGB、YCrCb像素格式,色彩量化位宽最高支持16bit

⚫ 支持1 Mb/s AUX通信

⚫ 支持eDP与DP接口

⚫ 支持自定义EDID

⚫ 支持最高4K@60Hz显示

⚫ 支持APB控制接口与Native图像接

4 DP DEMO介绍

4.1 DP DEMO程序结构

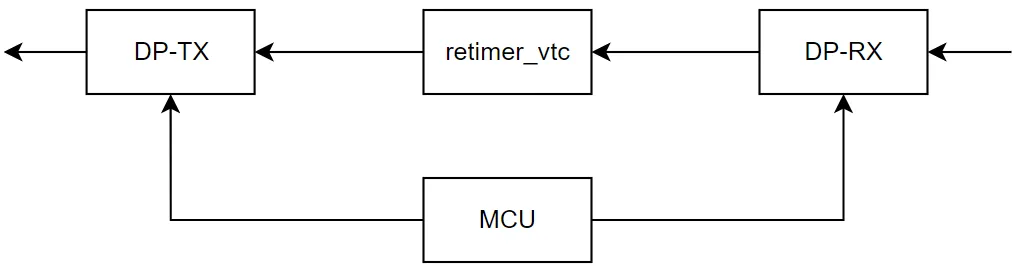

DEMO逻辑部分由DP TX/RX Controller、retimer_vtc与MCU构成。

retimer_vtc:缓存一行RX Controller输出的图像数据,保证TX Controller输入的每一行图像数据都是完整的。

MCU:实现对DP TX/RX Controller的初始化配置,同时也负责控制整个DEMO的工作流程与调试信息的打印。

图2-1 DEMO程序结构示意图

4.2 DP DEMO硬件结构

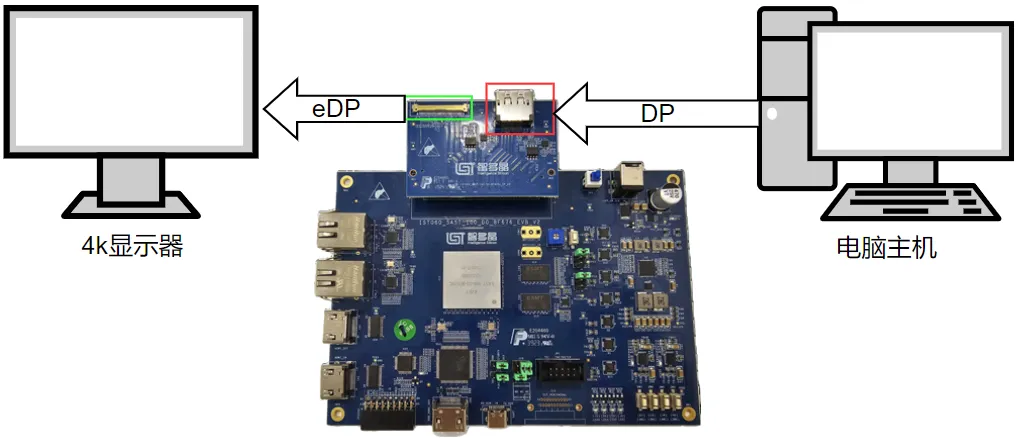

DP DEMO使用智多晶IST060_SA5Z_100_D0_8F676_EVB_V2开发板作为底板,经过FMC接口外接IST060_SA5Z_100_D0_8F676_DP_V3子板,子板搭载了DP与EDP接口。

显示屏使用京东方(BOE) MV270QUMNM1 4K@60Hz显示屏。

图2-2 DEMO硬件结构示意图

5 DP DEMO演示

智多晶DP IP简介 Version 1.0 版本于2024年6月4日首次发布。

版权所有©2023 西安智多晶微电子有限公司

未经本公司书面许可,任何单位和个人都不得擅自摘抄、复制、翻译本文档内容的部分或全部,并不得以任何形式传播。

文章来源:智多晶