oneAPI基础工具套件大大提升了硬件开发效率。它使得以SYCL*(C++)编写的软件内核能够在FPGA硬件中快速实施,彻底改变了为FPGA开发IP模块的方式。

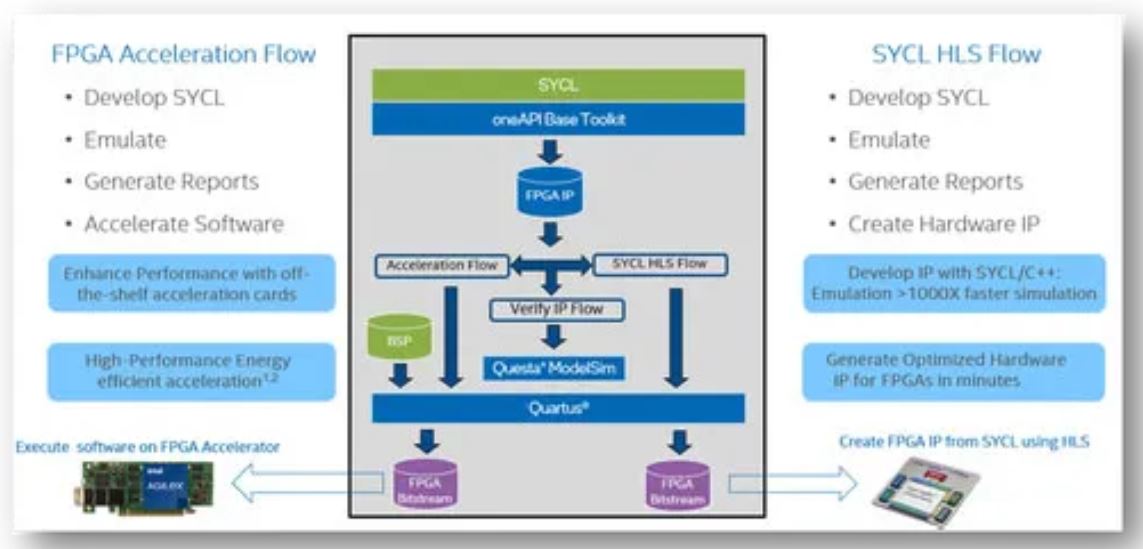

oneAPI标准实施方案支持多种开发流程,也为FPGA提供了两种不同的开发流程。

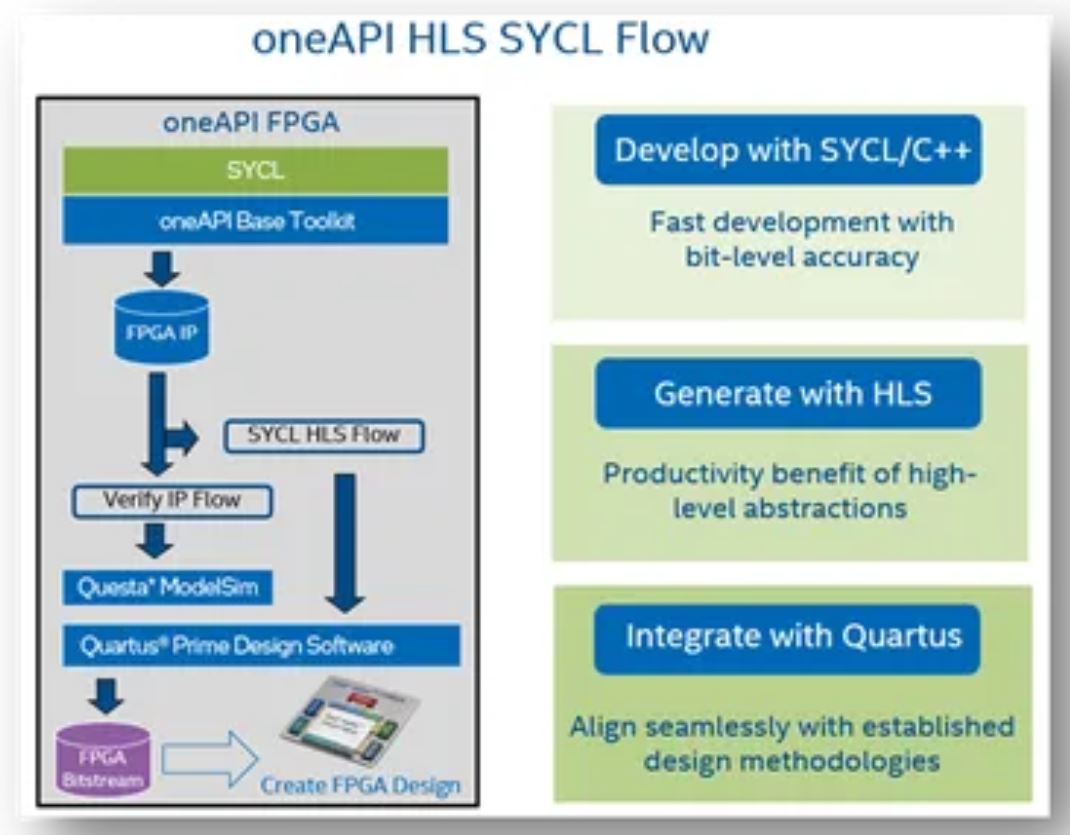

在FPGA加速流程中,oneAPI为软件算法提供运行时加速,其目标是FPGA加速平台。 在SYCL HLS流程中,oneAPI可针对FPGA设备生成优化的RTL IP模块并直接导入Quartus® 硬件开发环境。

本文主要介绍如何使用SYCL HLS流程在Quartus® 中进行RTL IP开发。已经在使用Quartus® 的用户只需安装oneAPI基础工具套件,即可开始使用该流程。

充分发挥高层次综合的IP开发能力

在当今快节奏的世界里,在Quartus® 中利用oneAPI和高层次综合(HLS)开发知识产权(IP)已经成为一项基本策略。

HLS是一种将高级编程语言(如C、C++、SYCL等)转换为硬件描述语言的过程。在Quartus® 中使用HLS进行IP开发,可以带来诸多效率方面的优势,包括实现快速上市、简化开发流程等,这对于技术密集型企业提升利润意义重大。

提高效率:与Verilog或VHDL等传统硬件描述语言(HDL)相比,HLS让设计人员能够以更高的抽象级别描述硬件行为,从而加速开发周期。

加速原型设计:HLS可加速原型设计和迭代,使设计人员能够快速进行测试、修改设计。使用SYCL,在不到1分钟的时间里就可以编译和验证一个典型的位精确算法,从而实现比RTL仿真更快的设计迭代。 减少错误:更高的抽象级别可以减少低级错误的发生概率,从而提高设计的稳定性。

提高资源管理效率:HLS可优化硬件资源,从而提升设计效率,尤其是在面积和功耗方面。

增强设计探索:HLS提供自动探索不同架构方案的功能,帮助设计人员在性能、面积和功耗之间找到理想的平衡点。

提高代码复用性:高级代码可以更方便地在不同项目中重复使用,从而减少创建新IP内核所需的工作量。

自动RTL验证:HLS生成的IP模块包括RTL测试台,可自动从源代码中提取激励和结果,从而使用RTL仿真来创建并自动验证IP。

无缝集成:您可手动或通过平台设计器实现HLS实施方案和oneAPI与Quartus® 的无缝集成,实现设计、仿真和综合之间的平滑过渡。 在Quartus® 中使用oneAPI和HLS进行IP开发是一种具有变革意义的方式,可以简化流程,提高效率,对于希望在当今市场保持竞争力的科技企业而言是一项必备策略。

如果您已准备好探索oneAPI流程或开始使用oneAPI进行开发,我们将为您提供丰富的资源,其中包括:

从工具安装到在FPGA上运行新RTL IP的全流程自学视频;

将现有C和C++算法轻松转换为SYCL的指南;

以FPGA为重点的oneAPI文档;

40多个有关常见性能建模技术的教程示例;

来自多个细分市场的设计参考示例。

这些资源将帮助您快速评估使用oneAPI的IP开发,助您顺利起步。

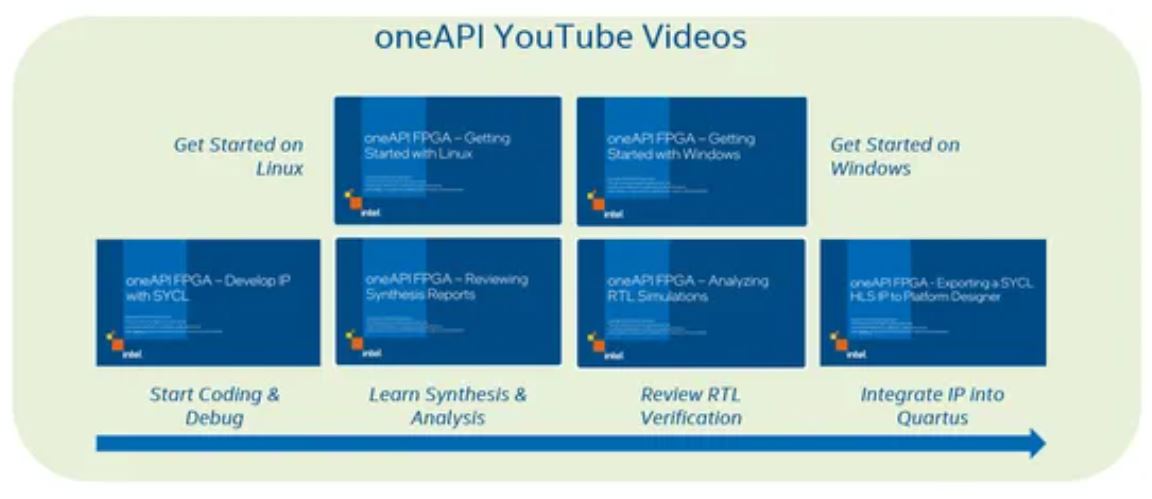

oneAPI学习视频助您快速入门

要开始在Quartus® 中使用oneAPI进行IP开发,一个快速的方法就是直接在YouTube上访问频道。

这些简短的oneAPI FPGA视频全面介绍了从安装工具到调试、综合以及可选的RTL波形深入分析等内容。您将了解oneAPI如何用于快速生成优化的RTL IP、如何自动创建RTL测试台,以及通过CPU进行选择性控制需要哪些软件驱动程序。

了解如何在Linux或Windows操作系统上安装用于在Quartus® 中进行FPGA开发的oneAPI、如何启动oneAPI并运行和调试代码示例。

了解如何使用SYCL在Quartus® 中设计IP,进行快速模拟以确认功能正确性,并调用调试器进行详细分析。

了解如何使用oneAPI在Quartus® 中生成RTL IP并查看综合报告。您将了解如何查看设计性能和面积资源,以及如何使用循环和系统查看器执行瓶颈分析。

了解如何验证oneAPI生成的RTL与综合前的SYCL源结果相匹配,并了解如何对RTL波形执行可选的详细分析。

查看从SYCL到FPGA的完整示例。了解如何使用SYCL设计IP并将其导出到平台设计器,从而在Quartus® Pro项目中加以使用。您将了解如何通过控制状态寄存器(Control Status Register) 从CPU控制IP,以及如何在FPGA板卡上运行IP。

了解上述流程后,您还可以通过40多个教程示例获得实操经验。

参考教程示例,使用oneAPI提升效率

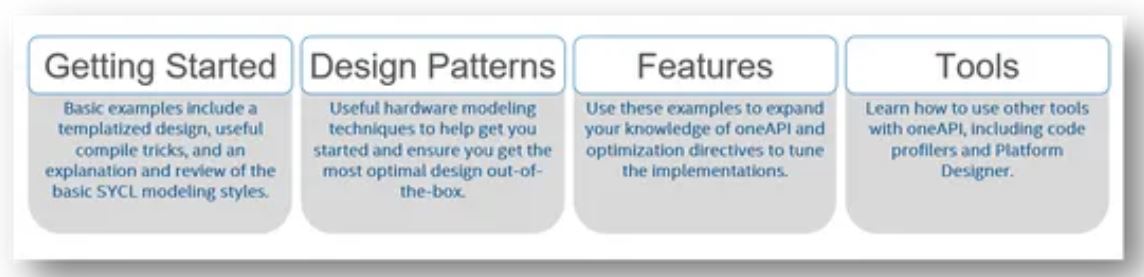

教程示例展示了如何使用SYCL对FPGA硬件进行轻松建模,以及如何使用优化指令实现仅凭源代码无法推断得出的特定硬件行为,如I/O端口实现和协议。这些示例可分为四类。

入门示例展示了运行oneAPI进行FPGA开发的基础知识。这些示例包括FPGA编译示例(FPGA Compile Sample)。这类示例展示了不同风格的相同设计模型,以突出同时支持functor和lambda SYCL建模风格以及通用共享内存(USM)的优势。

设计模式示例将带您了解如何轻松建模并将常见的设计模式纳入IP模型,包括双缓冲和N路缓冲、三角循环、片上内存缓存、零拷贝数据传输等。

我们还提供了多个功能示例,帮助您学习oneAPI优化技术,如循环融合、管道、优化目标和停顿启用。这类教程还介绍了在SYCL中使用任意精度和定点位宽进行设计的方法。

您还可以了解有关如何使用oneAPI的其他工具,尤其是如何使用平台设计器的详细教程。

这些教程示例将帮助您快速提升效率:您可使用模板示例快速开始高效的工作流程,迅速了解哪种SYCL建模风格更符合您的需求或个人风格,直接从工作代码中将有用的建模结构复制到您的IP中,并学习使用其他工具来提高您的整体工作效率。

使用oneAPI参考示例,学习如何提高性能

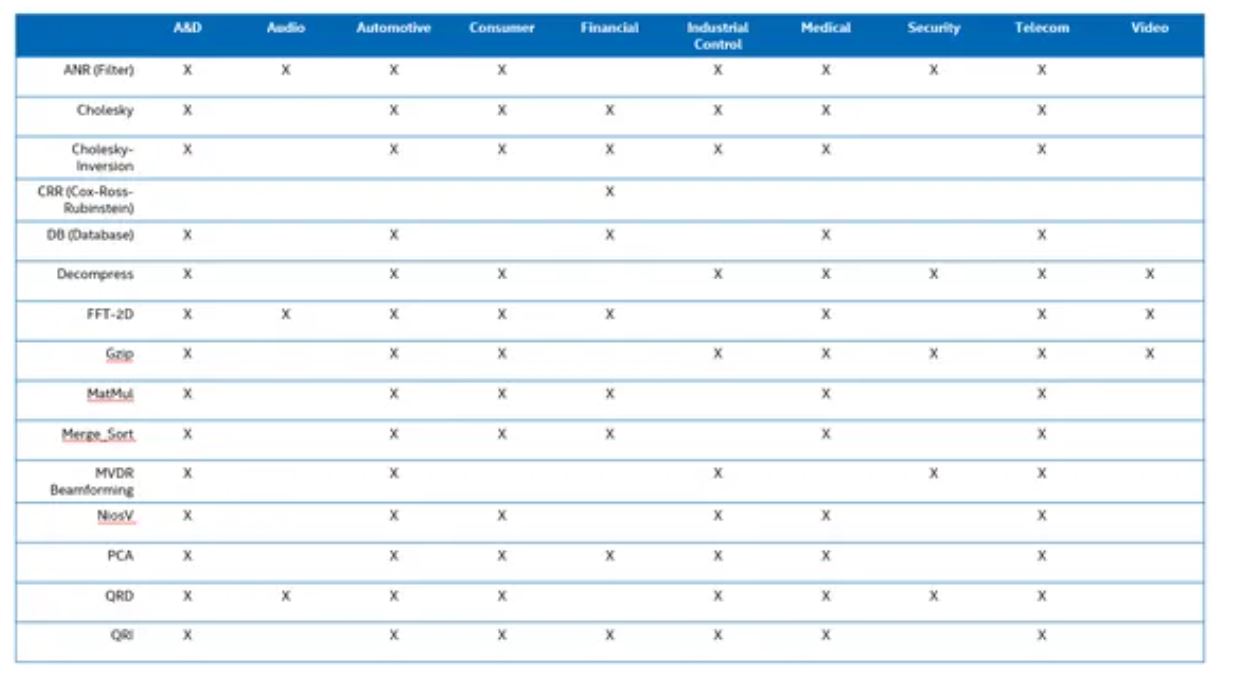

当您需要将设计扩展到高性能、小面积的硬件IP时,我们也为您提供了多个细分市场的完整设计参考示例。请注意,这些示例也可能适用于所示示例之外的其他细分市场。

这些参考设计可以为您设计复杂的高性能IP提供理想起点。如果您想使用这些良好实践和示例来扩展您的设计示例,我们还另外提供了一整套以FPGA为重点的文档。

全面统一的oneAPI FPGA手册

oneAPI FPGA手册是开发人员探索基于oneAPI开展FPGA开发的重要资源。无论是新手还是经验丰富的开发人员,其全局视角都提供了非常清晰的路线图。

该手册首先介绍了FPGA设计概念。这部分内容对于刚入门FPGA编程的开发人员至关重要,因为它介绍了FPGA硬件概念以及oneAPI如何将您的SYCL代码转换为FPGA应用。

接下来,手册深入介绍了基于oneAPI的FPGA开发流程。这一部分又细分为多个子小节,涵盖从FPGA开发流程概述到内核功能正确性验证的所有内容。每个子小节都为不同的开发阶段提供了详细的指南和技术介绍,帮助您全面了FPGA开发流程。 “基于oneAPI的FPGA开发”部分概述了FPGA开发流程。 “为FPGA定义内核”部分提供了内核代码编写指南。 “优化内核”部分概述了优化内核性能的方法以及您可以检查哪些内核代码以提高性能。 “设计分析”部分提供了在不使用硬件运行内核的情况下分析内核设计的工具和技术信息。在针对FPGA硬件编译内核之前,您可使用这些工具和技术来确定可以优化或调整内核的哪些部分。 “设计调试和验证”部分介绍了用于验证内核功能正确性的工具和技术。 “将RTL IP内核集成到系统”部分提供了将oneAPIDPC++/C++编译器生成的RTL IP内核集成到更大的FPGA设计的相关信息。 “优化区域”部分讨论了特定区域的优化,如循环、管道和内存操作。对于希望大幅提高FPGA应用性能的开发人员来说,这是一份宝贵的资源。 手册还讨论了在内核中使用库和从内核生成库的问题,这是开发人员有时会忽略的一个重要方面。 为帮助开发人员全面理解,该指南还提供开发IP时的其他考量因素,为FPGA开发流程提供了更多细节。 最后,手册还囊括了参考资料部分,其中列出了编译器优化标志、属性、pragma指令和扩展。这些参考资料对开发人员快速了解FPGA特定属性、pragma指令和变量很有价值,能够使开发流程更加顺畅高效。 相关技术可能需要支持的硬件、特定软件或服务激活。 没有任何产品或组件是绝对安全的。 您的成本和结果可能会有所不同。 性能因使用、配置和其他因素而异。更多信息请见 https://www.intel.cn/content/www/cn/zh/products/details/fpga.html 。 文章来源:英特尔FPGA