随着终端行业的快速发展,市场对于高性能、灵活可编程的解决方案需求愈发迫切。作为 FPGA 领域的创新者,易灵思最新产品16nm 钛金系列新成员—TJ375,经过近三个月的验证、测试工作,已做好准备面向市场。这款产品的面世正契合了当前市场的需求趋势,期待为各个领域带来创新与突破。

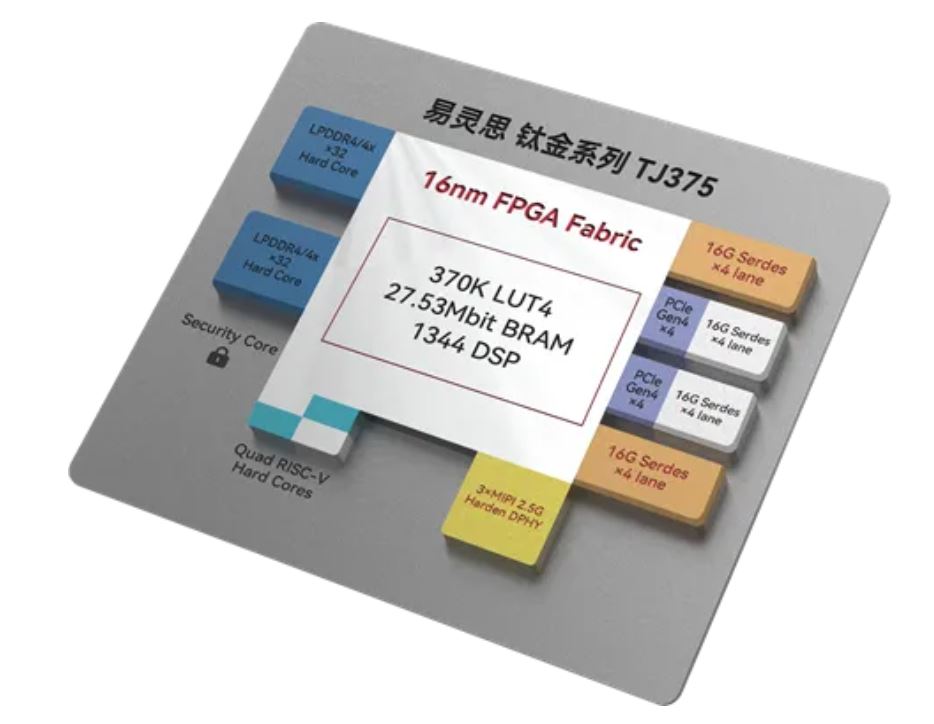

产品概览

TJ375 FPGA基于16nm标准工艺,在功耗、性能、集成度、灵活性等方面做了权衡优化,具备优秀表现。

可提供370K逻辑单元,以及丰富的DSP和BRAM资源

支持16路16G SerDes接口及两组PCIE Gen4x4,进行高速接口通信

内嵌四核硬核RISC-V处理器,方便用户进行网络协议处理、Linux/FreeRTOS等系统操作

支持多组2.5G MIPI DPHY硬核,快速完成视频数据收发

支持2x32bit LPDDR4/4x硬核接口,速率可达3.7Gbps,提供了高存储带宽、以及便捷使用的优势

低功耗特性:

·四核RISC-V@1GHz:~400mw

·PCIE Gen4x4:0.75w@25°C

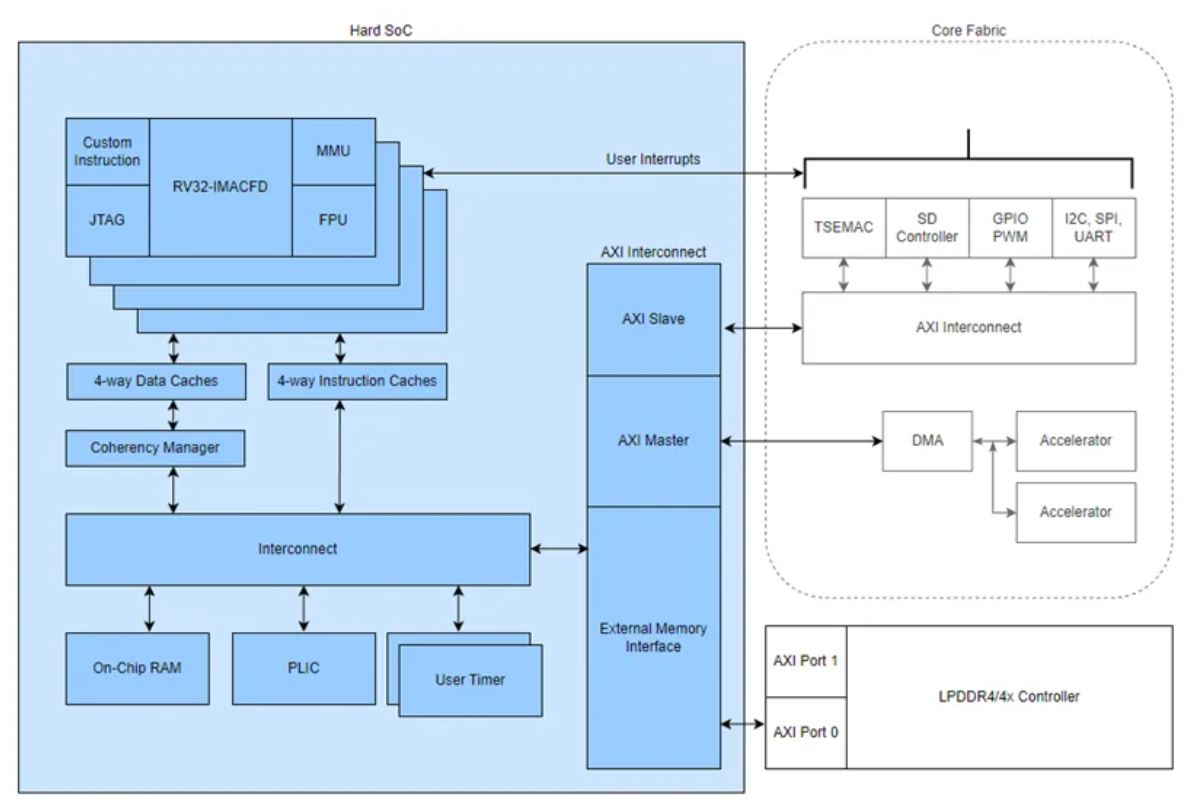

硬核4x RISC-V SoC模块

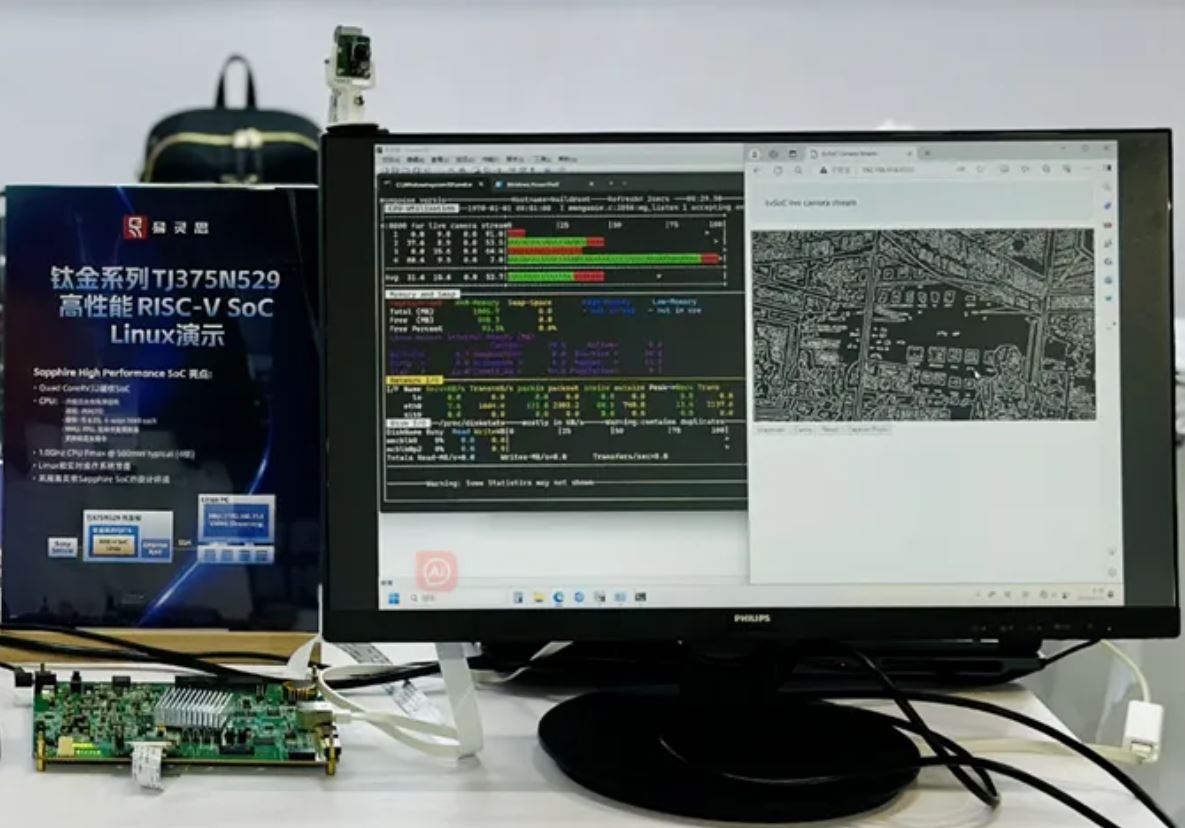

借助开源的VexRISC-V,易灵思自主优化了其内核架构,并在TJ375中实现4核处理器内嵌,无知识产权及授权期限等风险,客户可放心使用。目前基于TJ375N529开发板,已可实现Bare Metal/FreeRTOS/Linux系统搭建。

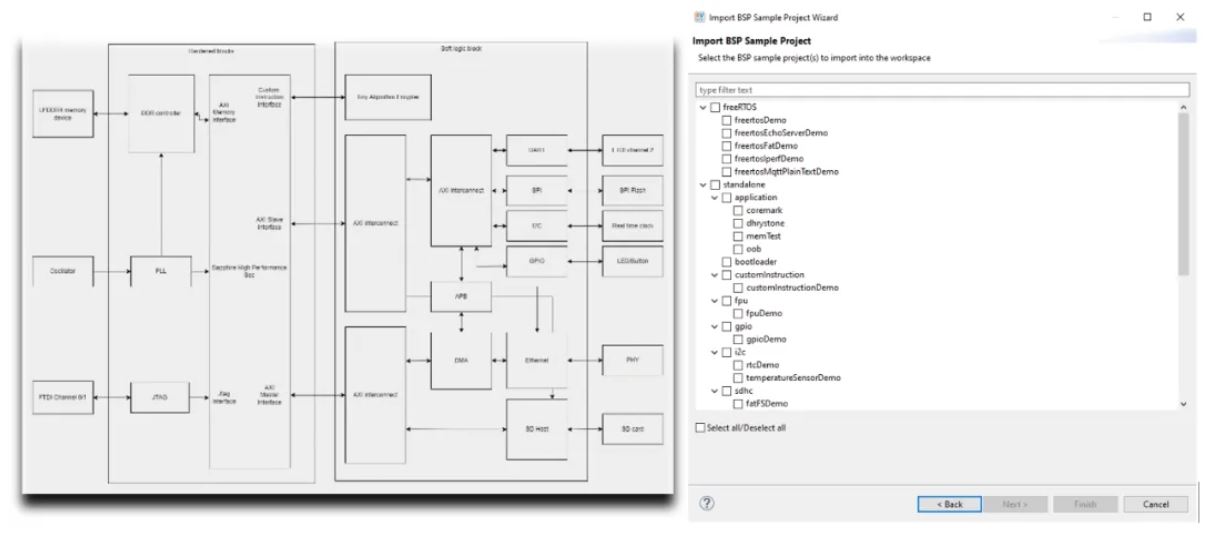

硬核RISC-V与Fabric交互架构概览

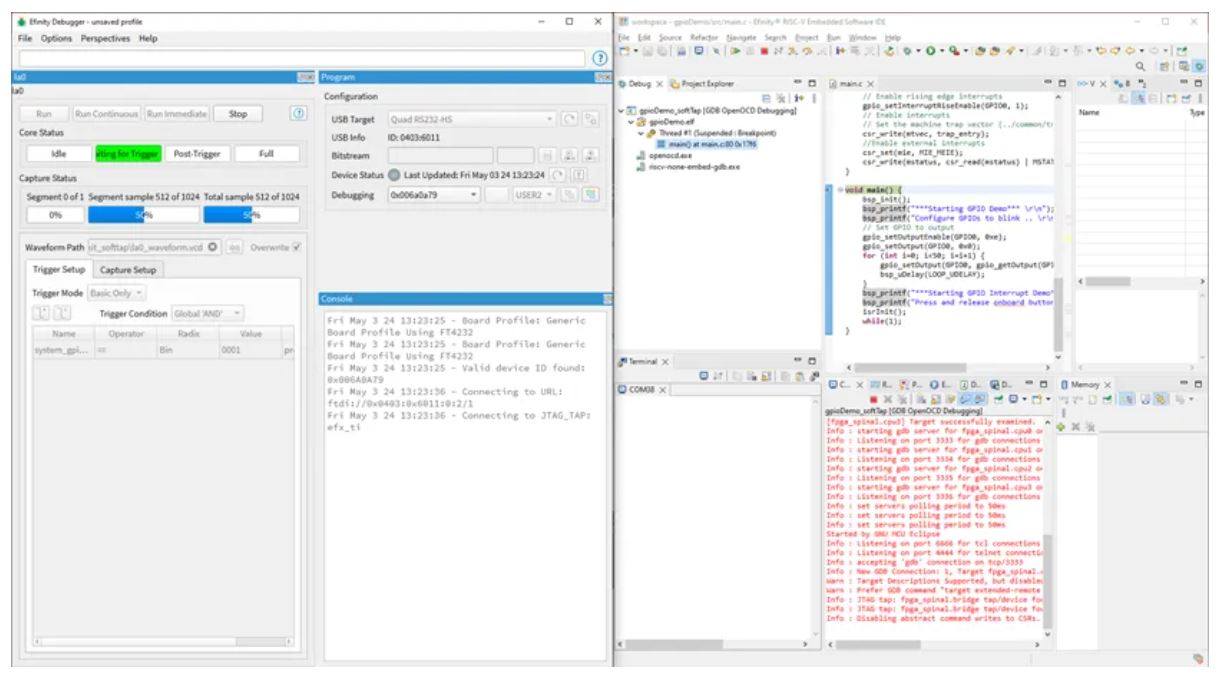

软件支持方面,易灵思已发布最新版本2024.1,能够支持RISC-V+FPGA SoC模式下的全流程开发,并提供IP快速搭建功能,帮助用户更加便捷的进行RISC-V接口外设、总线搭建,以及自定义指令开发。

RISC-V开发工具+Debugger示意

IP manager自动搭建RISC-V系统框架

16Gbps收发器模块及PCIE Gen4

TJ375支持16对16Gbps SerDes接口以及两组PCIE Gen4x4协议接口,为高带宽通信提供充足支撑。基本特性:

为4x Quad结构,每组Quad中包含4对SerDes通路,速率范围覆盖1.25G至16G

每个Quad中支持两组独立的参考时钟,可实现同Quad中不同速率/协议的通信需求

支持 PRBS and Loopback

通过APB接口可支持动态配置

提供Transceiver debugger tool眼图工具

硬件层面进展喜人!目前基于两片TJ375N1156X EA测试板卡,对PCIE Gen4进行回环测试,眼图效果良好。

软件层面步伐稳健,在发布初步支持PCIE Gen4的眼图工具后,将持续完善功能,并针对更多IP协议提供眼图测试功能。

TJ375N529开发板预售

TJ375N529开发板已可发售,用户可进行:

快速验证4核硬核RISC-V处理器,性能可达1GHz

验证自定义指令设计

提供硬核LPDDR4x控制器:100Gbps+外部存储带宽

RISC-V Embedded Software IDE,Debugger,Driver,and Embedded software 支持裸跑(Bare Metal)、FreeRTOS以及Linux系统搭建

提供TinyML AI Inference platform支持

支持Triple Speed Ethernet, SD Card, Real Time Clock

提供FMC、QSE、PMOD 连接器支持其他外设(暂不支持SerDes接口)

TJ375N529开发板正面图

TJ375N1156X开发板前瞻

预计在2024年8月中旬发布可以支持SerDes高速接口验证的TJ375N1156X开发板,敬请期待!

总结

易灵思16nm TJ375 FPGA已完成各项主要功能模块验证,欢迎各行业客户咨询、指导。同时希望与业界合作伙伴建立双赢的生态合作,包含高速IP及RISC-V开发等。

易灵思始终以低功耗、高性能FPGA产品创新为己任,以快速走向市场、服务客户为荣耀,为共创国产半导体生态而努力。

文章来源:易灵思官微