随着科技的飞速发展,CPU和GPU的集成趋势日益明显。如今,我们不仅能看到集成了GPU核心的CPU,还有配备了专用AI加速器的处理器。在这一浪潮中,AMD的高端GPU通过采用MCM技术,巧妙地将多个处理芯片或核心汇聚于一个封装之内,而其中扮演关键角色的,便是一个独立的I/O Die模块。这个名为“I/O Die”的组件,正逐渐在技术领域大放异彩。

I/O Die简介

I/O Die通常指的是一种特定功能的芯片,它集成了输入/输出功能,用于处理与外部设备的数据传输。I/O Die(输入/输出芯片)概念并非某家公司独创,而是伴随着半导体行业多芯片模块(MCM)和3D集成技术的进步应运而生。值得一提的是,AMD(Advanced Micro Devices)作为业界先驱,是最早采用并推广这一概念的公司之一。

核心与I/O分离的优势

将处理器核心与I/O功能分离,为系统设计带来了诸多益处:

分离核心和I/O的开发流程允许设计者专注于CPU核心的最小化,从而减少芯片的物理尺寸和制造成本。这种优化有助于提高生产效率和良品率。

通过专注于CPU核心的设计,可以更有效地实现更高的时钟频率和更优的微架构,从而提升处理器的性能。

缩小CPU核心尺寸有助于降低功耗和热输出,因为更小的芯片面积可以减少电流在芯片内部的传输距离,从而降低能量损耗。

I/O Die 的常见应用

在AMD的产品线中,例如其EPYC服务器处理器,其中包括一个中央处理器复合体(CCD)和多个输入/输出复合体(IOD),后者可以视为I/O功能的实现。AMD EPYC(霄龙)嵌入式 9004 系列包含PCIe 5 和 Memory 。

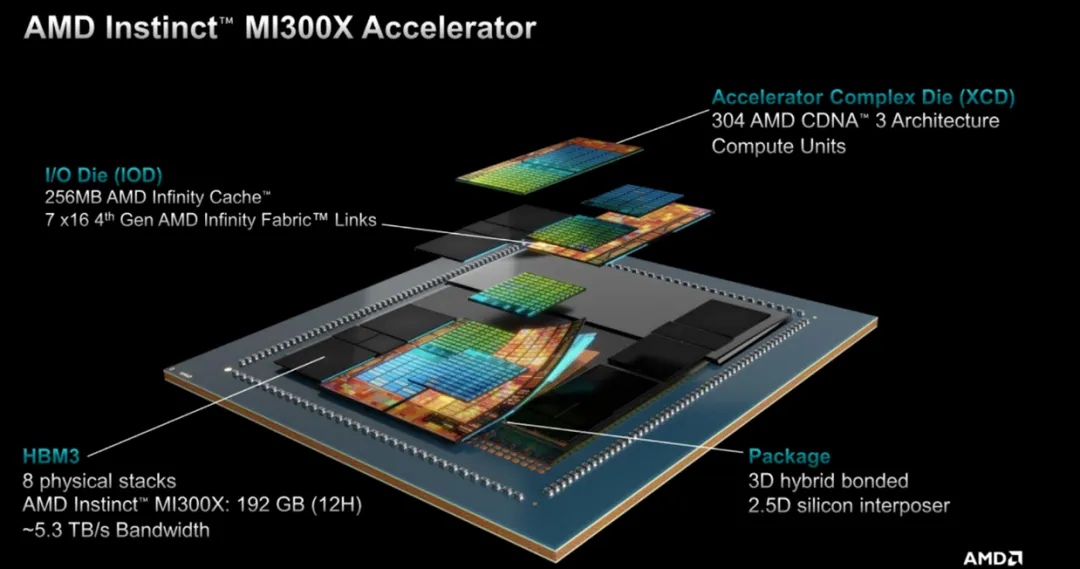

AMD的Instinct GPU MI300也采用了I/O Die的模块。总共四个IOD提供了多达七条满血的第四代Infinity Fabric连接通道,总带宽最高896GB/s,还有多达256MB Infinity Cache无限缓存。

I/O Die允许为不同的应用场景定制I/O功能,满足特定市场的需求。这种灵活性使得产品可以针对特定任务进行优化。

I/O Die可以集成高速接口技术,如PCIe、USB或NVMe,提供快速的数据传输速率,满足现代应用对高带宽的需求。

I/O Die的模块化设计简化了开发流程,使得设计者可以独立更新或改进I/O功能,而不需要重新设计整个CPU。

I/O Die的设计使得它们可以轻松集成到各种系统架构中,包括多芯片模块(MCM),3D堆叠技术,为系统设计提供了更大的灵活性。

奎芯IODie产品ML100的创新举措

今年,奎芯科技准备投片的I/O Die产品ML100结合了UCIe IP和HBM IP,包含16个标准封装的UCIe接口与1个完整的HBM 控制器,其带宽约为1TB/s,与HBM3完美匹配(IO速度:6.4Gbps)。

UCIe(Universal Chiplet Interconnect Express)是一种开放的芯片互连标准,它为芯片间的高速通信提供了可能。UCIe的优势在于其高带宽、低延迟和可扩展性,这些特性使得它成为实现复杂系统级芯片(SoC)的理想选择。

高带宽存储器(HBM)技术以其高数据传输速率和大容量存储空间,成为AI和高性能计算的理想选择。HBM与AI算法的互补性表现在它能够提供必要的数据带宽,以支持深度学习和其他AI应用中的数据密集型任务。这种互补性为AI的发展提供了强大的硬件支持。

对于需要HBM颗粒作为显存的客户,选择在SOC内部集成UCIe,搭配ML100的方案并不影响与其他处理器、存储器和加速器芯片的高效协同工作。而且,客户还将享受以下益处:

改善SOC与HBM的紧耦合状态,降低热效应对于HBM颗粒的影响。

减少IP对于SOC的面积占用,16个UCIe IP组合面积小于1个HBM IP面积。

SOC保留UCIe接口,可以采用不同规格的产品灵活配置。

2.5D模块化封装,成本骤降,硅中介层的尺寸不用受限于光罩尺寸。

奎芯科技始终致力于通过创新技术,克服信号完整性、热能和功耗等设计上的挑战。奎芯科技的ML100预计将为AI、大数据分析和高性能计算提供强大的支持,助力各行业的数字化转型与升级。客户可以根据自身需求,灵活选择GDS交付方式,也可以选择购买完整2.5D封装后包含HBM3 颗粒的芯粒产品。展望未来,奎芯科技将持续引领技术革新,积极将创新技术带入市场,为推动科技进步和应用发展贡献力量。

文章来源:奎芯科技