来源:内容由半导体行业观察(ID:icbank)编译自anandtech,谢谢。

回到 2024 年台北国际电脑展,AMD 首席执行官苏姿丰博士在开幕主题演讲中发布了备受期待的 Zen 5 CPU 微架构。AMD 宣布了两个将采用最新 Zen 5 核心的新客户端平台,而不是一个。其中包括 AMD 最新的面向笔记本电脑市场的 AI PC 芯片系列 Ryzen AI 300 系列。相比之下,Ryzen 9000 系列面向使用现有 AM5 平台的台式机市场。 Ryzen AI 300 系列以全新的 Zen 5 CPU 微架构为基础,在图形和 AI 性能方面都有了一些根本性的改进,代号为 Strix Point,将在多个领域实现改进。Ryzen AI 300 系列似乎将在迈向 AI PC 的道路上再添一笔,其移动 SoC 配备了全新的 XDNA 2 NPU,AMD 承诺其性能将达到 50 TOPS。AMD 还用 RDNA 3.5 升级了集成显卡,旨在取代上一代 RDNA 3 移动显卡,从而在游戏中实现比我们之前见过的更好的性能。 在上周 AMD 的技术日上,AMD 披露了有关 Zen 5 的一些技术细节,其中还涵盖了 Ryzen AI 300 和 Ryzen 9000 系列的一些关键元素。从纸面上看,Zen 5 架构与 Zen 4 相比有了很大的进步,关键组件通过比其前代产品更高的每周期指令数推动 Zen 5 向前发展,这是 AMD 从 Zen 到 Zen 2、Zen 3、Zen 4 以及现在的 Zen 5 一直努力做到的事情。 AMD Zen 5 微架构:IPC 比 Zen 4 提高 16% 移动版 AMD Ryzen AI 300 系列和台式机版 Ryzen 9000 系列均采用 AMD 最新的 Zen 5 架构,在性能和效率方面带来诸多改进。其移动产品线中最大的改进或许是集成了 XDNA 2 NPU,旨在利用 Microsoft Copilot+ AI 软件。这些新的移动处理器通过 NPU 可提供高达 50 TOPS 的 AI 性能,使其成为 AMD 移动芯片产品线的重大升级。

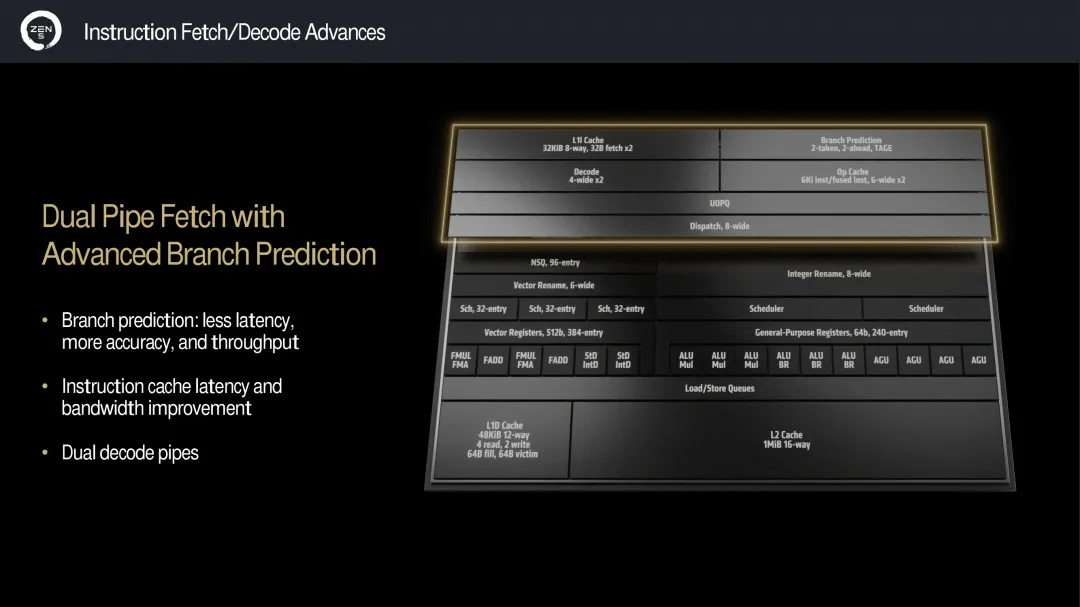

Zen 5 微架构的主要功能包括双管道提取,它与 AMD 所谓的高级分支预测相结合。这旨在减少延迟并提高准确性和吞吐量。增强的指令缓存延迟和带宽优化进一步促进了数据流和数据处理速度,而不会牺牲准确性。

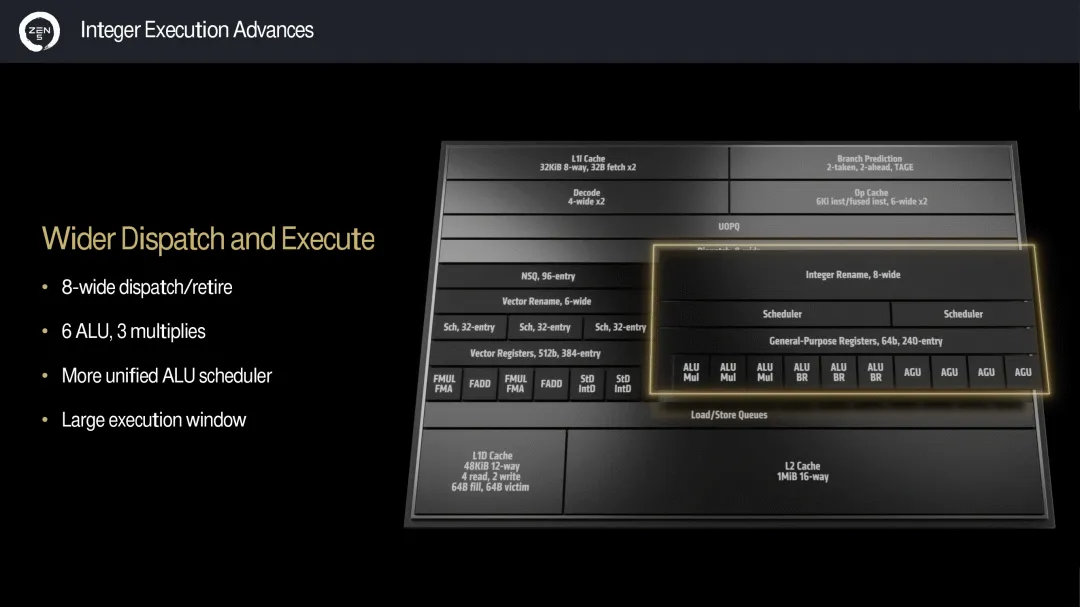

Zen 5 整数执行能力比 Zen 4 有所升级,Zen 5 具有 8 宽调度/退出系统。Zen 5 内部改进的一部分包括六个算术逻辑单元 (ALU) 和三个乘法器,它们通过 ALU 调度程序进行控制,AMD 声称 Zen 5 使用了更大的执行窗口。理论上,这些改进在更复杂的计算工作负载下应该会更好。

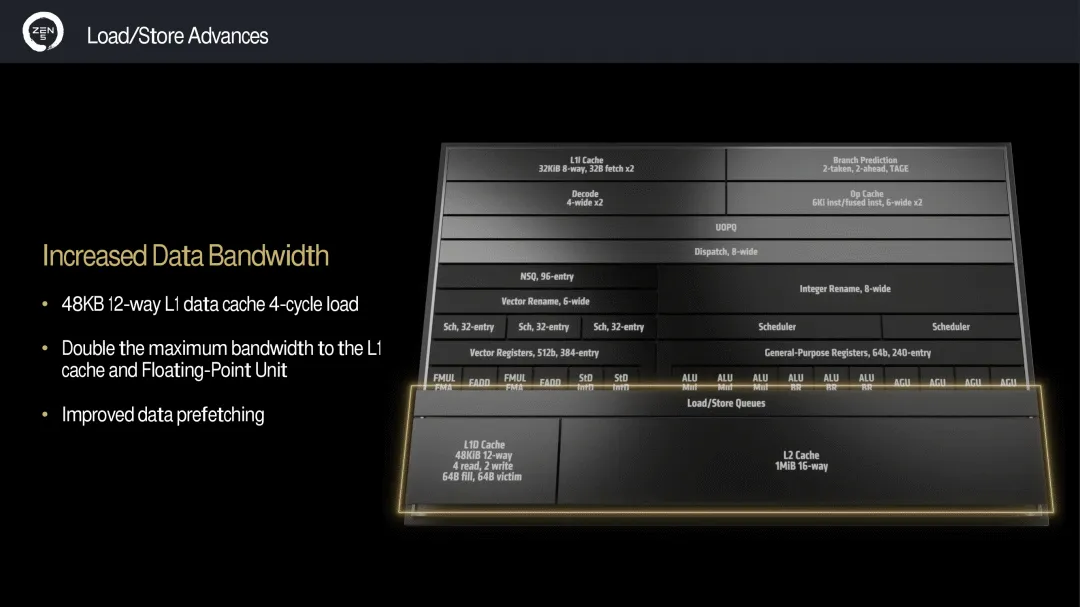

Zen 5 的其他主要增强功能包括比 Zen 4 更高的数据带宽,配备 48 KB 12 路 L1 数据缓存,可满足 4 周期负载。AMD 将 L1 缓存的最大可用带宽增加了一倍,浮点单元也比 Zen 4 增加了一倍。AMD 还声称改进了数据预取器,确保更快、更可靠的数据访问和处理。

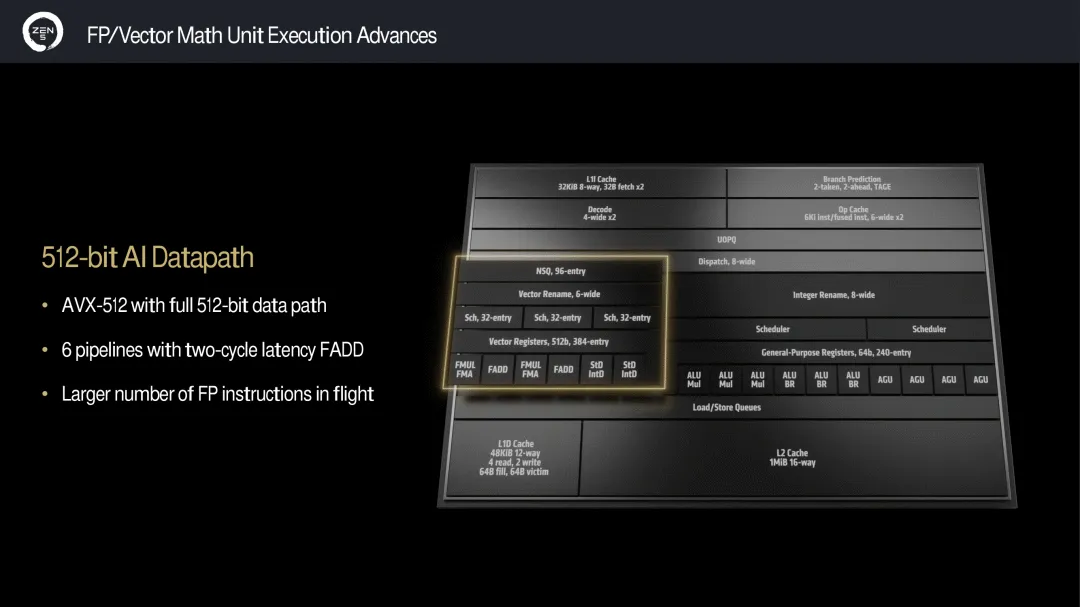

Zen 5 还引入了完整的 512 位 AI 数据路径,它使用具有完整 512 位数据路径的 AVX-512 和具有两周期延迟 FADD 的六个管道。尽管 Zen 4 可以支持 AVX-512 指令,但它使用两个相互协同工作的 256 位数据路径,术语“双泵”是其最广泛使用的术语。Zen 5 现在具有完整的 AVX-512 数据路径,这是一个受欢迎的改进。

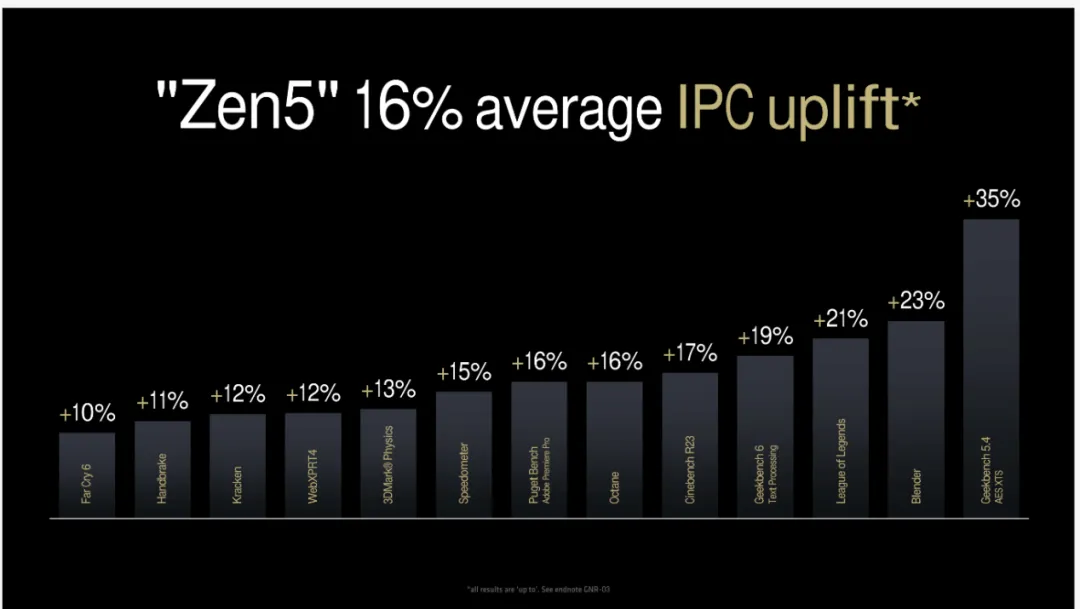

看看 AMD 宣称的 Zen 5 的 IPC 提升,AMD 声称与 Zen 4 相比平均提升了 16%。当然,AMD 提供了内部数据,这些数据显示了各种基准测试的全面改进。其中包括《孤岛惊魂 6》的 10% 提升,《速度计》的 15% 提升,《英雄联盟》的 21% 提升更大。AMD 最大的宣称是 Geekbench 5.4 AES-XTS 的大幅提升了 35%。这是一个令人印象深刻的性能提升,尽管 Geekbench 5 AES XTS 测试使用了 VAES+ 和 AVX10/512,这对于像 Zen 5 一样支持这些指令的处理器来说可能是有利的。

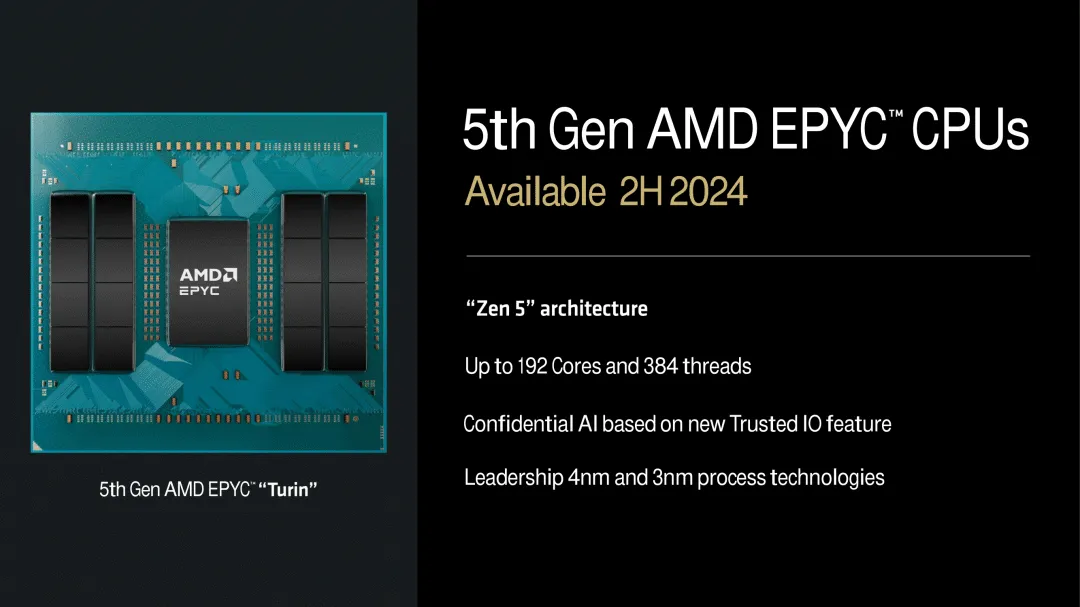

正如我们在 Zen 微架构的先前版本中看到的那样,AMD 正在将 Zen 5 应用于整个产品系列。全功能 Zen 5 内核采用台积电的 4nm制造,而更紧凑、更节能的 Zen 5c 内核则采用台积电的 3nm 工艺技术制造。AMD 即将推出的第五代 EPYC CPU(代号为“Turin”)预计将于 2024 年下半年推出,它将利用多达 192 个 Zen 5 内核。AMD 此前在 2022 年 6 月的财务分析师日上宣布,第五代 EPYC 将于 2024 年推出。

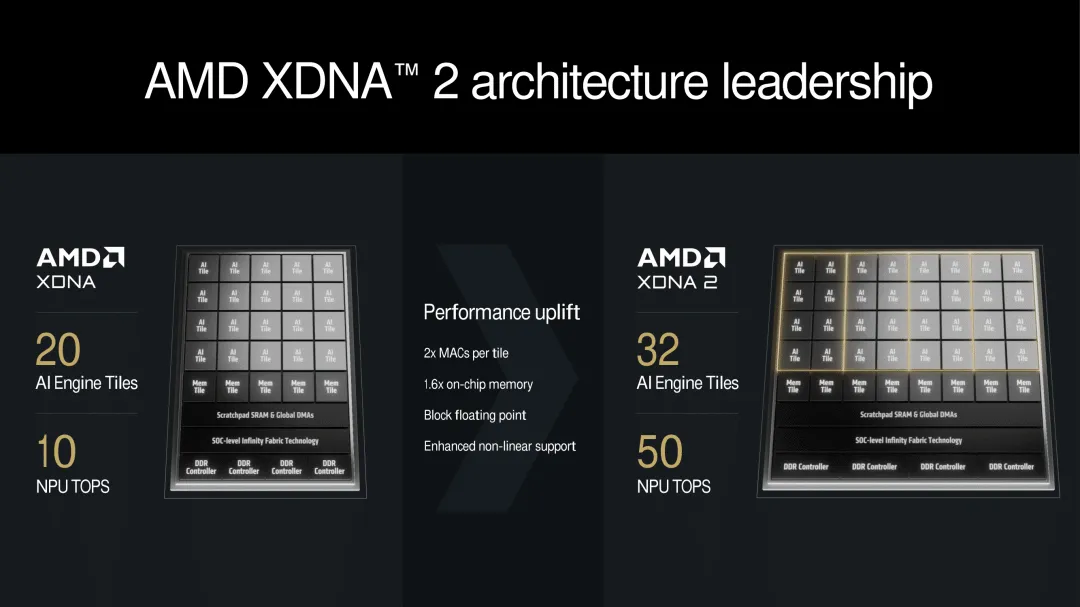

XDNA 2 NPU ,最高可达 50 TOPS 对于用于笔记本电脑的 AMD Ryzen AI 300 系列,与上一代 Ryzen 8040 系列 (Hawk Point) 相比,第二大进步是神经处理单元 (NPU)。AMD于 2020 年收购 Xilinx,通过整合 Xilinx 现有技术启动了 NPU 开发,从而形成了 AMD 最初的 XDNA 架构。凭借其最新版本的架构 XDNA 2,AMD 进一步扩展了其功能和性能。它还引入了对块浮点 16 位算术方法的支持,而不是传统的半精度 (FP16),AMD 声称它结合了 8 位的性能和 16 位的精度。

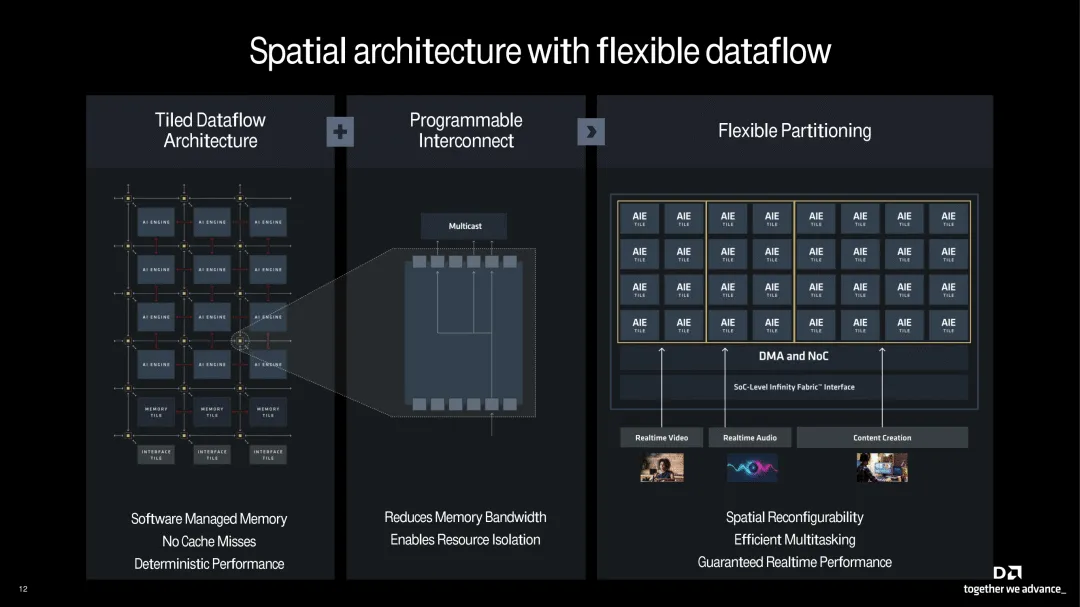

看看 AMD XDNA 架构与多核处理器的典型设计有何不同,XDNA 设计必须将灵活的计算与自适应内存层次结构结合起来。与固定计算模型或基于静态内存层次结构的模型相比,XDNA(Ryzen AI)引擎使用互连的 AI 引擎 (AIE) 网格。每个引擎都经过精心设计,能够动态适应手头的任务,包括计算和内存资源,旨在提高可扩展性和效率。

进一步谈及 AIE 的平铺方法,AMD 称之为空间架构。它设计灵活,同时将平铺数据流结构与可编程互连和灵活分区结合在一起。平铺数据流结构可实现确定性性能,不会出现任何缓存未命中,还可增强内存管理。可编程互连大大降低了对内存带宽的需求,从而使其能够高效地分配资源。所采用的灵活分区设计可实现实时性能,同时能够满足不同的要求,从各种 AI 推理任务(包括实时视频和音频处理)到内容创建工作流程。

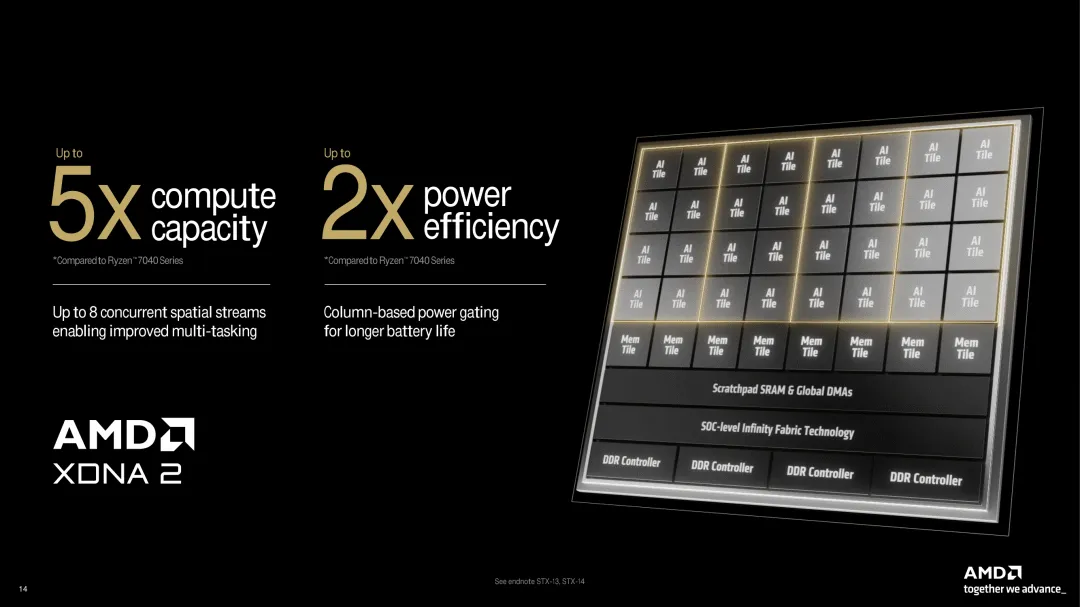

XDNA 2 架构以现有的 XDNA 架构为基础,并添加了更多 AI 引擎以提高吞吐量。Strix Point 中的 AMD XDNA 2 实现有 32 个 AI 引擎块,比上一代多 12 个。XDNA 2 架构不仅提供了更多的 AI 引擎块,而且每个块的 MAC 数量是上一代的两倍,片上内存是上一代的 1.6 倍。

总而言之,AMD 声称其 NPU 性能达到 50 TOPS,这比英特尔和高通目前的产品要高。关于使用 TOPS 来衡量 AI 性能的相关性的争论存在分歧,而微软通过将 Copilot+ 的标准设定为 40 TOPS 而率先提出了这一要求。

XDNA 2 架构不仅试图在 TOPS 上超越竞争对手,而且在设计时还考虑到了能效。AMD 声称,与 Ryzen 7040 系列中使用的 NPU 相比,其 XDNA 2 NPU 的计算能力提高了 5 倍,能效提高了一倍。这是通过各种设计选择实现的,包括基于列的电源门控,AMD 表示它可以显著延长电池寿命,并且在多任务处理时能够同时处理多达八个并发空间流。

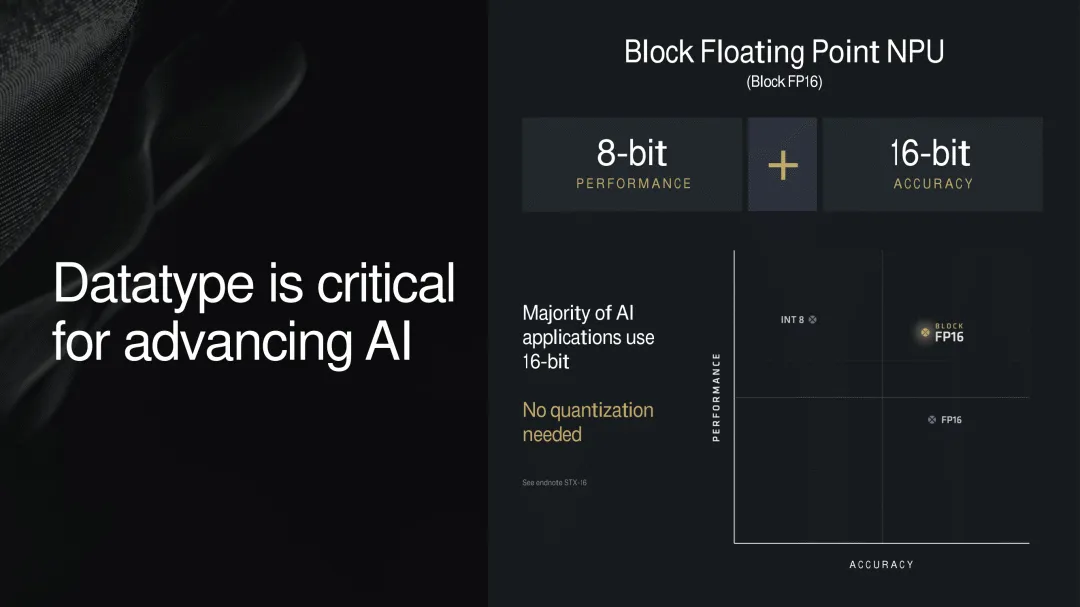

XDNA 2 架构的主要功能之一是支持块浮点 (Block FP16)。简单来说,它提供了 8 位运算的性能和速度,但采用了额外的技巧,试图使精度更接近 16 位运算。值得注意的是,这也是在没有进一步量化或减少正在处理的数据大小的情况下实现的。

与其他神经网络精度优化一样,Block FP16 的目的是减少所需的计算工作量;在这种情况下,使用 8 位数学,而不会产生从 16 位数学降级的全部缺点——即降低精度导致结果较差。当前一代 NPU 已经可以进行原生 8 位处理(以及 16 位处理),但这要求开发人员要么优化(和量化)他们的软件以进行 8 位处理,要么承受停留在 16 位的速度损失。人工智能仍然是一个相对年轻的领域,因此软件开发人员仍在努力弄清楚多少精度才足够(这条线似乎像边缘栏一样不断下降),但基本思想是,这试图让软件开发人员鱼与熊掌兼得。

尽管如此,从技术角度来看,Block FP16(又名Microscaling)本身并不是一项新技术。但 AMD 将成为第一家支持该技术的 PC NPU 供应商,英特尔即将推出的 Lunar Lake 也将加入他们的行列。因此,虽然这是 AMD 的一项新功能,但它不会是一项独特的功能。

至于 Block FP16 的工作原理,AMD 自己关于该主题的材料相对较高,但我们从其他来源得知,它本质上是一种带有附加指数的定点 8 位计算形式。具体来说,Block FP16 对所有值使用共享指数,而不是每个浮点值都有自己的指数。例如,FP16 数字不是具有符号位、5 位指数和 10 位有效位,而是具有与所有数字共享的 8 位指数,然后是 8 位有效位。

这实际上允许处理器通过将唯一有效数字处理为 INT8(或定点 8 位)数字来作弊,同时跳过共享指数的所有工作。这就是为什么 Block FP16 性能与 INT8 性能大致相同:它基本上是 8 位数学。但是通过共享指数,软件作者可以将计算的整个数字范围窗口移动到特定范围,该范围通常超出了真正的 FP8 数字的微不足道的指数所提供的范围。

大多数 AI 应用都需要 16 位精度,而 Block FP16 满足了这一要求,至少从 AI 的角度来看,它同时为移动市场带来了高性能和高精度。这使得 Block FP16 成为推动 AI 技术发展的重要组件,而这也是 AMD 正在努力推进的事情。

归根结底,Ryzen AI 300 系列移动芯片中基于 XDNA 2 的 NPU 实际上是用来处理 AI 工作负载并以比使用图形更节能的方式运行 Microsoft Copilot+ 等功能。并且,通过能够提供 8 位性能和 16 位精度,这为开发人员提供了另一个杠杆,以充分利用硬件。

AMD XDNA 2 架构将与 Ryzen AI 300 系列一起首次亮相,它将提供解锁 AI PC 的关键,或者至少是微软对 Copilot+ 的 40 TOPS 要求所定义的。通过将 Block FP16 引入方程式,AMD 以 8 位速度实现了(接近)16 位精度,使其在某些 AI 应用程序上具有更高的性能。总而言之,集成的 NPU 预计将提供高达 50 TOPS 的计算性能。

AMD 是第一家在芯片中集成 NPU 的 x86 SoC 供应商,随着对片上 AI 解决方案的需求不断增长以解锁许多软件功能,他们希望硬件(及其代表的芯片空间)能够得到充分利用。XDNA 2 架构确保 AMD 保持领先地位,为移动市场提供稳定的性能和综合的多功能性。

RDNA 3.5 显卡带来视觉效果 为 Ryzen AI 300 移动系列芯片带来的另一项新技术是升级的集成显卡。AMD 的 RDNA 3.5 图形架构代表着下一代 AMD 图形架构的垫脚石(没有 .5)。最新版本的设计旨在提高性能和效率,重点是优化每瓦性能的每一滴。值得注意的是,AMD 尚未提供有关 RDNA 3.5 的太多细节,因此我们将深入研究其主要功能和进步。

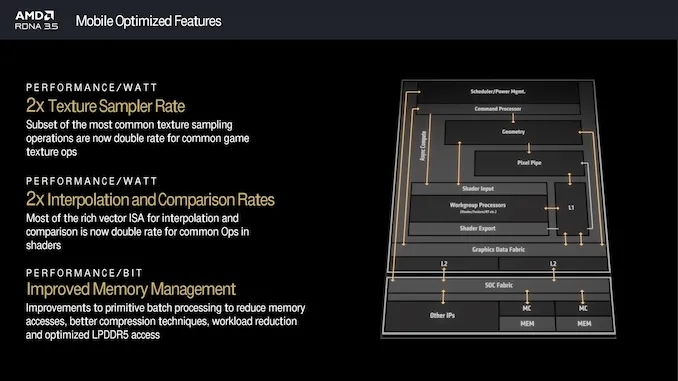

AMD RDNA 3.5 图形架构代表了其 Ryzen AI 300 移动 SoC 集成显卡的下一步,与 RDNA 3 相比有一些显著的升级。AMD 一直与 ISV 和开发商密切合作,以确保 RDNA 3.5 提供 AMD 表示将与移动合作伙伴携手合作以提高游戏每瓦性能的所有内容。一些改进包括常规图形着色器操作,这些操作经过优化以确保一切正常运行。AMD 非常注重每位性能,这不仅减少了内存访问时间,还使操作更流畅。改进的总体重点是功率与性能,AMD 的目标是中间地带以确保更长的电池寿命,这对于移动和便携式设备至关重要。

与 RDNA 3 相比,许多改进都来自针对移动平台特别优化的多项功能。这确保了 Radeon 890M(Ryzen AI 300 系列的型号)在效率和视觉性能方面兼具两者的优势。纹理采样率翻倍,确保 GPU 具有双倍速率性能。从表面上看,这意味着在游戏过程中纹理和图形的细节和清晰度得到增强。从理论上讲,这应该有助于改善细节纹理,使其在玩高分辨率游戏时看起来很棒。此外,RDNA 3.5 的插值和比较率是 2 倍,因为矢量 ISA 操作可以更好地呈现高质量图形的细节。

另一个关键改进是更好的内存管理技术。这些技术降低了内存访问频率,这意味着数据处理在理论上应该更快,总体上更节能。优化的 LPDDR5 访问还应保证快速高效的内存使用,从而有助于延长电池寿命。

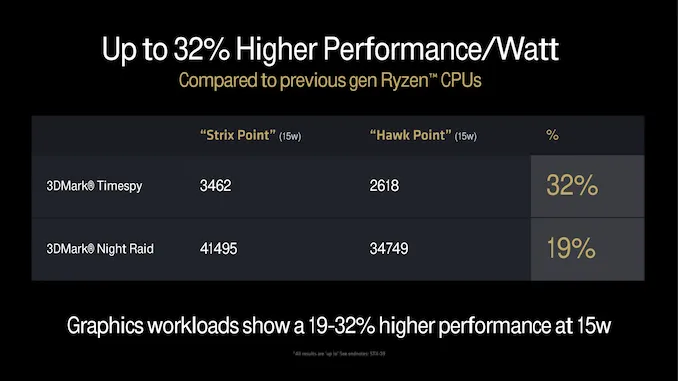

AMD 提供了一些 RDNA 3.5 与 RDNA 3 的性能数据,如果将其转化为实际性能,这些数据将非常令人印象深刻。从纸面上看,RDNA 3.5 架构与上一代 Ryzen 8040 系列相比,性能显著提升,每瓦性能提升高达 32%。在 3DMark Timespy 和 3DMark Night Raid 等图形工作负载中,AMD 声称 RDNA 3.5 在 15 W 下的性能提升了 19% 至 32%。

由于这些改进,RDNA 3.5 与其前身 RDNA 3 相比在各个方面都有所改进。例如,RDNA 3.5 通过优化纹理采样和插值等关键内容,大大提高了 GPU 更有效地执行复杂图形操作的能力。改进 RDNA 3.5 中的内存管理还可以实现更好的功率优化和数据处理,以解决主要的 GPU 性能问题。所有这些都应该带来实际的性能优势。然而,与任何移动 SoC 一样,这些仍然没有达到独立显卡的水平,独立显卡通常具有更大的芯片面积、更高的制造级晶体管预算,当然还有更高的功率。

原文链接