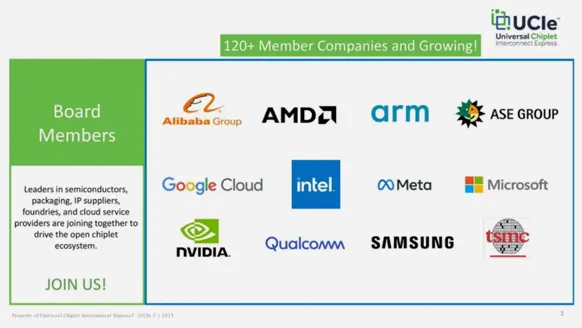

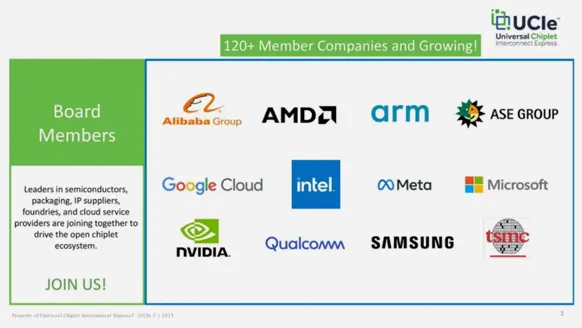

8月6日,通用芯粒互联产业联盟(UCIe Consortium)宣布发布UCIe 2.0规范,这是对芯片互连技术的重要更新。因为摩尔定律的失效,半导体行业过去多年正在寻找提升芯片性能的方法,而芯粒(Chiplet)正在成为几乎所有巨头的共同目标。然而,因为Chiplet的理念是将芯片的不同功能模块变成一个die,如何保证这些die能够更通用地连接到一起就成为了行业的头等大事。于是,UCIe( Universal Chiplet Interconnect Express )便顺势成立。据介绍,UCIe是一种开放的行业架构标准,可在不同芯粒之间提供die-to-die之间的接口,解决物理芯片间 I/O 层、芯片间协议和软件堆栈问题。自2022年3月成立以来,UCIe联盟得到了业界的广泛支持,包括AMD、Arm、Google Cloud、英特尔、Meta、微软、高通、三星、台积电等领先企业。这些公司的参与不仅确保了UCIe规范的技术先进性,也促进了行业内的协作和标准化。8月6日,通用芯粒互联产业联盟(UCIe Consortium)宣布发布UCIe 2.0规范,这是对芯片互连技术的重要更新。UCIe 2.0规范引入了对可管理性标准化系统架构的支持,并全面解决了系统级封装(SiP)生命周期中跨多个芯粒的可测试性、可管理性和调试(DFx)的设计难题。

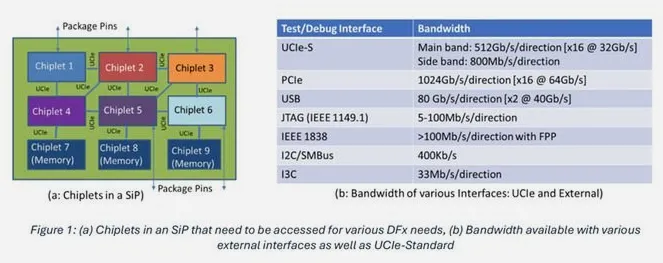

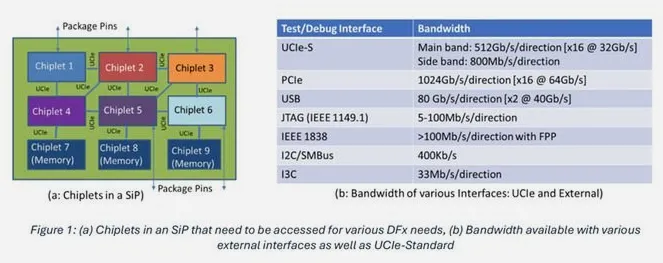

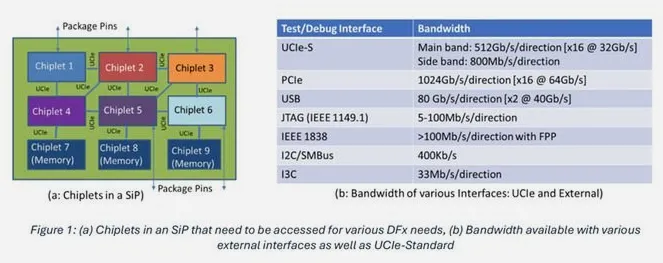

全面的可管理性支持:UCIe 2.0规范为任何具有多个芯粒的系统级封装(SiP)结构提供了可管理性、调试和测试的全面支持,这是通过引入可选的可管理性功能和UCIe DFx架构(UDA)实现的。其中包括在每个芯粒内部构建的管理结构,用于测试、遥测和调试功能,从而简化了不同供应商芯粒的互操作性,为SiP管理和DFx操作提供了统一的方法。

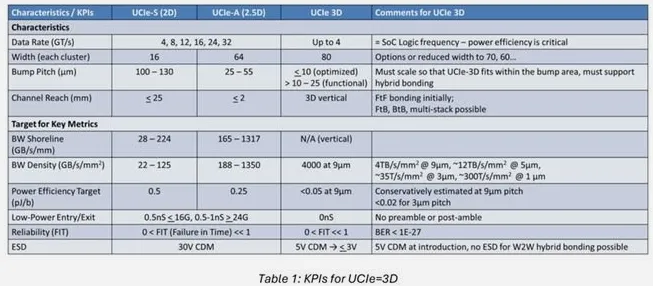

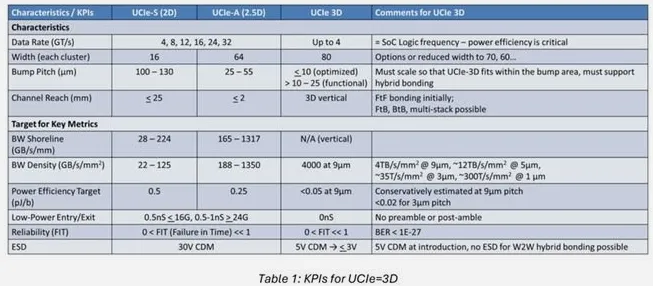

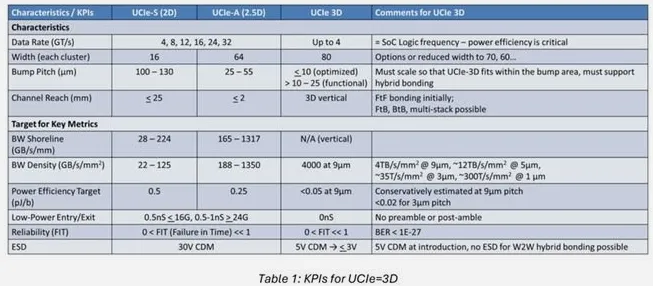

3D封装技术:与2D和2.5D架构相比,UCIe 2.0规范支持的3D封装技术提供了更高的带宽密度和改进的能效。UCIe-3D优化了混合键合技术(hybrid bonding),允许凸点间距从大至10-25微米到小至1微米或更小,以提供灵活性和可扩展性。

互操作性和合规性测试:UCIe 2.0规范优化了封装设计,以确保不同芯粒间的互操作性和有效的合规性测试。符合性测试的目标是验证被测设备(Device Under Test,DUT)相对于已知良好参考实施的主要频段支持特性,规范确立了物理、适配器和协议的初步测试框架。向后兼容性:新规范完全向后兼容UCIe 1.1和UCIe 1.0,确保了与旧版本的兼容性。同时,通过一系列的优化,使规范更加适用于包含多个芯粒的SiP结构,为行业的长期发展提供了更大的可能性。UCIe 2.0规范的发布,标志着芯片互连技术向更高密度、更高能效和更易于管理的方向发展。这一规范的实施将简化来自不同供应商的芯粒在SiP中的集成,推动开放的芯片生态系统的发展。UCIe联盟希望可以建立一个芯片到芯片的互联标准,并培育一个开放的芯粒生态系统,以满足客户对可定制的封装级整合的需求,连接来自多个供应商的芯片。

在最早的 UCIe 1.0里,涵盖了芯片到芯片之间的 I/O 物理层、协议和软件堆叠等,并利用了 PCI Express(PCIe) 和 Compute Express Link(CXL) 两种高速互连标准。而2023年发布的UCIe 1.1规范里,进一步纳进了针对汽车应用的增强功能。UCIe 联盟总裁兼三星电子公司副总裁 Cheolmin Park 表示:“UCIe 联盟支持多种芯片,以满足快速变化的半导体行业的需求。UCIe 2.0 规范在之前的版本基础上开发了全面的解决方案堆栈,并鼓励芯片解决方案之间的互操作性。这又是联盟致力于蓬勃发展的开放芯片生态系统的又一例证。”