文章来源:明德扬FPGA科教

一、摘要

明德扬(MDY)在某个XILINX项目中,偶然性出现开机后通信出错的情形,具体表现为反复开机测试400次后,约有1~2次通信异常,数据发不出去。经过定位,是某个FIFO出现异常,时钟正常、复位无效、写使能有效的情况,空信号empty一直为1,即一直保持为空的问题。

二、项目背景

FIFO是FPGA项目中使用最多的IP核,一个项目使用几个,甚至是几十个FIFO都是很正常的。通常情况下,每个FIFO的参数,特别是位宽和深度,是不同的。如果按照通常做法,每种位宽和参数,都要打开FIFO IP核界面、命名(命名不好不好分辨需要的FIFO)、设置参数、生成并编译IP核,工作量可以想象出来是非常多的。

明德扬(MDY)承接过多个基于XILINX芯片的研发项目,包括VPX网络透明传输项目(芯片为XC7K325T-2FBG900)、某高端测试仪项目(芯片为XCKU060-FFVA1156)、某网闸设备项目(芯片为XC7Z030-FBG676)等,另外,明德扬自研了基于XC7K325T-2FBG900和基于XC7K410T-2FBG900芯片的核心板,在XILINX研发领域拥有丰富的经验。

对于我们专门承接项目的团队,绝不可忍受如此重复、枯燥、容易出错的工作。经过精心研究,终于发现XILINX的原语:xpm_fifo_async,是可以可参数化FIFO的位宽和深度的。即在设计时,不用生成FIFO IP,直接例xpm_fifo_async,例化时定义好位宽和深度,就可以使用了。关于具体的使用方法,可以留意我们新出的文章教程。

本问题的出现,就是在使用这个xpm_fifo_async时出现的。

三、问题现象

FPGA问题都不好定位,特别是偶然性出错的问题,即使复现问题都要花大量精力。本问题出现的概率小于1%,即使概率如此之低,也是不得不去定位去做的工作。

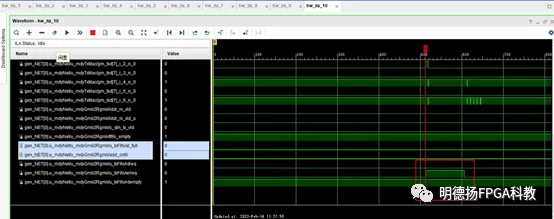

在花费了一个月的时间,才定位到某个FIFO出现异常。为更加细致地确认是FIFO哪里出错,使用ILA抓取FIFO的信号,包括写使能、复位、空指示信号等。

如上图所示,在FIFO写使能有效时,empty信号仍然保持为空状态,导致数据无法传输。更奇怪的是,即使复位了这个FIFO,仍然是同样现象。

四、问题分析

该问题非常之奇怪,从逻辑角度讲,时序是正确的,那么IP核就应该正确,是不应该出现此问题的。

怀疑是FIFO使用不正确,如FIFO满后还在写,或者FIFO空后仍在读。特意在ILA触发写使能、写满信号同时为1,看两者是否有同时有效,没有触发到,说明没有问题。

怀疑是写时序不正确:为此,我们还反反复复地观测写时序,捕捉开机后的第一个写时序,也是没问题的。

怀疑处于复位状态:为此观测复位信号,发现没有处于复位状态,没有问题。

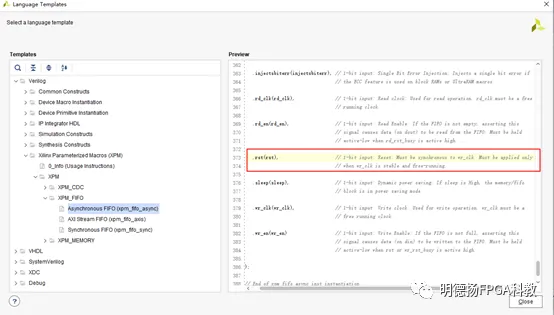

在思考了多种办法后,问题没有解决。为此,不得不认真查阅xpm_fifo_async的官方资料,查看步骤:

vivodo-PROJECT MANAGER-Language Templates-Verilog-Xilinx Parameterized Macros(XPM)-XPM-XPM_FIFO-Asynchronous FIFO (xpm_ fifo async)。

通过调阅vivado中有关FIFO的说明,终于发现了问题。

如上图所示,复位信号rst要求同步于WR_CLK时钟。而我们的复位信号是异步信号,不满足要求。

五、解决方法

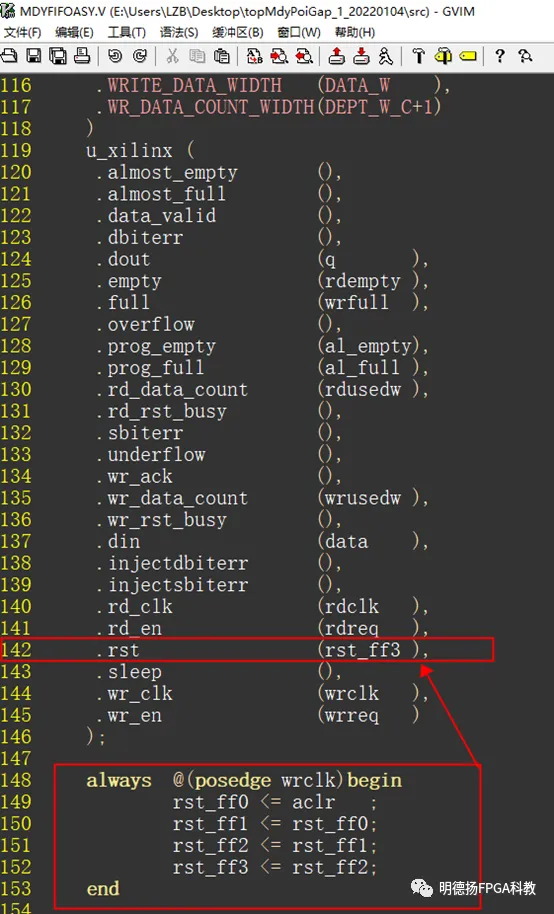

对 FIFO中的复位信号进行异步信号同步化处理,即对复位信号进行延迟两拍处理,如下图所示:

上图中,aclr是异步复位信号,经过上图中的148~153行的代码,将该信号同步化,同步化后的rst_ff3可以认为同步于写时钟。将该信号连接到rst中,如图中的第142行。

每3分钟重启一次,经过三天的严苛测试,再没有出现通信异常问题,问题得到解决!!!