摘要

本文介绍了许多通信系统中的关键技术,包括一种在FPGA上实现正交频分复用(OFDM)和单频信号的技术。该设计是通过集成HDL Coder™生成的RTL和手动编码的RTL开发,可以在OFDM和单频模式之间切换。这对于无线链路测试特别有用。

本文解决了在FPGA上初始调试无线链路时遇到的一个常见问题——缺少能将OFDM信号馈送到FPGA的主机。OFDM和单频调制器允许在不依赖主机的情况下测试JESD204到射频前端的链路,从而显著提高测试过程的效率。

该设计可以直接在莱迪思FPGA中实现,从而节省成本并缩短开发周期。此外,该设计还通过ModelSim中的RTL和门级仿真验证以及莱迪思CertusPro-NX™(CPNX)FPGA开发套件上的硬件测试。

总之,本文提出了一种基于莱迪思FPGA器件的新型OFDM和单频信号的设计,简化了无线链路验证过程并降低了所需的成本和时间。

引言

正交频分复用(OFDM)和单频调制是许多通信系统(尤其是5G和Wi-Fi 4/5/6/7标准)中使用的关键技术。OFDM以其频谱效率高、抗信道衰落性能强和灵活性而著称。另一方面,单频信号是一种更简单的信号生成形式,通常用于基本的系统验证和故障排除。

本文介绍了一种全新的方案来解决这些系统中遇到的一个常见问题,即如果没有主机控制器,就很难生成所需的复杂测试模式。本文介绍了OFDM和单频调制器(可在OFDM和单频之间切换)的设计和实现。该设计的开发是基于HDL Coder生成的RTL和手动RTL编码。

由于OFDM模式依赖主机,必须在FPGA和主机之间建立匹配的接口(如PCIe)以及在开始无线链路测试之前,需要执行测试所需的主机软件。这一过程不仅耗时、效率低,而且在出现问题时调试难度大。

OFDM和单频调制器可与FPGA中的JESD204B IP直接连接,发送OFDM和单频信号以验证JESD204B链路。引入OFDM和单频调制器后,我们可以在不依赖主机的情况下验证无线链路,大大提高了测试过程的效率。

OFDM和单频调制器设计

设计细节

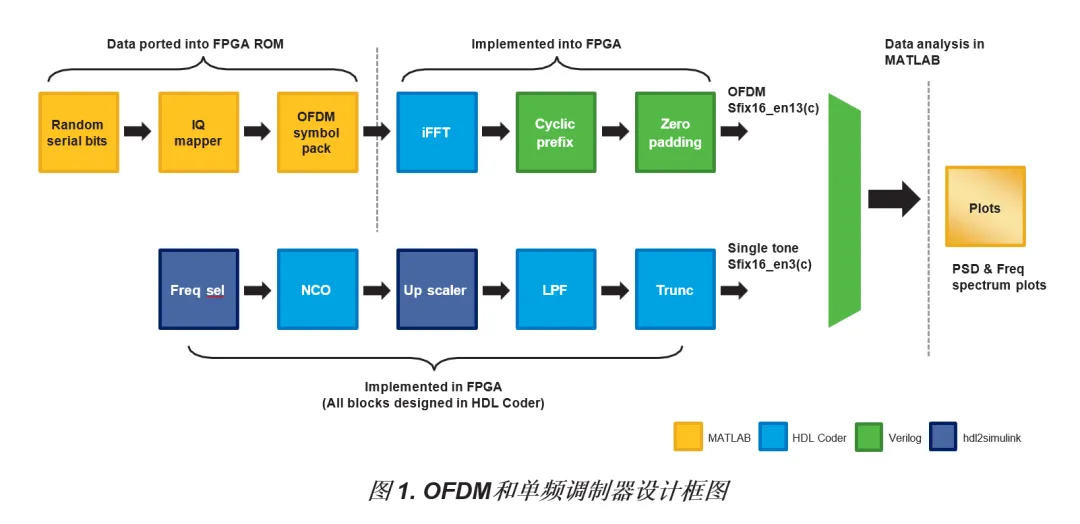

顾名思义,这种设计支持两种模式生成:OFDM模式和单频模式。用户只需使用一个控制信号,就能在这两种模式之间进行实时切换。该设计的上层框图显示了两条数据路径:上层路径用于生成OFDM模式,下层路径用于生成单频模式。

该设计利用了各种设计技术和工具,包括MATLAB®、Simulink®、HDL Coder和手动编码的RTL。图1中的颜色编码区分了实现方法:

. 黄色:使用MATLAB实现的模块

. 蓝色:使用HDL Coder实现的模块

. 绿色:用手动Verilog编码实现的模块

. 紫色:从手动Verilog编码导入Simulink的模块

OFDM模式生成

OFDM模式发生器不断重复并输出相同的OFDM符号及其循环前缀。在OFDM数据路径中,随机调制符号在MATLAB中预先生成并存储在FPGA ROM中。然后,这些符号经过IFFT、循环前缀和零填充块,形成OFDM模式,并生成IQ数据输入到射频前端。

下表列出了设计中使用的OFDM模式系统参数。

表 1. OFDM模式系统参数

单频模式生成

单频模式发生器由一个实时配置频率为1 MHz、2 MHz、3 MHz、4 MHz和5 MHz的NCO组成。在单频数据路径中,多频NCO可产生不同频率的正弦信号。频率选择器模块允许用户通过3位输入信号在这些支持的频率之间切换。NCO的输出经过放大器来提升幅度。低通滤波器可平滑信号并去除噪声。最后,FIR输出被截取为16位复合信号,形成单频测试模式。

特有的特性和优势

. 实时切换:该设计允许使用单个控制信号在OFDM和单频模式之间进行实时切换。

. 集成设计:用户可直接在FPGA中实现该设计,无需其他外部设备。

. 成本和时间效率高:这种设计减少了购买或借用外部设备以及建立复杂系统所需的成本和时间。

. 全面验证: 用户可以连接FPGA中的JESD204B IP或类似接口,并在开发套件上执行从功能仿真到硬件验证等一系列操作。

设计流程

本节讨论OFDM和单频调制器的设计过程,从MATLAB模型的实现到莱迪思FPGA的实现。

开发流程

莱迪思FPGA上的OFDM和单频调制器设计的开发流程始于在MATLAB中的模型实现。然后使用HDL Coder和DSP HDL Toolbox™库将模型转换为Simulink模型。Simulink的仿真结果与最初的MATLAB模型进行验证。接下来是HDL代码生成,通过HDL Coder生成RTL文件。然后将这些RTL文件与手动编码的RTL整合,形成完整的设计。然后在Modelsim中进行RTL和门级仿真以验证功能,并将结果与Simulink仿真进行比较。最后,在莱迪思FPGA开发套件上实现设计,并根据RTL和门级仿真检查硬件输出结果。在验证过程中发现的任何差异都会提示进行调试,并重新检查之前的阶段进行更新。

图 2. OFDM和单频调制器设计的开发流程

使用HDL Coder生成HDL

下面以单频模式发生器为例,介绍HDL Coder生成HDL文件的典型步骤。

. 从Simulink中的HDL Coder和DSP HDL工具箱库中实例化所需的模块

. 根据目标要求配置模块参数

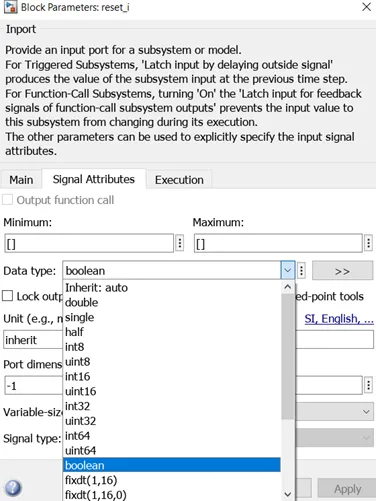

. 配置输入和输出端口的数据类型

. 连接模块和端口创建子系统

. 添加测试台,便于在Simulink中验证子系统

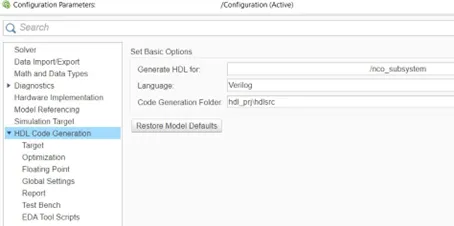

. 在Settings -> HDL Code Generation Settings菜单中配置HDL生成设置

. 指定所需参数,如语言(VHDL/Verilog/SystemVerilog)

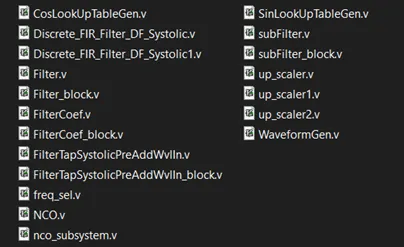

. 使用Generate HDL Code图标生成HDL文件

图 3. Simulink中的单频模式发生器设计框图

图 4. NCO模块参数配置示例

图 5. 输入和输出端口数据类型示例

图 6. HDL代码生成设置示例

图 7. 生成的Verilog HDL文件示例

实现

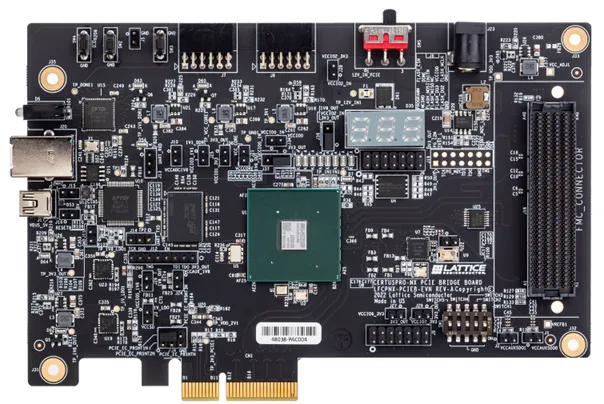

该设计使用了CertusPro-NX PCIe桥接板,在CertusPro-NX(CPNX)器件上实现。该设计的时钟频率为122.88 MHz,该时钟是通过PLL产生的,板上已有的125 MHz时钟作为PLL的单端参考时钟。

使用的软件和硬件

本设计所使用的软件和硬件如下:

软件

. MATLAB R2023b

. Simulink HDL Coder

. DSP HDL Toolbox Communication Toolbox™

. 莱迪思Radiant™软件2023.2.0.38.1版本

. ModelSim莱迪思FPGA版本(2023.3)

. Fixed-Point Designer™

硬件

. 莱迪思CertusPro-NX FPGA(封装LFCPNX-100-9LFG672I)

. CertusPro-NX PCIe桥接板

图 8. CertusPro-NX PCIe桥接板正面图

引脚分配

表 2. CertusPro-NX PCIe桥接板设计的引脚分配

设计验证

该设计通过Modelsim中的RTL和门级仿真以及CertusPro-NX开发套件上的硬件测试进行了验证。这一全面的验证过程确保了设计实现的稳健性和可靠性。以下章节介绍了使用的测试方法。

Modelsim仿真

. 观测仿真信号波形

. Test Bench打印OFDM和单频输出数据,与Simulink的参考数据进行比较

. 同样的输出数据还用于在MATLAB中绘制功率谱密度(PSD)和频谱,以便进一步分析

. 门级仿真数据重复上述步骤

CertusPro-NX PCIe桥接板硬件测试

. 使用Reveal Analyzer采集OFDM和单频输出数据

. 采集到的数据输入到Modelsim中进行观测检查

. 还将数据输入到MATLAB中,用于绘制PSD和频谱图

结果和讨论

RTL仿真结果

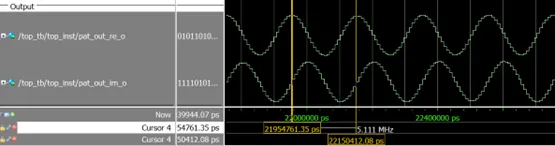

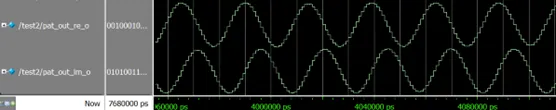

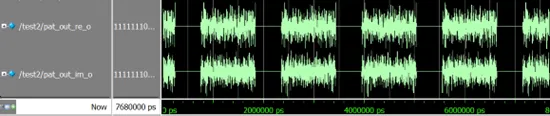

采集了5 MHz单频信号和OFDM信号的RTL和门级仿真波形。

图 9. RTL仿真中的5 MHz单频复信号正弦输出

图 10. RTL仿真中的时域OFDM复信号输出

图 12. 门级仿真中的时域OFDM复信号输出

从仿真结果得出的主要结论是:

. 根据Modelsim测量结果,单频信号具有预期的正弦波形和正确的频率

. OFDM信号符合预期的突发模式(burst pattern)

. 根据Test Bench打印的单频和OFDM信号仿真输出数据与RTL仿真和门级仿真相匹配

. 经过验证,打印数据也与Simulink仿真的参考值相匹配

CertusPro-NX PCIe桥接板硬件测试

Reveal Analyzer的输出数据传输到Modelsim中,用于5 MHz的单频信号和OFDM信号。

频图 13. Reveal Analyzer采集的复单频5 MHz信号的正弦输出

图 14. Reveal Analyzer采集的复时域OFDM输出

硬件测试结果中得出的主要结论是:

. 单频信号是预期的正弦波形

. OFDM信号符合预期的突发模式(burst pattern)

. 注意在Modelsim中,每个采样被转换为1ns步长。

结果分析和解读

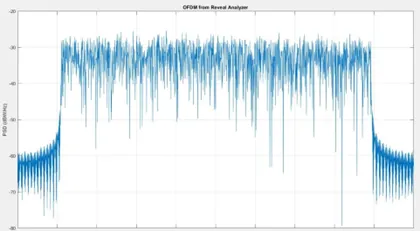

在MATLAB中绘制了门级仿真和硬件测试结果的频谱和PSD,以便进一步分析。

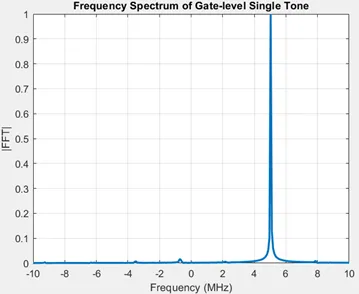

图 15. 门级仿真的5 MHz复单频正弦输出的频谱图

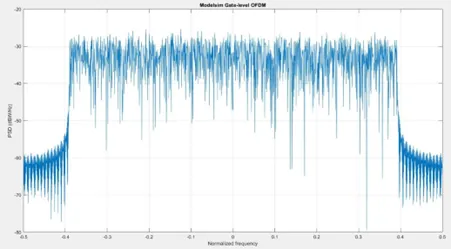

图 16. 门级仿真的OFDM输出PSD图

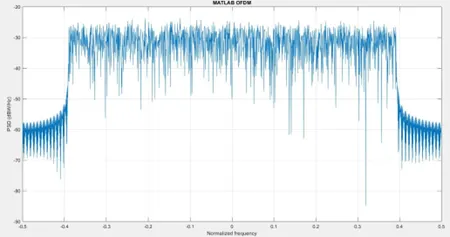

图 17. MATLAB模型的OFDM输出PSD图

门级仿真图的主要结论是:

. 单频仿真值的频谱图显示了5 MHz处的预期频率峰值

. MATLAB模型和门级仿真的OFDM输出PSD图相似

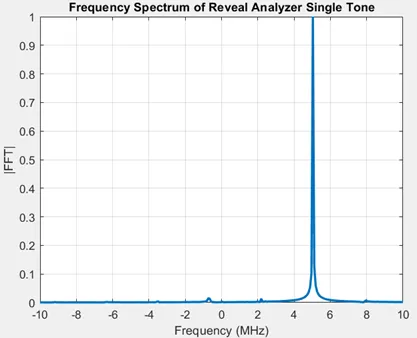

图 18. Reveal Analyzer的5 MHz复单频正弦输出频谱图

图 19. Reveal Analyzer的OFDM输出PSD图

从Reveal Analyzer的图中可以观察到以下关键信息:

. Reveal Analyzer的单频频谱图显示了5MHz处的预期频率峰值

. MATLAB模型、门级仿真和Reveal Analyzer的OFDM输出PSD图相似

结论

评估和结论总结

本文介绍了通过整合HDL Coder生成的RTL和手动编码RTL,设计和实现OFDM和单频调制器的过程。RTL和门级仿真结果以及CertusPro-NX开发套件上的硬件测试结果表明了设计的稳健性和可靠性。此外,RTL仿真和门级仿真之间的匹配结果以及硬件测试结果也验证了设计的功能性。

未来的研究建议

今后的研究可侧重于以下领域:

a. 与JESD204B IP集成:调制器可与JESD204B IP集成以启动链路。这样可以对设计进行更全面的测试和验证。

b. 移植到Lattice Avant™器件并添加sinc滤波器:可将调制器移植到Lattice Avant器件并添加sinc 滤波器,提高OFDM信号的频谱效率,有助于提高设计的性能。

c. 利用外部模拟芯片组和JESD204集成进行进一步验证和BER测量。

技术支持与协助

您可以通过下列网址提交技术支持案例:www.latticesemi.com/techsupport。

有关常见问题,请参阅莱迪思答案数据库:www.latticesemi.com/ Support/AnswerDatabase。