作者:Grace Sun,AMD工程师;来源:AMD开发者社区

IDR的全称是Intelligent Design Runs,在阐述what和how之前,我们先来了解一下why,即在Vivado工具中引入这个流程的背景和目的。

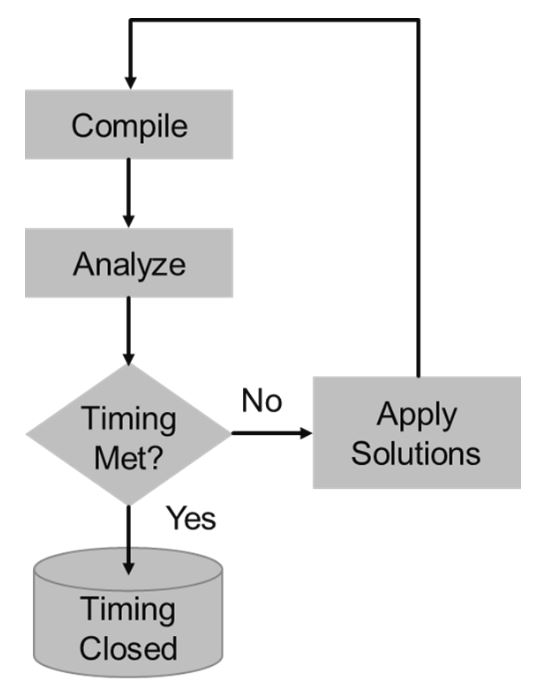

高速设计的时序收敛一直是硬件设计中最具挑战性的阶段之一。时序收敛是一个费时费力的过程,需要审查设计工具报告、查找时序故障、评估每个违规的可能根本原因,然后制定解决方案以潜在地修复时序故障。 而这些不同的解决方案需要进行组合和取舍应用到设计中,重新运行设计实现再次评估时序结果,过程简化如下图所示:

典型的解决方案包括但不限于:

• 优化HDL 源代码以减少逻辑深度和逻辑利用率

•插入流水线级以提高时钟速度

• 探索和遍历工具选项和编译策略,以使用不同的综合、布局布线算法

• 对时序关键逻辑做物理约束和布局规划,指导工具的设计实现

不难想象,对于具有挑战性的复杂设计来说,时序收敛并不是一个一蹴而就的过程,通常伴随着迂回反复和不确定性。你需要首先从设计瓶颈和关键路径修复入手,选择可能产生最大积极影响的解决方案,在随后的迭代中,再做微调进行改善。在众多的方案中,如何以最快的路径最少的迭代完成收敛闭环,很大程度上依赖于设计者的专业知识以及经验,包括详细了解目标FPGA/ACAP架构以及Vivado工具链的知识。另一方面,多个解决方案往往并行运行,因为单个迭代往往需要几个小时,这对计算能力和资源会造成不小的压力。

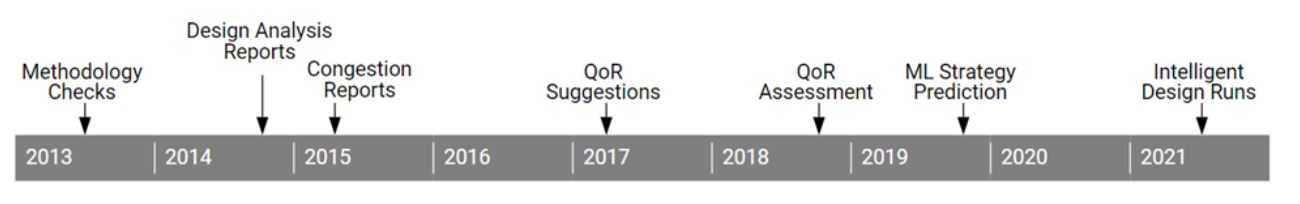

为了确定如何最好地提高时序收敛的效率,基于多年来支持客户积累的经验,研发团队对时序收敛专业技术进行了详细研究,逐步在Vivado 工具中引入了许多基于规则和机器学习模型构建的时序收敛辅助功能,旨在为时序收敛过程注入更多智能,每项新加的功能都以现有构建模块为基础,组合发挥更强大的作用,从而实现更快、更有效的时序收敛。时间线演变如下图所示:

2013年: Vivado 工具中首先实现了方法论检查的自动化。UltraFast 设计方法论用户指南中的常见最佳实践被转化为适合 Vivado 工具设计规则检查(DRC)的规则。设计方法论的合规性内置到工具中,可向用户指出通常导致时序问题的方法论违规。

2014年: 设计分析和拥塞报告提供了对时序失败原因的更深入洞察。这些报告超越了基本的时序报告,考虑了逻辑结构、物理实现和设计复杂性对关键路径的影响。引入了像Rent Exponent这样的指标,以识别最有可能产生布线拥塞的逻辑单元。

2017年: 开发了一个复杂的基于规则的引擎,提供一键解决方案,自动化为工具建议。建议以新对象形式存在,代表设计约束或Tcl命令,用于解决分析中发现的特定问题。RQS成为基于规则的时序闭环的一项重大进步。

2018年:利用在综合和实现过程中收集的设计指标,开发了一种基于规则的引擎,称为报告质量评估(RQA),用于评估和预测成功时序闭环的可能性,以逐渐增加的1到5的数字分数来发出评估。报告包括推动分数的问题的细节,RQS成为改进评估的补充工具。

2019年:Vivado工具中的机器学习模型从研究跃升至实践,预测数十种可能性中最有可能找到最佳设计性能的编译策略。通过限制尝试的编译策略数量,减少了时序闭环迭代所需的并行处理量。这些预测被整合到RQS中。

2021年: 引入了智能设计运行(IDR),将基于规则和基于机器学习的特性结合到高效的时序闭环流程中。IDR具有内置的智能功能,可以做出复杂的决策,模拟专家的决策。流程的内部复杂性隐藏封装于一个简单的右键菜单项。

总的来说,自Vivado设计套件推出以来,我们一直致力于通过在时序收敛任务中构建智能来最大程度地减少手动干预,使用户腾出更多时间来专注于产品差异化,从而提高生产力。 IDR可以视为最新的产品进步,它将所有时序收敛构建块封装到一个强大的、密集型的编译中,并提供易于使用的按钮式运行方式,一定程度减少了用户时间和专业度的要求。

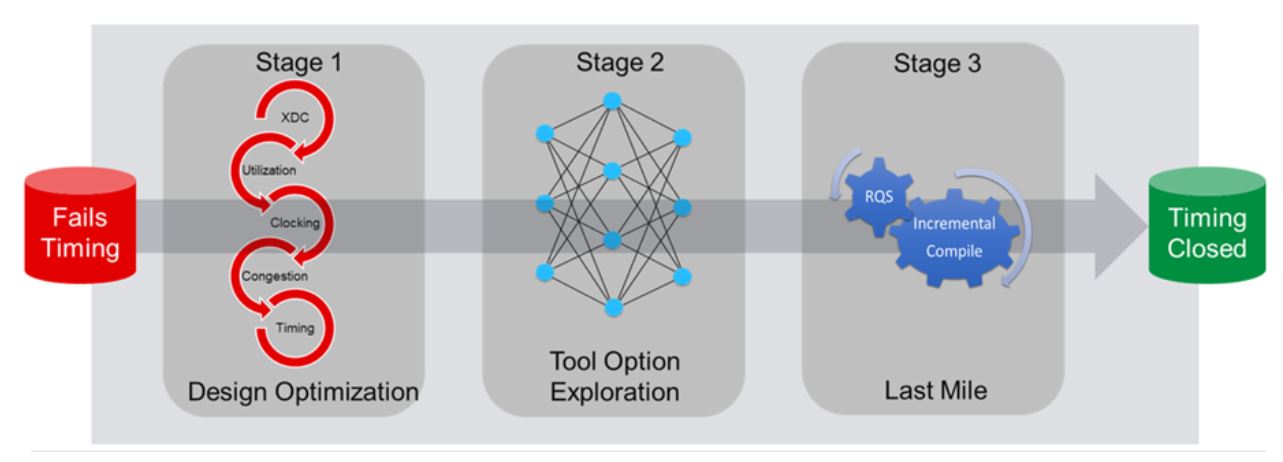

IDR总体分为3个阶段,流程示意图如下:

该流程是全自动化的,用户无法控制运行哪些阶段。在使用IDR尝试时序收敛之前,设计应没有方法学问题。建议运行report_methodology并修复或移除所有关键警告和警告。

IDR可以在以下任一条件下退出:

在任何阶段,如果时序满足且设计成功布线。

在阶段1,如果:

设计未通过初始时序检查。

设计未通过初始利用率检查。

工具选项激活了在方法学检查失败时退出,且存在ID为TIMING-6/7/8/13的方法学检查失败。

设计未能完成布线。

没有预测到机器学习策略。

在阶段2,如果未满足“最后一英里”标准。

在阶段3结束时,如果“最后一英里”算法已被耗尽且无法进一步改进。

以下是各阶段详情:

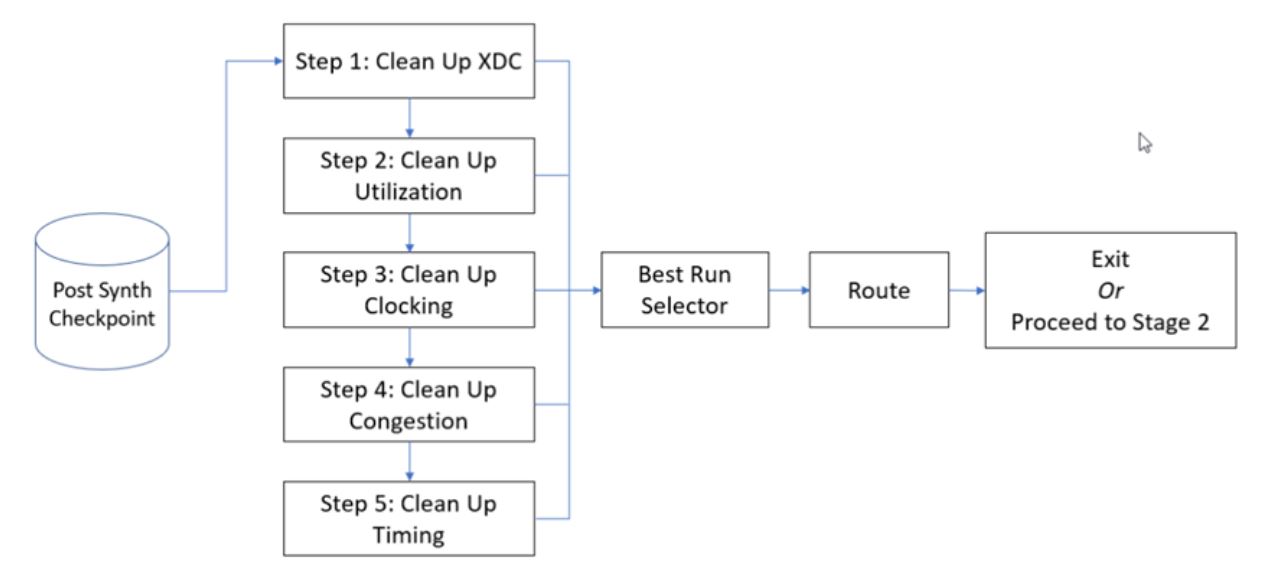

阶段1:设计优化

如果我们考虑一个标准的实现运行(即 opt_design、place_design、phys_opt_design 和 route_design),那么阶段1可以被认为是这些命令的多次执行。整个流程中会使用 report_qor_suggestions 和 report_qor_assessment 进行分析。当达到某些节点时,implementation会被重置,应用建议的修复措施重新跑implementation。

总体来说,这个过程最多可以发生4次。因为我们在进入精细调优过程之前,先得进行较大的修复。如果设计不需要修复,那么步骤将被跳过。在应用建议之后,工具会将新结果与旧结果进行比较,以确保没有出现任何意料之外的变化,并在必要时可以还原结果。

建议的应用顺序大致上与各步骤的类别名称对齐。

XDC 约束:主要是一个检查步骤,检查不可能满足的约束,通常是跨时钟域(CDC)上的时序约束导致的结果。在这个流程中没有建议能自动修复时序约束。如果时序无法满足, IDR 将提前退出。

资源利用率:考虑降低利用率但不降低关键路径时序的优化。分析主要基于网表,通过QoR 建议解决一些利用率问题。减少利用率通常可以缩短编译时间,有时还可以提高设计性能。

时钟:在任何 FPGA 设计中,正确的时钟配置都非常重要。这是对 QoR 影响最大的步骤,检查次优时钟拓扑和不平衡全局时钟树等问题。这一步将在可能的情况下应用自动修复,例如 CLOCK_DELAY_GROUP 约束和 MMCM 优化。然而,也有一些建议无法自动化,这些将在无法自动化时作为文本建议提供。

拥塞:这是另一个高影响步骤。解决拥塞的建议例子包括重新映射原语 MUXFs、CARRY8s、撤销 LUT 合并以及合并等效信号。它还可以通过进行小规模的布局规划floorplanning来减少因布局引起的拥塞。这种小规模的floorplanning涉及的负载数为几千,不会进行诸如 SLR floorplanning之类的大规模规划。

时序:这个步骤修复前阶段失败的时序路径。它可以做诸如复制驱动器、合并 LUT、重新映射控制集、展开 SRL 等操作。建议与失败路径一一对应。

第一阶段的问题类别与 QoR 评估所使用的问题类别相同。 RQA 在第 1 阶段自动运行,如果时序收敛得到改善,每一步的分数都会增加。由于应用修复时需要重置运行,编译时间最多可以达到默认运行的 4 倍。

第1 阶段(设计优化)是获得较大QoR增益的地方,这一阶段结束时,IDR决定是否退出或采用最佳运行结果进入第 2 阶段。

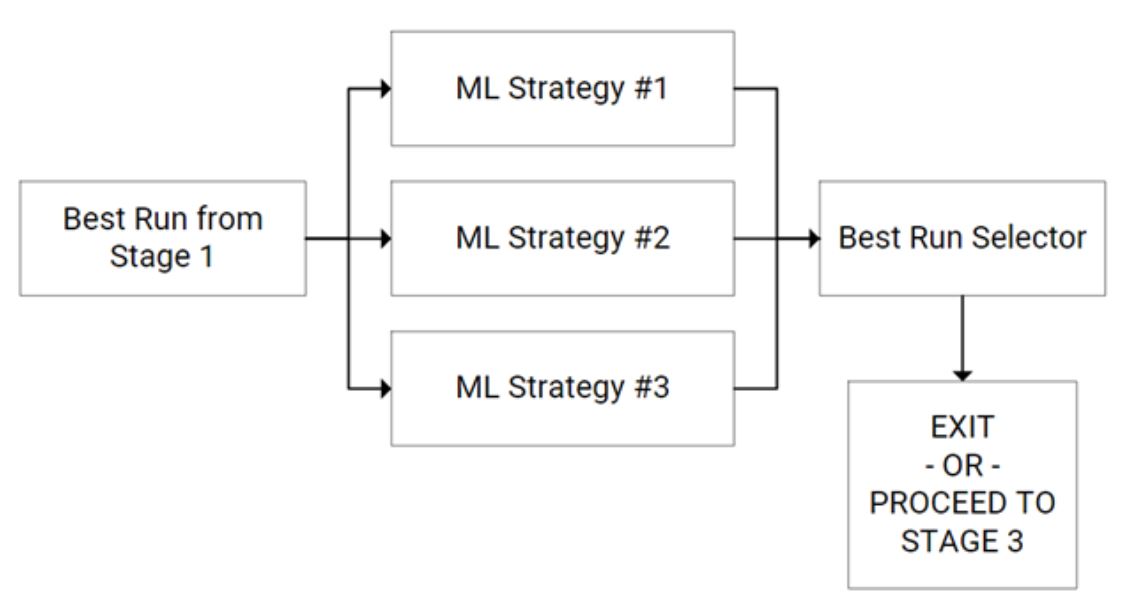

阶段2:工具选项探索

这一阶段旨在从工具选项中获取最大的QoR回报。利用基于机器学习的策略预测,这一阶段运行3个并行的implementation,继承第1阶段最佳运行的设计修复建议。

IDR流程的好处在于,对于没有重大方法学或时钟问题的设计,我们可以看到机器学习策略的性能有所提升。如果你以遵循良好方法学规则的设计进入IDR,那么第一阶段可以解决许多时钟问题。这就为机器学习策略的执行创造了合适的环境。

工具从众多可用的策略中选择3个排序最高的ML策略,因为整体来看,这有助于在不使用过多计算资源的情况下充分利用工具,也可以消除任何单次运行带来的 QoR 波动。

这些是并行进行的常规实现运行,因此这一阶段的长度等于一个实现运行的时间。在这一阶段结束时,表现最好的一个将被保留,另外两个将被丢弃。

这一阶段提供了另一个显著的QoR提升。许多设计将在这一阶段完成时序收敛。

阶段3:“最后一英里”时序收敛

阶段3被称为最后一英里阶段,致力于挖掘剩余的少量时序余量。第一阶段逐步从高影响到低影响解决时序问题,第二阶段探索布局和布线算法的解决方案空间。剩下的唯一实际操作是对剩余的关键路径进行精确打磨。这一阶段的优化在处理关键路径时尽量减少对布局和布线的干扰,并使用增量编译功能来实现这一目标。对于WNS < -0.100 ns的设计,大约有20%的设计能够实现时序收敛。

要从第一阶段或第二阶段进入“最后一英里时序收敛”阶段,设计必须满足以下条件:

布线完整

WNS > -0.250

RQA评分为3或更高

阶段3的目标是使设计的时序收敛。这与默认工具流程略有不同,默认流程旨在实现最佳的WNS并使WHS=0。算法必须在改善时序和不显著改变布局和布线结果之间取得平衡。为此,使用“最后一英里”增量指令和QoR建议来实现时序收敛。带有APPLIED属性的建议从参考运行中复用,而设置了INCREMENTAL_FRIENDLY属性的建议被应用。在布线完成后,可以运行phys_opt_design进一步尝试时序收敛。

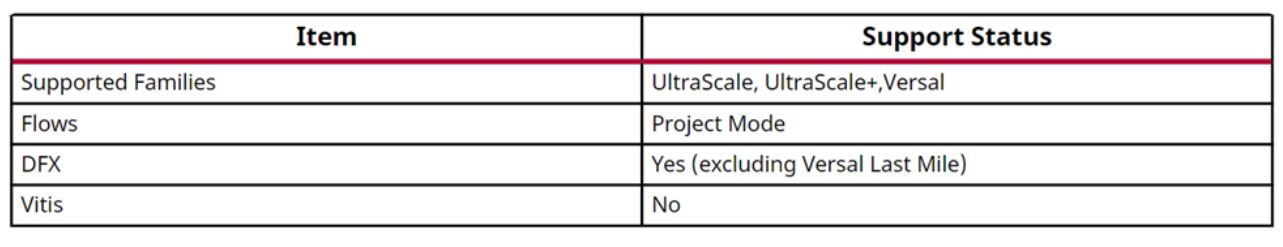

以下是到Vivado 2024.1为止IDR流程的支持类目汇总:

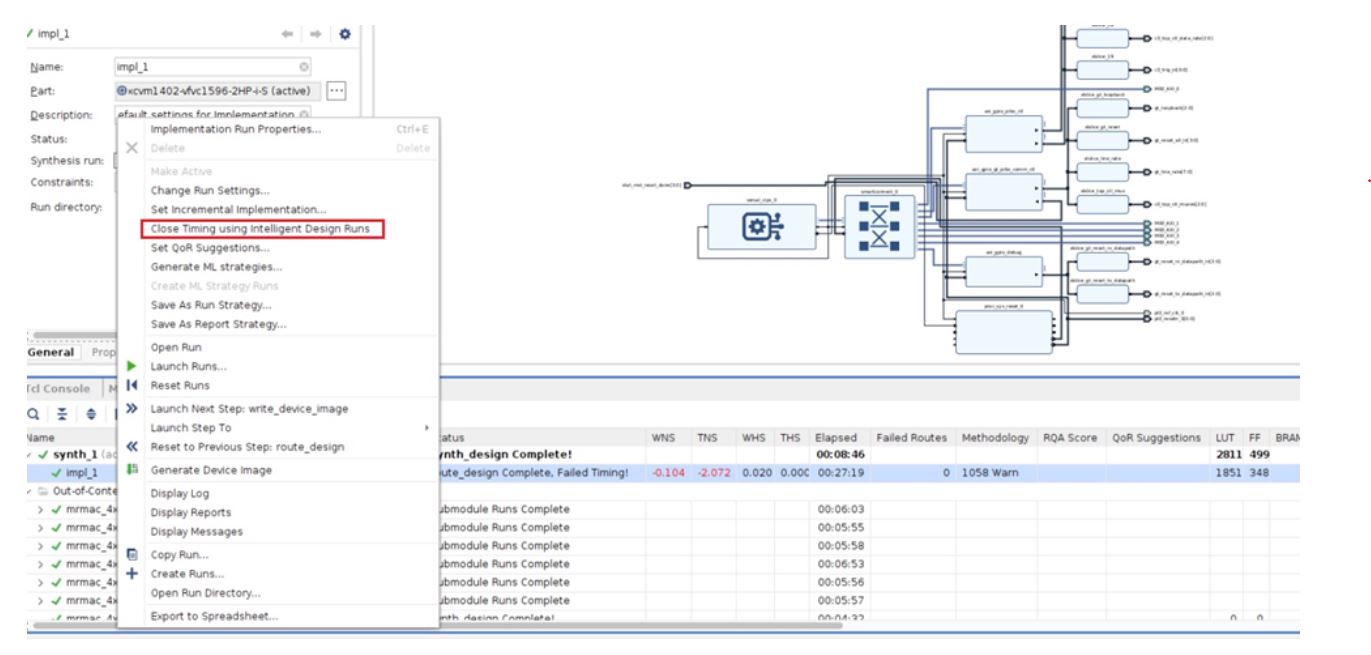

在Vivado的工程模式下,可以从标准的implementation run一键式创建IDR,只需从Design Runs窗口选中目标run,例如impl_1,右键菜单点击Close Timing using Intelligent Design Runs,如下图所示:

如果你想尝试再次执行此步骤以创建额外的IDR,你会发现该选项被禁用。由于directives由IDR控制,从具有相同网表、相同约束和相同pre/post Tcl的impl run中创建多个IDR没有意义。因此,从任何给定的实现运行中只能创建一个IDR。如果需要更多的IDR,请更改综合选项以创建不同的网表或修改floorplan。

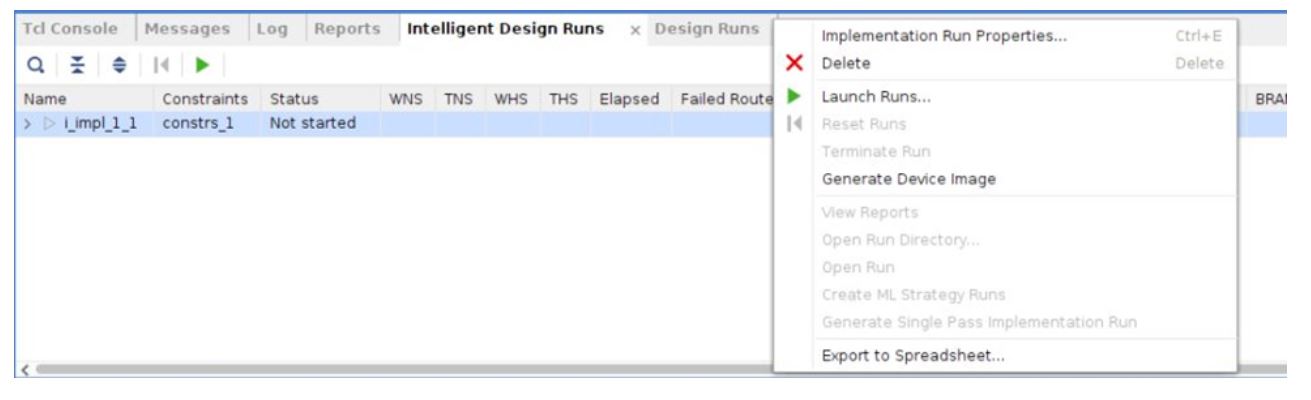

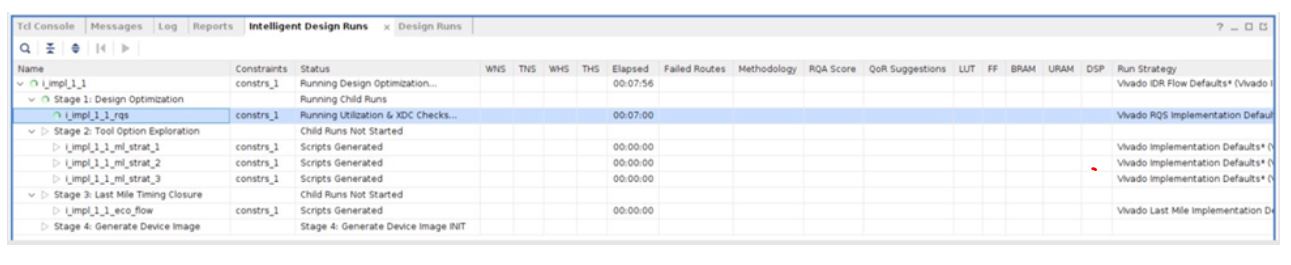

在Vivado IDE的底部,会自动打开一个Intelligent Design Runs的窗口,如果不小心关闭了,可由菜单Window → Intelligent Design Runs重新打开。在此窗口中右键菜单提供了当前阶段相关的流程控制选项,选择Launch Runs可以启动IDR。

展开i_impl_1_1 的层次结构可以看到不同的阶段

创建和启动IDR的等效Tcl命令如下:

create_run -flow {Vivado IDR Flow 2024} -parent_run synth_1 i_impl_1_1

set_property REFERENCE_RUN impl_1 [get_runs i_impl_1_1]

launch_runs i_impl_1_1 -jobs 24

wait_on_run i_impl_1_1

加黑部分可根据实际版本,需要参考的run及环境做调整。REFERENCE_RUN属性可用于从已有的impl run里面拷贝impl阶段的tcl.pre/post。

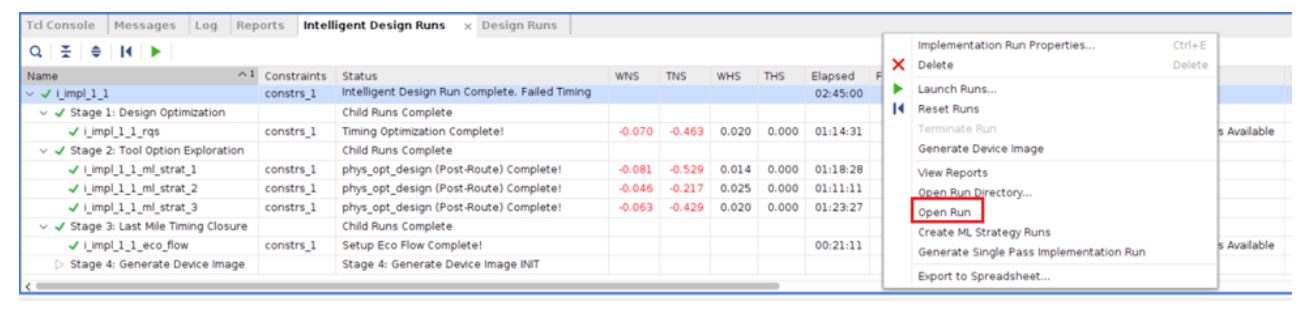

在IDR运行的过程中,各阶段的状态和结果会实时更新在Intelligent Design Runs Reports窗口。下图是IDR跑完后的Reports窗口状态。

如窗口注解所示,流程进度会显示运行的所有阶段,分别用$表示整体最佳run,*表示各阶段内的最佳run。同时,表格会显示一些统计数据,包括设计时序,RQA分数和拥塞信息, 并且为IDR 中生成的报告提供了超链接。

在工程的.runs文件夹下你会看到多了几个IDR相关的子文件夹:

在i_impl_1_1目录中,idr_flow summary.rpt 可视为上述Intelligent Design Runs Reports窗口等效的文本。除了报告链接外,它包含相同的信息。在i_impl_1_1_rqs目录下则包含了所有的report和一些中间阶段的dcp。

在IDR窗口中,右键单击顶层运行 impl_1_1,然后单击Open Run,这样会打开三个阶段中最佳run:

由于 IDR 可能需要相当于多次实现运行才能完成,如果要在一次run里面复刻其最佳结果,可同样在上图的右键菜单中点击Generate Singe Pass Implementation Run,按照提示创建run以后,可在Design Runs窗口看到新建的run。

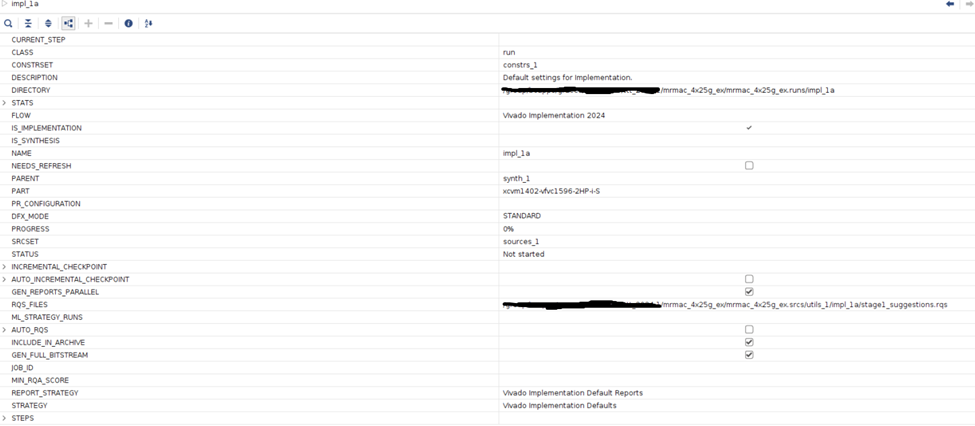

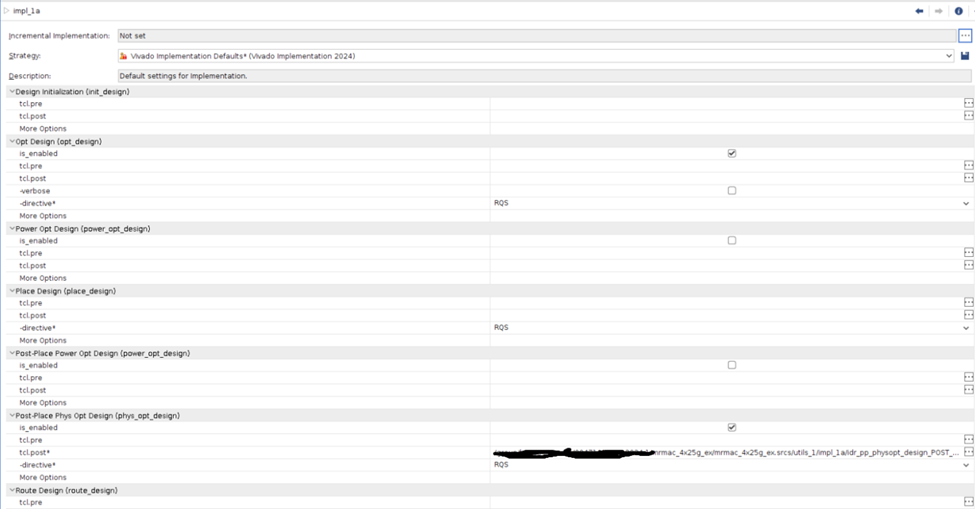

以新创建的名为impl_1a的single run为例,可以查看它的property和option,可以看到有RQS_FILES熟悉设置,并且流程中很多directive均为RQS。

最后提一下non-project模式下如何运行IDR。推荐的做法是创建一个Post-Synthesis Netlist类型的工程,加入能代表整个设计的单一dcp(通常是opt_design之后或者link_design之后opt_design之前导出的dcp)。在此工程中重复前文提到的步骤来创建IDR。

create_project <ProjectName> <ProjectDirectory> -part <PartName>

set_property design_mode GateLvl [current_fileset]

add_files -norecurse <Pre/PostOptDesign>.dcp