作者:Ken Zhang,来源:FPGA FAE技术分享选集

二、VE2302的DDRMC硬核介绍

在Versal器件中,有两种DDR4/LPDDR4控制器。一种是,它是通过配置NOC IP生成;另一种则是通过软核soft DDR4 memory controller IP生成。DDRMC硬核的性能更高,并且不额外占用其他的可编程逻辑资源(PL)。

2.1、DDRMC硬核中的资源

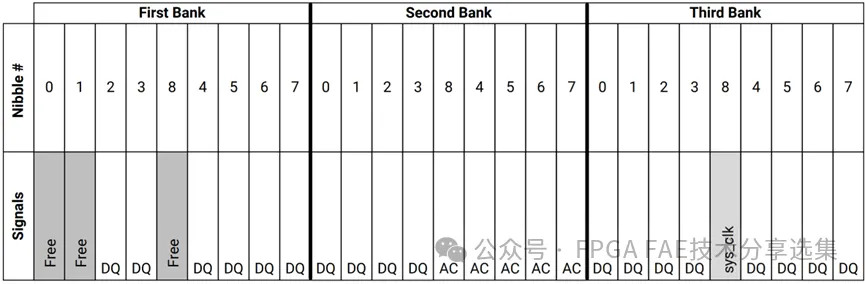

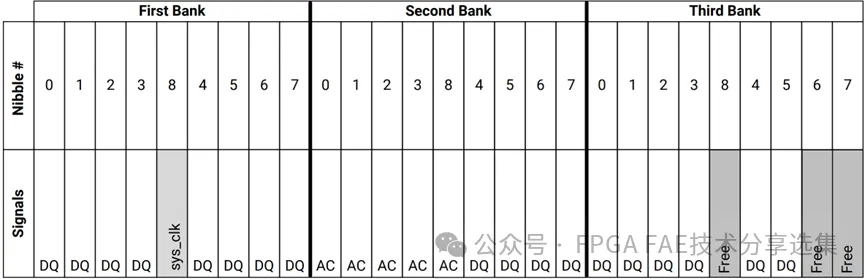

每个DDRMC硬核都有三个与之关联的XPIO存储体(称为一个Triplet)包括二十七个差分引脚对(L0P/N至L26P/N)。有九个Nibbles在一个Bank和每个Nibble都有六个引脚。

2.2、DDRMC硬核的管脚定义

NiPj:Ni是Bank中的Nibble数(其中i=0到8)

•MxPy:Mx是DDRMC的Triplet编号(其中x=0到(DDRMC总数-1))

•MxP0至MxP53是Triplet第一组中的引脚。

•MxP54至MxP107是Triplet第二组中的引脚。

2.3、DDRMC硬核的布线

• All Command, Address, Control, Clocks are fixed

• Allow swap of DQ bits within a nibble for x4 based DDR4

• Allow swap of DQ bits within byte for x8 based DDR4

• Allow swap of DQ bits within byte for LP4

支持的配置都有两个版本的引脚;非翻转和翻转。这个由于以下原因,可以使用翻转版本的引脚:

• 提供释放尽可能多不在收发器下方的引脚的选项以及用于用户系统设计的处理器系统。

• 为PCB布局工程师提供灵活性,以实现更好的信号布线。

图4 72-bit Multi-Rank L/RDIMM with ECC的Nibble(翻转)

三、VE2302的DDRMC硬核实战

3.1、 DDR4 Component类型

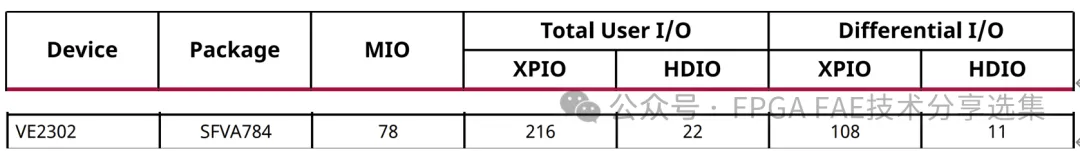

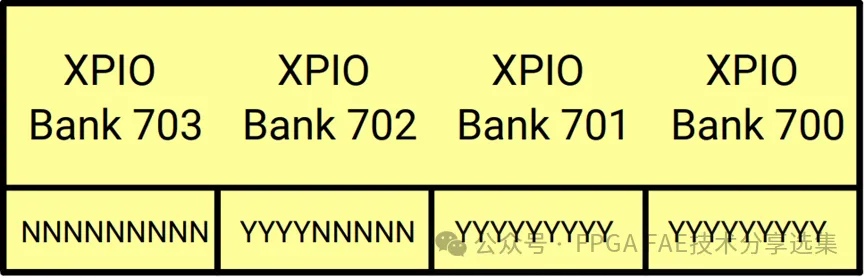

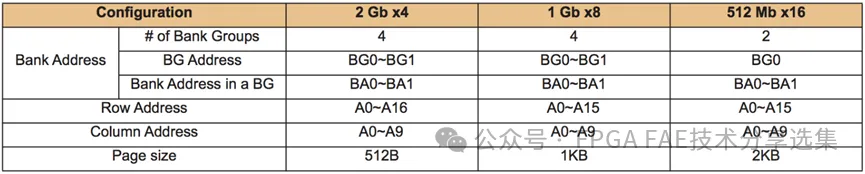

本设计采样4片1GB的DDR4芯片,型号为MT40A512M16LY-062E, 4片DDR4挂在BANK700,701和702的XPIO上,组成64位数据总线带宽和4GB的容量。

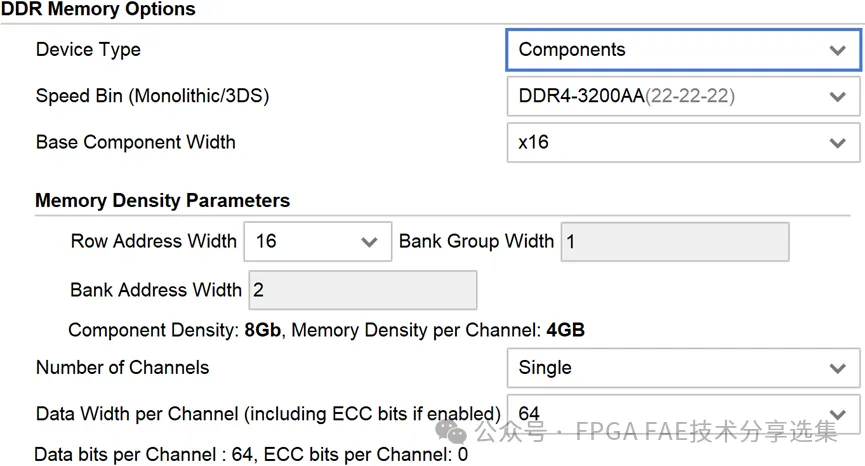

3.2、 DDRMC硬核配置(64位)

Versal的DDR4是通过NoC访问,因此需要添加NoC IP进行DDRMC硬核的配置。

VE2302的DDRMC硬核控制器,共连接4颗16bit DDR4。

图5数据位宽为64位的DDR4MC硬核的配置

数据位宽为64位的DDR4MC硬核共占用115个XPIO DDR only pins。具体分类如下:

1、数据线,

1)DQ[0:63]:2)DQS_t/DQS_c(0-7):2组差分数据选通。

2、地址线,

1)A[15:0] :其中WE_n/A13, CAS_n/A14, RAS_n/A15可功能复用。

2)BA[1:0] :bank地址线,bank是DDR4 SDRAM芯片内部的存储阵列,注意和rank区分。

3、时钟,

4、命令

1)CS_n:片选。

2)ACT_n:激活命令输入。

3)RAS_n/A15、CAS_n/A14、WE_n/A13:命令输入。ACT为低,RAS、CAS和WE作为行地址;ACT为高,RAS、CAS和WE作为命令。

4)PAR:校验位,使能后可以校验命令和地址线数据。

5)ODT(On-die termination):片内端接。将端接电阻移植到芯片内部,防止CPU发出的信号不能被电路终端完全吸收,形成反射,影响后面信号。ODT应用在DQ、DM、DQS引脚。

6)ZQ:ZQ校准。

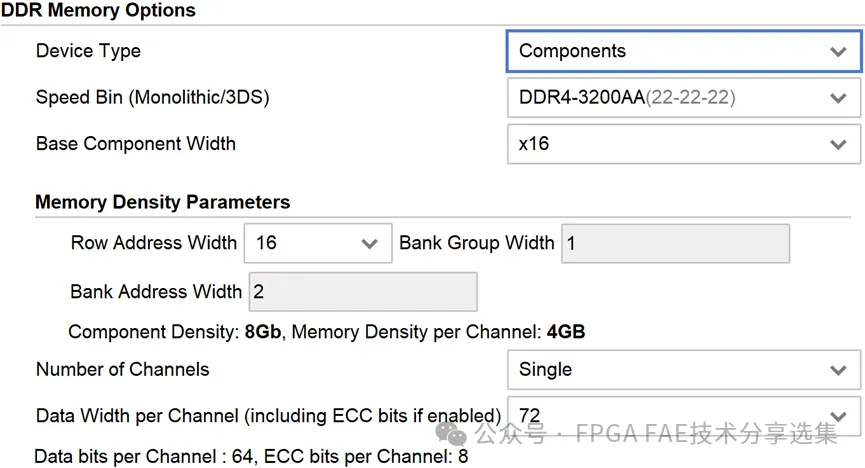

3.3、 DDRMC硬核配置(72位)

本设计中,数据位宽为72位的DDR4MC硬核共占用126个XPIO DDR only pins。

后续,基于VE2302的AI Edge和Vitis AI的示例工程也将于2024年Q4陆续发布,希望本文对广大工程师有所帮助。

欢迎读者联系我们进行沟通和讨论