作者:Meng Fancheng,AMD工程师;来源:AMD开发者社区

PCIe复位简介

PCI Express是一种即插即用协议,主机在启动时将枚举 PCIe设备。此过程包括主机从读取请求中获得每个设备的地址大小,然后为设备分配基地址。因此,PCIe 接口必须在主机查询时准备就绪,否则将不会分配基地址。PCI Express 规范规定,PERST# 必须在系统电源正常后 100 毫秒内解除,并且 PCI Express 端口必须在 PERST# 解除后不超过 20 毫秒内准备好进行Link training。这通常称为 100 毫秒启动时间要求。

对CIPS进行配置

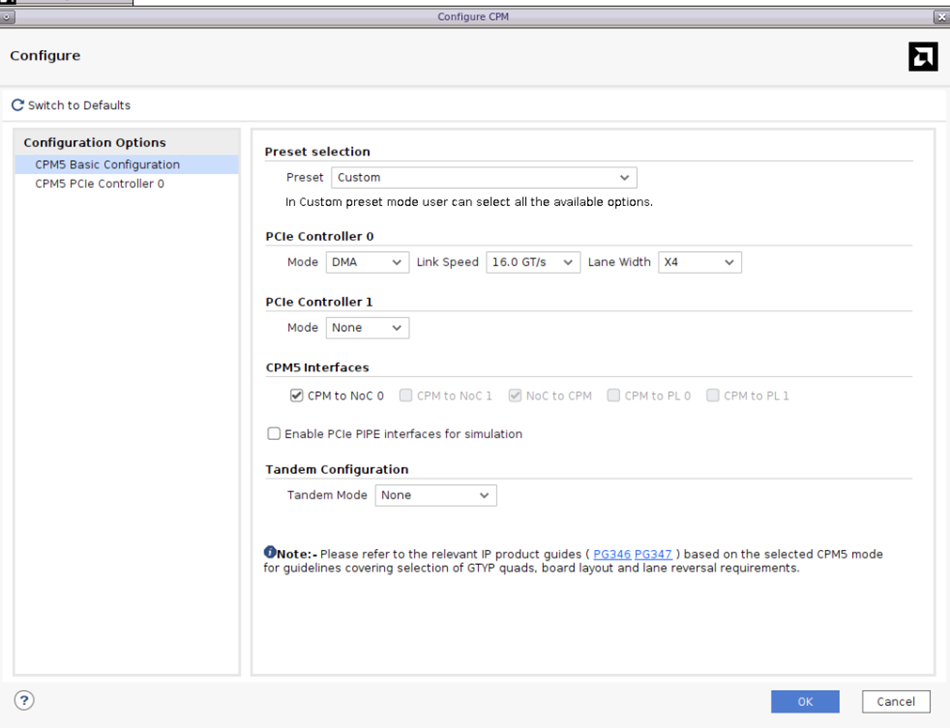

首先进入CIPS的CPM界面,选择所需要的PCIe配置,如图1所示,本设计的采用的是gen4x4(Link speed和Lane Width用户可根据自己的需求进行配置),mode必须要选择DMA模式。

图1

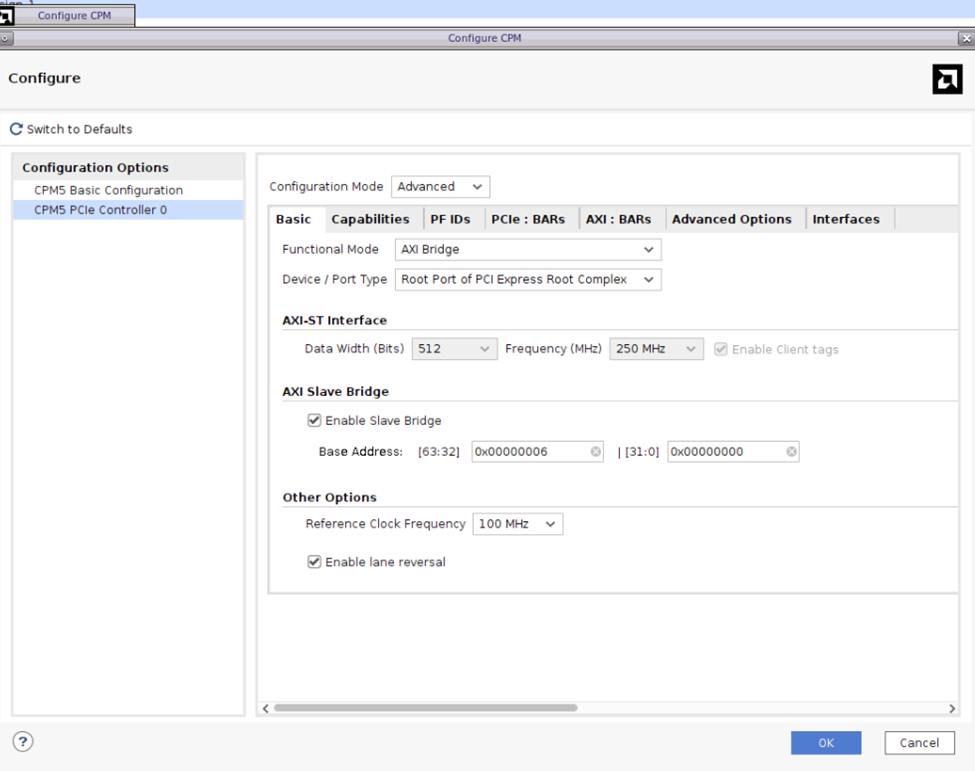

然后点击CPM5 PCIe Controller 0,在Basic界面,如图2所示,将Function mode选择为AXI bridge。 Device/ Port Type选择为Root Port of PCE Express Root Complex,其他界面可以应用默认配置。

图2

接下来需要对PS PMC进行配置,其他的配置页面不进行过多描述,详细可以参考CPM RP 的example design,本篇文章主要对IO界面的配置进行描述。因为在PCIe做RP时,需要控制与其连接的EP,对于不同的系统架构难以设计出一个普遍可行的方案,故RP的驱动在目前的版本并未对复位进行操作,PS PR的驱动可在下面链接中获取:

https://xilinx-wiki.atlassian.net/wiki/spaces/A/pages/85983409/Xilinx+PCIe+Root+and+EndPoint

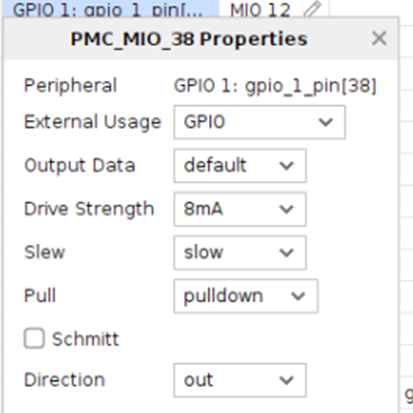

本篇文章通过举例来说明,用户如何根据自己的硬件电路设计来实现对EP端复位的控制,如下图3所示,MIO38为PCB板上金手指perst所连的pin脚,此时在PS PCM页面中不要将此管脚配置成PCIe reset管脚,而是需要将此管脚按照下图4配置为GPIO管脚。GPIO管脚的配置如图4所示,direction配置为out,并设置为PULL DOWN

图4

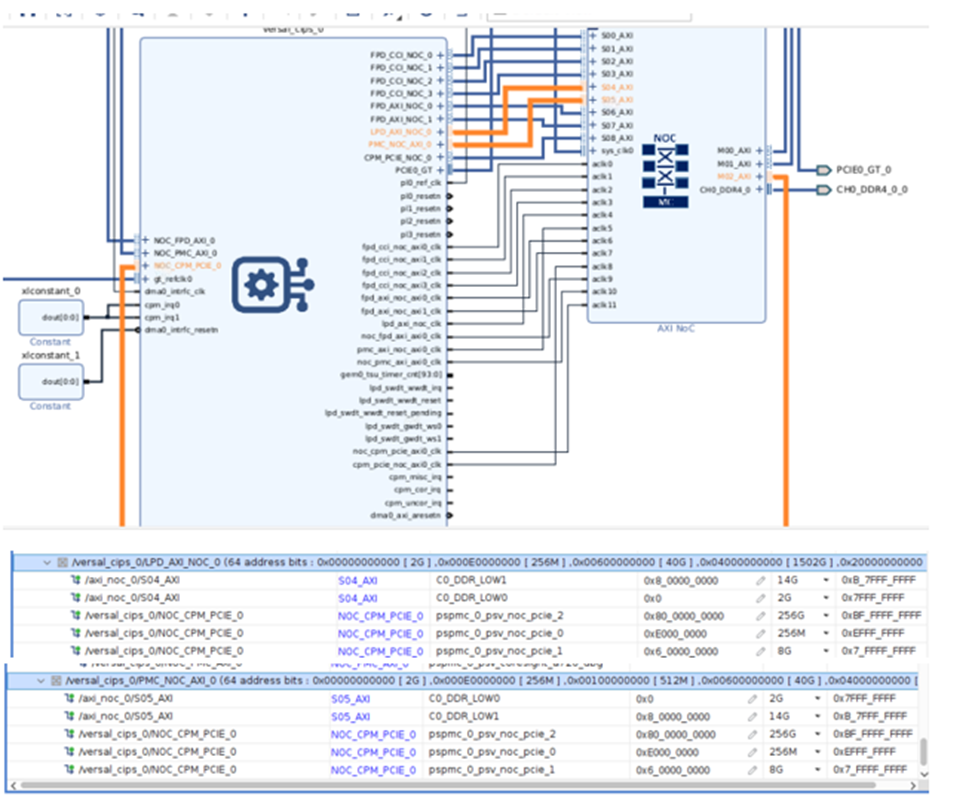

除了CIPS的配置需要注意之外,LPD_AXI_NOC_0和PMC_NOC_AXI_0两个接口需要连通到NOC_CPM_PCIE_0,如果LPD_AXI_NOC_0和PMC_NOC_AXI_0这两个接口没有连通到NOC_CPM_PCIE_0,那么此时CPU对PCIE的链路情况是无感知的,其会在Petalinux中打印PCIe link down,即使用户根据本篇文章对复位进行了配置,在PCIe debugger中看到LTSSM已进入L0,并且PCIe的link up信号已拉高,因为CPU与PCIE之间的链路没有打通,CPU无法感知到PCIE的状态依然会显示PCIe Link down。

图5

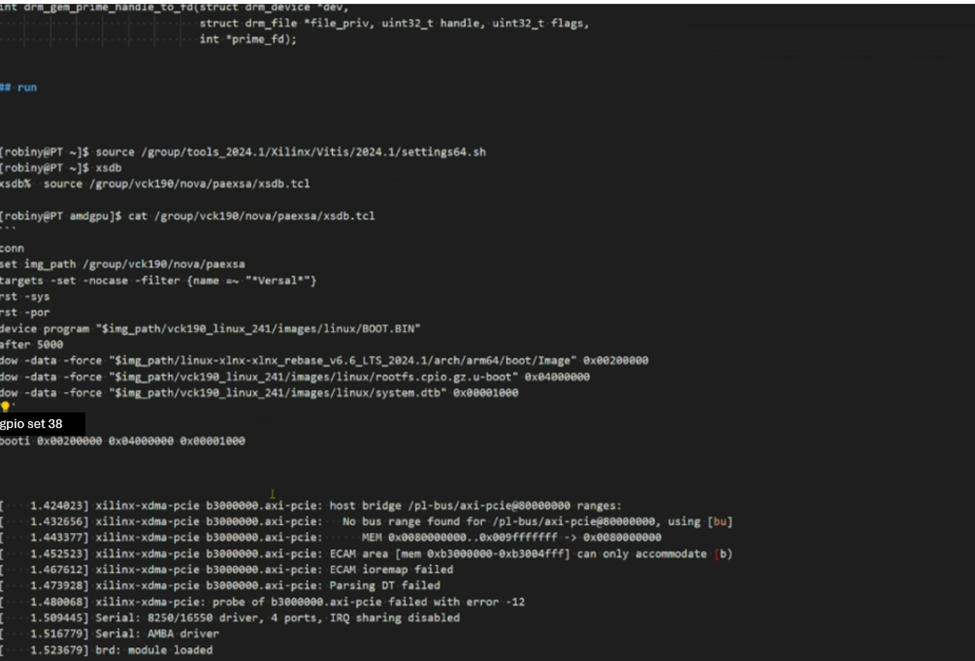

在Load Petalinux的image之前,需要运行指令gpio set 38,如下图6所示,这个指令是将PCIe的复位拉高,因为在CIPS中,是将复位MIO38配置成pull down,在此状态下PCIe处于复位状态,所以在load image前需要将复位拉高,使得双端进入link training状态,在运行petalinux时,会显示PCIe link up,接下来会完成PCIE的整个枚举流程。

图6