来源:内容编译自techspot,谢谢。

虽然芯粒(Chiplet)已经存在了几十年,但其使用在历史上仅限于特定的专业应用。然而,如今它们处于技术的最前沿,为全球数百万台台式电脑、工作站、服务器、游戏机、手机甚至可穿戴设备提供支持。 短短几年间,大多数领先的芯片制造商都已采用芯粒技术来推动创新。现在很明显,芯粒即将成为行业标准。让我们来探索一下是什么让它们如此重要,以及它们如何塑造技术的未来。

什么是芯粒?

芯片组是分段式处理器。它不是将每个部分整合到单个芯片中(称为单片方法),而是将特定部分制造为单独的芯片。然后使用复杂的连接系统将这些单独的芯片安装到单个封装中。

这种安排使得受益于最新制造方法的部件尺寸缩小,提高了工艺效率,并使其能够容纳更多的组件。

芯片中无法大幅减少或者不需要减少的部分可以采用更古老、更经济的方法生产。

虽然制造此类处理器的过程很复杂,但总体成本通常较低。此外,它还为处理器公司提供了一条更易于管理的途径来扩大其产品范围。

硅科学

要充分理解处理器制造商为何转向使用芯粒,我们必须首先深入研究这些设备的制造方法。CPU 和 GPU 最初是由超纯硅制成的大圆盘,直径通常略小于 12 英寸(300 毫米),厚度为 0.04 英寸(1 毫米)。

硅片经过一系列复杂的工序,形成多层不同的材料层——绝缘体、电介质和金属。这些层的图案是通过一种称为光刻的工艺创建的,其中紫外线照射到放大的图案(掩模版)上,然后通过透镜缩小到所需的尺寸。

这种图案以一定的间隔在晶圆表面重复出现,最终每个图案都会变成一个处理器。由于芯片是矩形的,而晶圆是圆形的,因此图案必须与光盘的周边重叠。这些重叠部分最终会被丢弃,因为它们没有功能。

完成后,使用探针对每个芯片进行测试。电气检查结果可让工程师根据一系列标准了解处理器的质量。这一初始阶段称为芯片分级,有助于确定处理器的“等级”。

例如,如果芯片要用作 CPU,则每个部件都应正常工作,在特定电压下在一定范围的时钟速度内运行。然后根据这些测试结果对每个晶圆部分进行分类。

完成后,晶圆被切割成可供使用的单个部件,即“芯片”。然后,这些芯片被安装到类似于专用主板的基板上。处理器在准备分发之前还要经过进一步的封装(例如,使用散热器)。

整个过程可能需要数周的制造时间,台积电和三星等公司对每片晶圆收取的费用很高,根据所使用的工艺节点,费用在 3,000 美元到 20,000 美元之间。

“工艺节点”是用来描述整个制造系统的术语。从历史上看,它们以晶体管的栅极长度命名。然而,随着制造技术的进步和允许使用越来越小的组件,命名法不再遵循芯片的任何物理方面,现在它只是一种营销工具。

尽管如此,每个新的工艺节点都比其前身带来好处。它可能生产成本更低、在相同时钟速度下消耗更少的功率(反之亦然),或者密度更高。后一个指标衡量给定芯片面积内可以容纳多少个组件。在下图中,您可以看到 GPU(PC 中最大、最复杂的芯片)多年来的发展情况……

工艺节点的改进为工程师提供了一种提高产品功能和性能的方法,而无需使用大而昂贵的芯片。然而,上图只展示了部分情况,因为并非处理器的每个方面都能从这些进步中受益。

芯片内的电路可分为以下几大类:

逻辑——处理数据、数学和决策 内存——通常是 SRAM,用于存储逻辑数据 模拟——管理芯片与其他设备之间的信号的电路 不幸的是,虽然随着工艺节点技术的每一次重大进步,逻辑电路的体积都在不断缩小,但模拟电路却几乎没有变化,而 SRAM 也开始达到极限。

虽然逻辑仍然占据芯片的最大部分,但近年来,当今 CPU 和 GPU 中的 SRAM 数量已显著增加。例如,AMD 在其 Radeon VII 显卡(2019 年)中使用的 Vega 20 芯片总共具有 5 MB 的 L1 和 L2 缓存。仅仅两代 GPU 之后,为 Radeon RX 6000 系列(2020 年)提供支持的 Navi 21 芯片就包含超过 130 MB 的组合缓存——显著增加了 25 倍。

随着新一代处理器的开发,我们可以预计这些成本将继续增加,但由于内存的缩小速度不如逻辑的缩小速度,在同一工艺节点上制造所有电路的成本效益将越来越低。

在理想情况下,人们会设计一个芯片,其中模拟部分在最大和最便宜的节点上制造,SRAM 部分在小得多的节点上制造,逻辑部分则保留给绝对尖端技术。不幸的是,这在实践中无法实现。不过,还有另一种方法。

分而治之

1995 年,英特尔推出了 Pentium II,这是其原始 P5 处理器的继任者。它与当时其他处理器的不同之处在于隐藏在塑料外壳下的设计:一块电路板容纳两个芯片。主芯片包含所有处理逻辑和模拟系统,而一个或两个单独的 SRAM 模块用作二级缓存。

虽然主芯片由英特尔制造,但缓存来自外部供应商。这种方法在 20 世纪 90 年代中后期成为台式电脑的标准配置,直到半导体制造技术的进步使得逻辑、内存和模拟系统能够完全集成到单个芯片中。

虽然英特尔继续尝试在同一封装中集成多个芯片,但它在很大程度上坚持所谓的单片处理器方法,即一个芯片可以实现所有功能。对于大多数处理器而言,不需要多个芯片,因为制造技术足够精湛(且价格合理),可以保持简单。

然而,其他公司对采用多芯片方法更感兴趣,其中最著名的是 IBM。2004 年,人们可以购买 POWER4 服务器 CPU 的 8 芯片版本,该版本包含四个处理器和四个缓存模块,全部安装在同一机箱内(称为多芯片模块或 MCM 方法)。

大约在这个时候, “异构集成”一词开始出现,部分原因是DARPA 所做的研究工作。异构集成旨在将处理系统的各个部分分开,在最适合每个部分的节点上单独制造,然后将它们组合到同一个封装中。

如今,这种技术更广为人知的名字是系统级封装(SiP),自诞生之日起就一直是智能手表配备芯片的标准方法。例如,Apple Watch Series 1 就在一个结构内安装了一个 CPU、一些 DRAM 和 NAND 闪存、多个控制器和其他组件。

通过将不同的系统全部放在一个芯片上(称为 SoC 或片上系统)可以实现类似的设置。但是,这种方法无法利用不同的节点价格,也无法以这种方式制造每个组件。

对于技术供应商来说,将异构集成用于小众产品是一回事,但将其用于大多数产品组合又是另一回事。这正是 AMD 对其处理器系列所做的。2017 年,这家半导体巨头推出了单芯片 Ryzen 台式机 CPU,并推出了Zen 架构。仅仅几个月后,AMD 就推出了两条多芯片产品线:Threadripper 和 EPYC,后者的配置最多可达四个芯片。

两年后,随着 Zen 2 的推出,AMD 全面拥抱了 HI、MCM、SiP(随便你怎么称呼它们)。他们将大部分模拟系统从处理器中移出,并将它们放入单独的芯片中。这些芯片采用更简单、更便宜的工艺节点制造,而其余逻辑和缓存则采用更先进的工艺节点。

因此,芯粒成为了流行的流行词。

越小越好

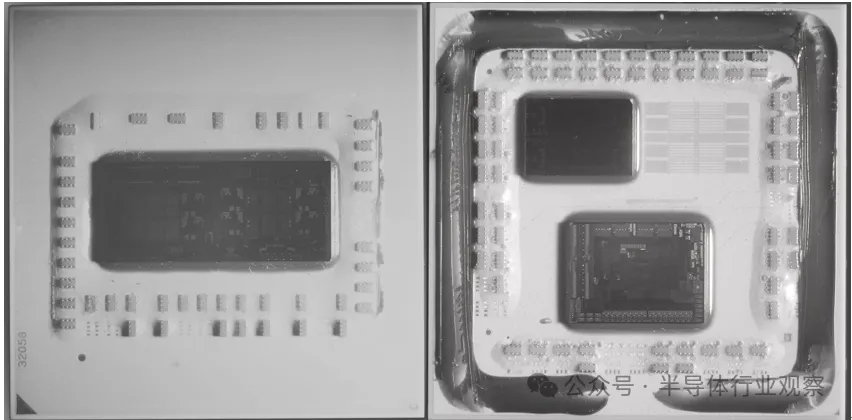

为了准确理解 AMD 选择这个方向的原因,让我们来看看下面的图片。它展示了 Ryzen 5 系列的两款较旧的 CPU——左侧的 2600 采用所谓的 Zen+ 架构,右侧的 3600 采用 Zen 2 架构。

两种型号的散热器均已拆除,照片是使用红外摄像机拍摄的。2600 的单个芯片内有 8 个内核,但此特定型号禁用了其中两个内核。

3600 也是如此,但在这里我们可以看到封装中有两个芯片——顶部的核心复合芯片 (CCD),包含核心和缓存,底部的输入/输出芯片 (IOD) 包含所有控制器(用于内存、PCI Express、USB 等)和物理接口。

由于两款 Ryzen CPU 都安装在同一个主板插槽中,因此两张图片基本上是按比例绘制的。从表面上看,3600 中的两个芯片的总面积似乎比 2600 中的单个芯片要大,但外表可能具有欺骗性。

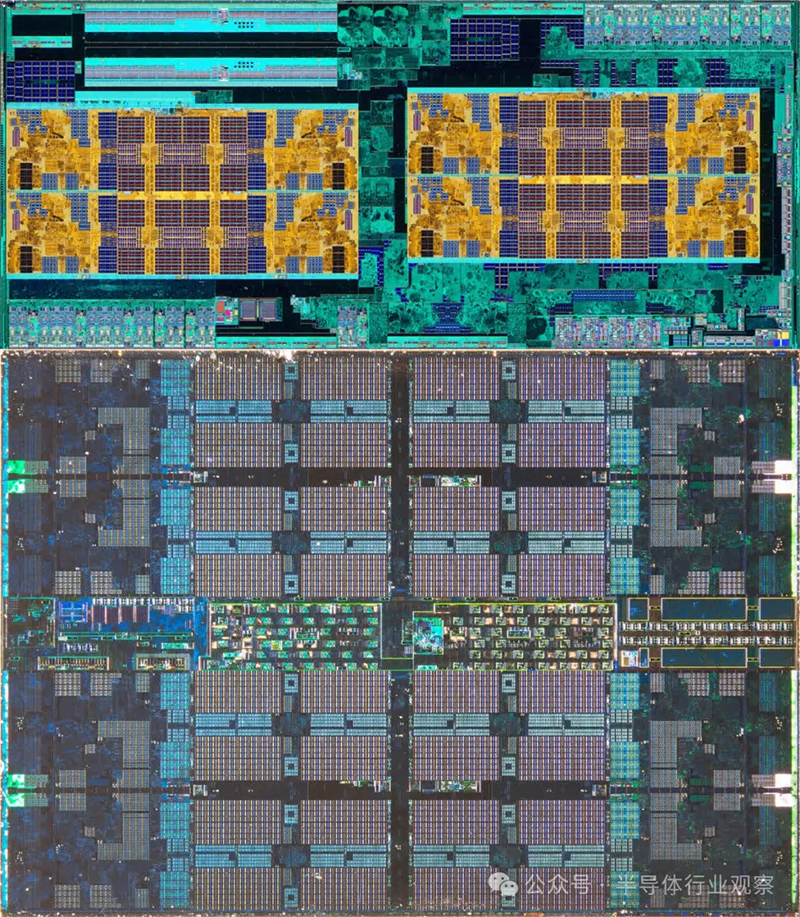

如果我们直接比较包含核心的芯片,就会清楚旧型号中模拟电路占用了多少空间——所有蓝绿色都围绕着金色核心和缓存。然而,在 Zen 2 CCD 中,只有极小的芯片区域专用于模拟系统;它几乎完全由逻辑和 SRAM 组成。

Zen+ 芯片面积为 213 平方毫米,由 GlobalFoundries 使用其 12nm 工艺节点制造。对于 Zen 2,AMD 保留了 GlobalFoundries 为 125 平方毫米 IOD 提供的服务,但利用台积电更先进的 N7 节点为 73 平方毫米 CCD 提供服务。

新款芯片的总面积更小,L3 缓存也增加了一倍,支持更快的内存和 PCI Express。不过,芯粒方法的最大优点是 CCD 的紧凑尺寸使 AMD 能够在封装中再装一个。这一发展催生了 Ryzen 9 系列,为台式电脑提供 12 核和16 核型号。

更妙的是,通过使用两个较小的芯片而不是一个大芯片,每个晶圆可以产生更多的芯片。以 Zen 2 CCD 为例,单个 12 英寸(300 毫米)晶圆可以比 Zen+ 型号多产生 85% 的芯片。

从晶圆上切下的切片越小,发现制造缺陷的可能性就越小(因为它们往往随机分布在光盘上),因此考虑到所有这些因素,芯粒方法不仅使 AMD 能够扩展其产品组合,而且成本效益更高——相同的 CCD 可用于多种型号,每个晶圆可生产数百个 CCD!

但如果这种设计选择如此有利,为什么英特尔不这样做呢?为什么我们没有看到它被用在其他处理器上,比如 GPU 上?

跟随领先

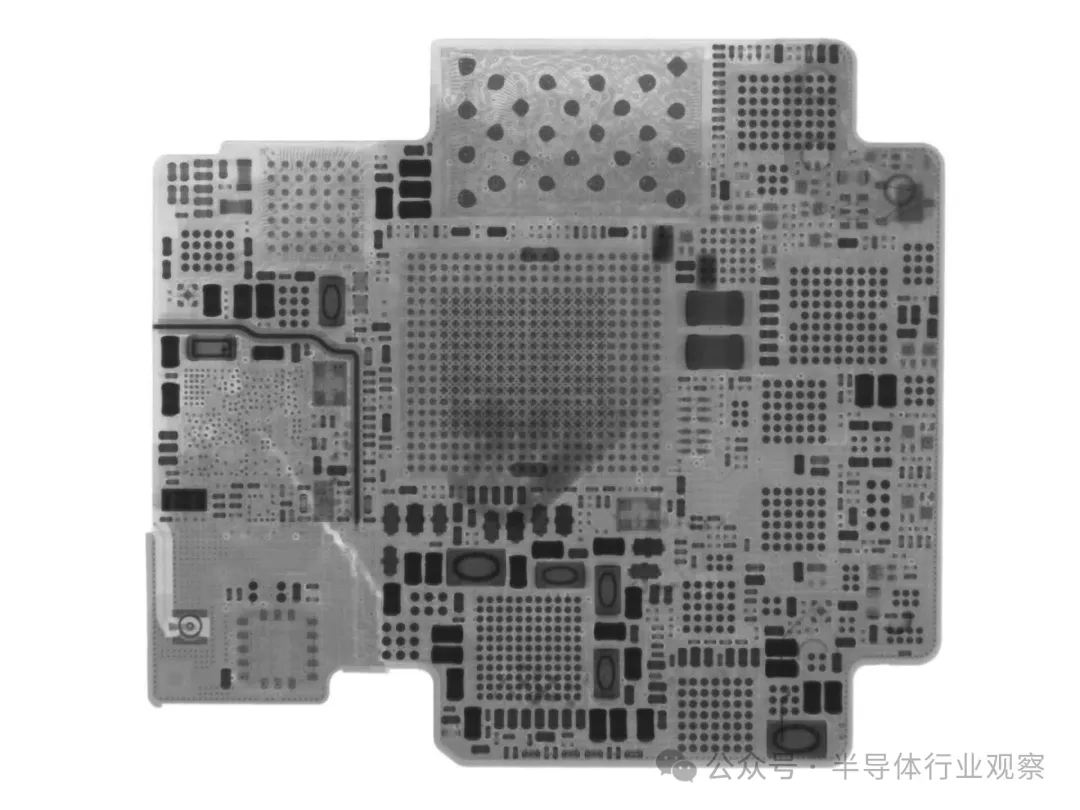

为了回答第一个问题,英特尔也在逐步采用芯粒技术。他们推出的第一款使用芯粒的消费级 CPU 架构名为Meteor Lake。不过,英特尔的方法有些独特,所以让我们来探索一下它与 AMD 的方法有何不同。

这一代处理器使用术语“tile”而不是“chiplet”,将之前的单片设计分成四个独立的芯片:

计算块:包含所有核心和 L2 缓存 GFX 模块:容纳集成 GPU SoC 模块:集成 L3 缓存、PCI Express 和其他控制器 IO 块:容纳内存和其他设备的物理接口 SoC 与其他三个块之间存在高速、低延迟连接,并且它们都连接到另一个称为中介层的芯片。该中介层为每个芯片供电,并包含它们之间的走线。然后将中介层和四个块安装到另一块板上,以便封装整个组件。 与英特尔不同,AMD 不使用任何特殊的安装芯片,而是拥有自己独特的连接系统(称为Infinity Fabric)来处理芯片数据交易。电力传输通过一个相当标准的封装进行,AMD 使用的芯片也更少。那么为什么英特尔会这样设计呢? AMD 的方法面临的一个挑战是,它不太适合超移动、低功耗领域。这就是为什么 AMD 仍然在该领域使用单片 CPU 的原因。英特尔的设计允许他们混合搭配不同的芯片以满足特定需求。例如,经济实惠的笔记本电脑的预算型号可以在任何地方使用小得多的芯片,而 AMD 为每个用途只提供一种尺寸的芯片。 英特尔系统的缺点是生产起来复杂且成本高昂(这导致了不同类型的问题)。然而,这两家 CPU 公司都完全致力于芯粒概念。一旦制造链的每个部分都围绕它进行设计,成本就会降低。

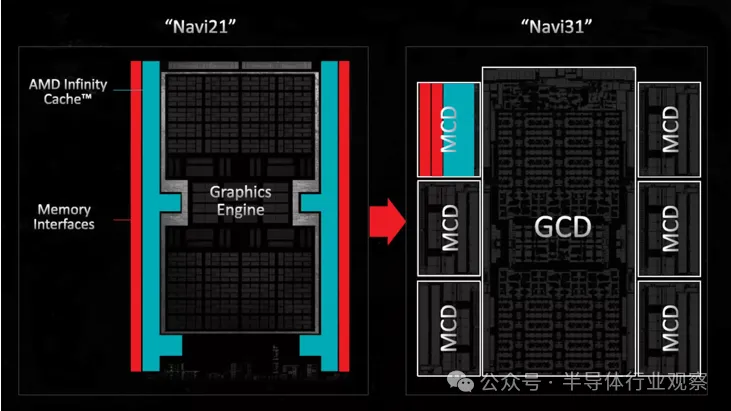

说到 GPU,与芯片的其余部分相比,它们包含的模拟电路相对较少。但是,内部的 SRAM 数量一直在稳步增加。这一趋势促使 AMD 在 Radeon 7000 系列中利用其芯片专业知识,其中Radeon RX 7900 GPU 具有多芯片设计。这些 GPU 包括一个用于核心和 L2 缓存的大型芯片,以及五到六个较小的芯片,每个芯片包含一个 L3 缓存和一个内存控制器。

通过将这些组件移出主芯片,工程师能够显著增加逻辑数量,而无需依赖最新、最昂贵的工艺节点来保持芯片尺寸可控。虽然这项创新可能有助于降低总体成本,但它并没有显著扩大 AMD 图形产品组合的广度。

目前,Nvidia 和 Intel 的消费级 GPU 尚未显示出采用 AMD 芯片方案的迹象。两家公司都依赖台积电完成所有制造任务,似乎满足于生产超大芯片,并将成本转嫁给消费者。

尽管如此,据悉,两家公司都在积极探索和实施基于芯片的架构,并将其应用于部分 GPU 设计中。例如,Nvidia 的Blackwell数据中心 GPU 采用芯片设计,其中两个大型芯片通过每秒 10 TB 的高速互连连接,可有效充当单个 GPU。

利用 chiplet 实现 Moore 算法

无论这些变化何时发生,基本事实是它们必须发生。尽管半导体制造技术取得了巨大进步,但每个元件的缩小程度还是有一定限度的。

为了继续提高芯片性能,工程师基本上有两种途径——增加更多逻辑,并增加支持逻辑所需的内存,以及提高内部时钟速度。关于后者,普通 CPU 多年来在这方面并没有显着改变。AMD的 FX-9590处理器(2013 年推出)在某些工作负载下可以达到 5 GHz,而其当前型号的最高时钟速度为 5.7 GHz(使用Ryzen 9 9950X)。

英特尔最高主频的消费级 CPU 是酷睿 i9-14900KS,双核最高睿频可达 6.2 GHz。这款“特别版”处理器保持着台式机 CPU 中开箱即用主频最快的记录。

然而,电路和 SRAM 的数量有所变化。前面提到的 AMD FX-9590 有 8 个内核(和 8 个线程)和 8 MB 的 L3 缓存,而 9950X 拥有 16 个内核、32 个线程和 64 MB 的 L3 缓存。英特尔的 CPU 在内核和 SRAM 方面也有类似的扩展。

Nvidia 的首款统一着色器 GPU 是2006 年推出的G80,它在一个面积为 484 平方毫米的芯片上包含 6.81 亿个晶体管、128 个内核和 96 KB 的二级缓存。快进到 2022 年,AD102推出时,它现在在 608 平方毫米的芯片面积内包含 763 亿个晶体管、18,432 个内核和 98,304 KB 的二级缓存。

1965 年,仙童半导体公司联合创始人戈登·摩尔 (Gordon Moore)发现,在芯片制造的早期,芯片内部元件的密度每年都会翻一番,而最低生产成本是固定的。这一观察结果被称为摩尔定律,后来根据制造趋势被解释为“芯片中晶体管的数量每两年翻一番”。

近六十年来,摩尔定律一直相当准确地代表着半导体行业的进步。CPU 和 GPU 的逻辑和内存的巨大进步很大程度上得益于工艺节点的不断改进,随着时间的推移,组件变得越来越小。然而,无论出现什么新技术,这种趋势都不可能永远持续下去。

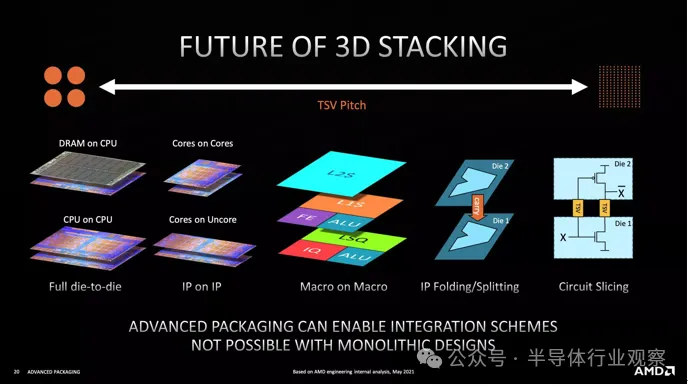

像 AMD 和英特尔这样的公司并没有等待这些物理极限被达到,而是采用了芯粒技术,探索将这些模块化组件组合起来的创新方法,以支持日益强大的处理器的创造。

几十年后,普通 PC 可能会配备手掌大小的 CPU 和 GPU。但是,剥开散热器,你会发现许多微型芯片——不是三四个,而是几十个,它们都巧妙地平铺和堆叠在一起。芯粒的主导地位才刚刚开始。