作者: Chris Yuan FPGA,来源:FAE技术分享选集

介绍SEM之前,需要先介绍一下SEU,SEU全称:Single Event Upset,中文译作单粒子翻转事件;单粒子翻转是指意外情况(辐射或高能粒子攻击)导致单个存储单元出现了状态错误;这种错误并不是永久性的,可以在重新编程或重新上电后恢复,但是如果不对错误进行及时纠正,可能就会导致设备运行与设计预期不符,出现功能异常。

针对这一问题,Xilinx推出了SEM IP, SEM全称是Soft Error Mitigation,SEM的作用就是通过ICAP不断扫描FPGA内部的CRAM(Configration RAM),来及时发现FPGA运行过程中出现的SEU错误,并完成错误纠正,以保证器件能及时恢复正常工作状态。SEM并不能完全避免SEU导致的软件错误,它只能帮助器件在发生SEU错误之后,从故障状态中恢复过来,在一定程度上,可以提高系统设计的可靠性。

这里需要注意一点:由于SEM会占用ICAP,如果设计中有其他应用(比如:multiboot/Partial Reconfiguration)也需要使用ICAP,那么就会出现ICAP的使用权冲突,需要注意ICAP的仲裁,这个官方有一个参考设计XAPP517。

下面主要从应用的角度出发,介绍一下,如何使用SEM IP。

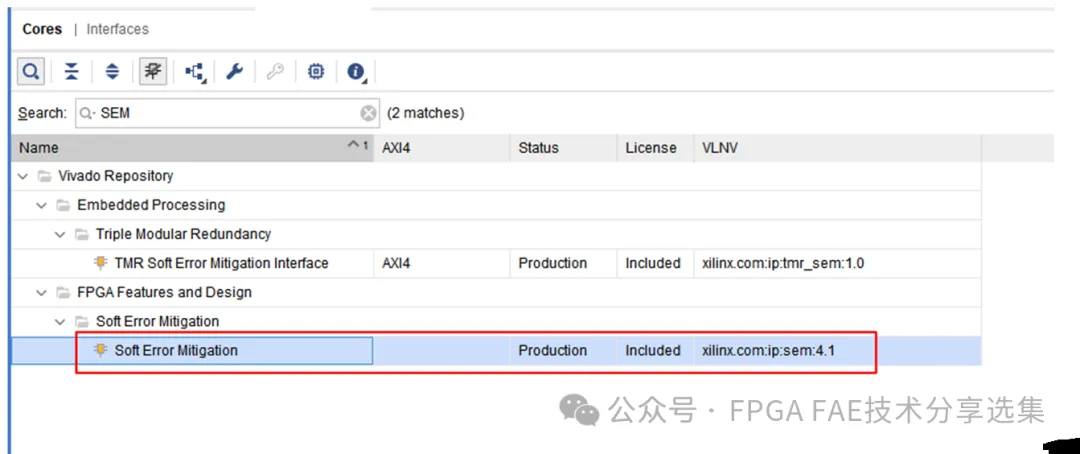

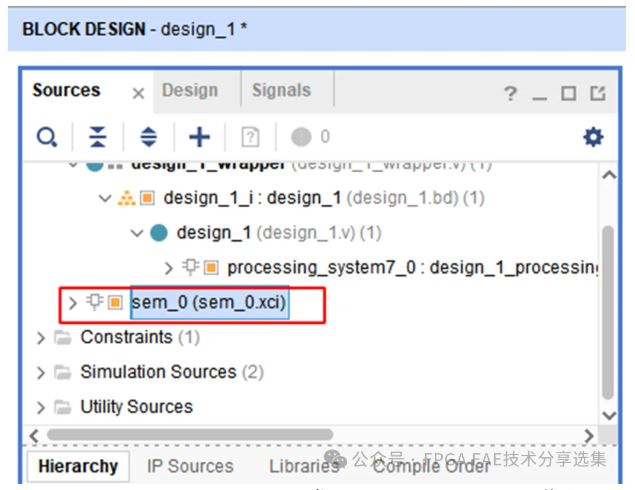

二、SEM IP核配置

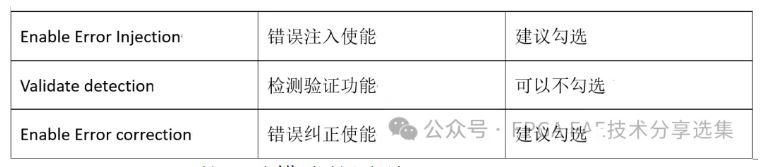

双击打开IP的配置页面,这里默认配置如下,非特殊需求,建议按照默认配置使用:

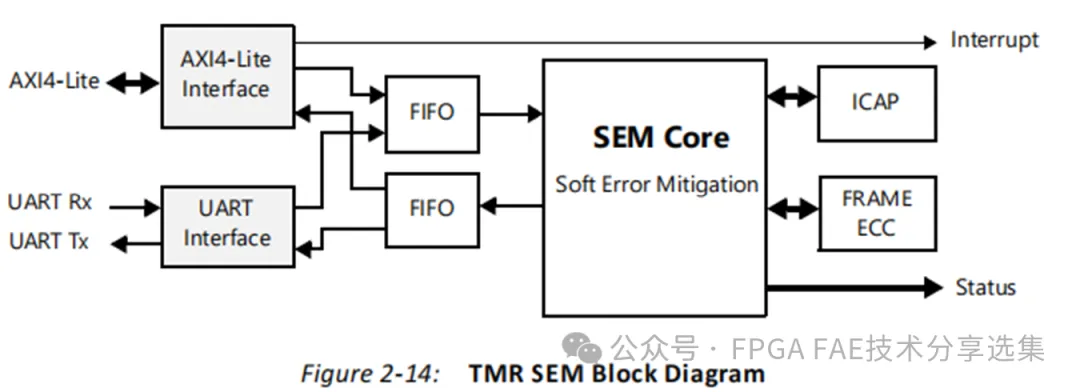

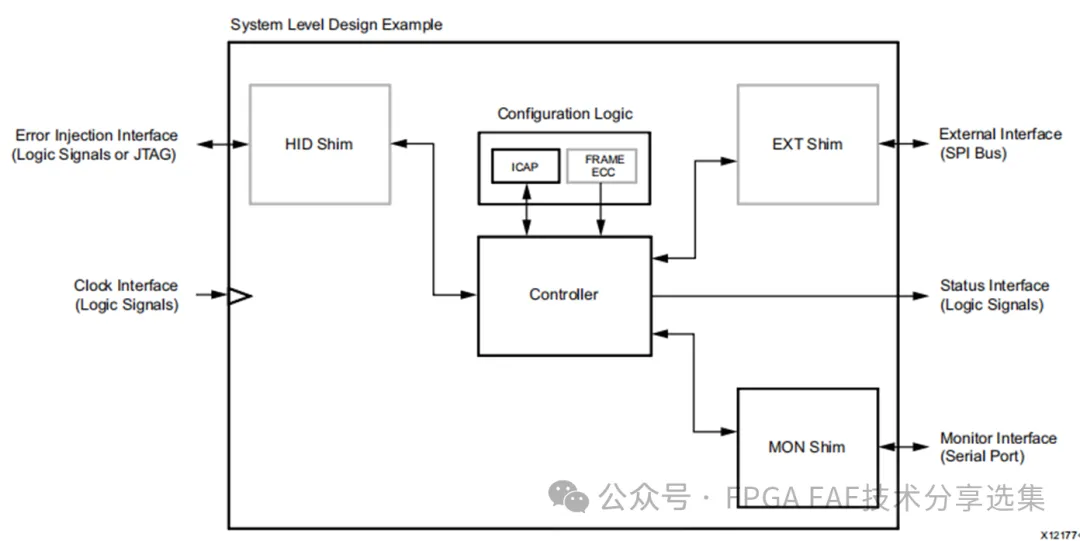

接下来就是考虑如何将example design和我们的原工程结合起来,我们先看一下example design 的框图:controller就是我们生成的SEM IP,configuratio Logic就是内部的动态配置单元;另外还有3个Shim模块:

A. HID Shim:就是一个VIO,将状态信号和错误注入信号接入VIO,完成对SEM的错误注入和状态观测,这个模块不是必要的,我们可以将状态信号引到IO进行观测,或者引到ILA等,这个用户自行决断;如果是通过VIO控制注入,在IP配置的时候就一定要选择Vivado Lab Tool.

B. EXT Shim:是外部flash的驱动模块,只有当使能replace/classification才需要使用这个模块;

C. MON Shim: 这个一个串口监控模块,串口模块可以通过打印信息判断当前SEM进入什么状态,串口模块也可以通过命令实现状态切换和错误注入等功能;这个模块实现的功能和HID模块实现的功能是一样的,只是一个是通过串口发命令,一个是通过JTAG/IO直接控制信号;另外,串口注入错误是独立于VIO或pin的一条路径,不管IP配置时选择Vivado Lab Tool还是pins都可以通过MON 串口完成错误注入。

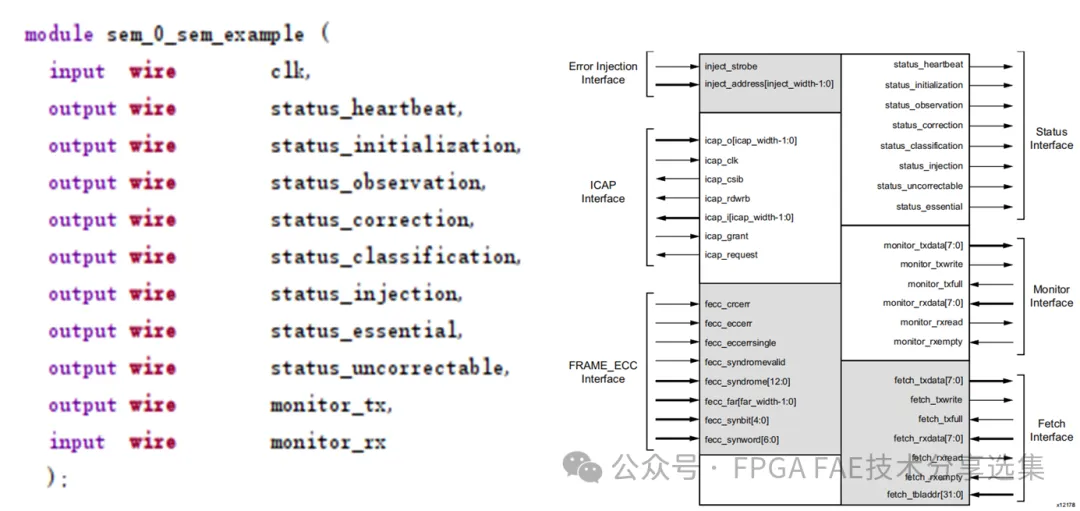

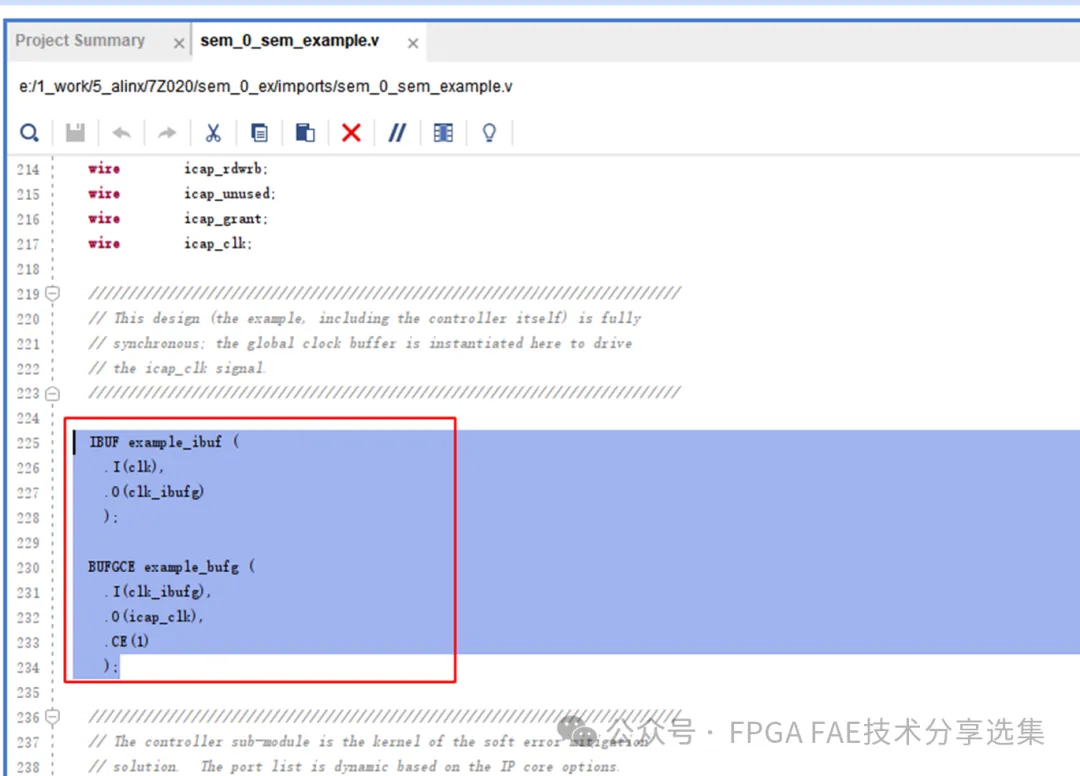

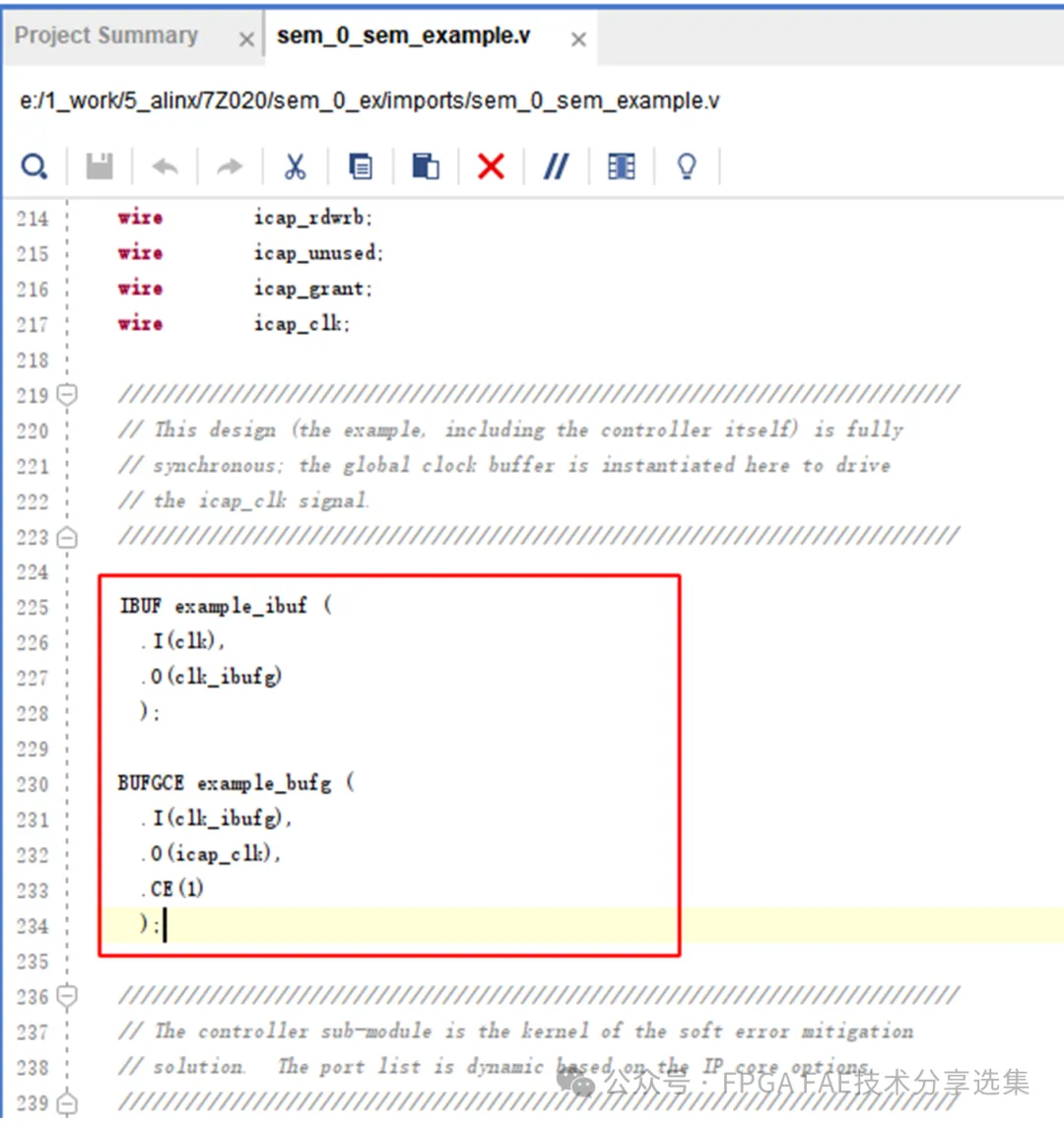

接下来我们再看一下example design的顶层,其实就只有状态输出和串口两个信号,状态输出其实都可以不用引出,真正需要的就只有时钟和串口;但如果我们直接调用IP的话,其接口就是右边这个;所以十分推荐大家通过example design来简化设计。