作者: Fisher Yang,来源:FPGA FAE技术分享选集

RFDC这部分一共有5种电源:

A. ADC_AVCC

B. ADC_AVCCAUX

C. DAC_AVCC

D. DAC_AVCCAUX

E. DAC_AVTT

前两种和ADC有关,后3种和DAC有关。硬件设计需要注意如下3个事项:

1. 电流大小:这几种电源的电流大小,可以使用XPE工具评估。 在AMD网站搜索XPE,下载对应的Excel表格填写ADC和DAC的数量,频率等,EXCEL表格会给出每种电源的电流。额外再留一些余量即可。

2. 电源质量:DS926文档上面标注了这几种电源的最大最小值,从要求来说,在文档指定的范围即可。例如ZCU208,这几路电源就直接用DC-DC搭建。实际测试中,这几个电源对性能的影响非常大。所以如果对电源设计不太放心,就用LDO供电即可,如果LDO可以选择low noise、high PSRR的LDO,那就更好了。

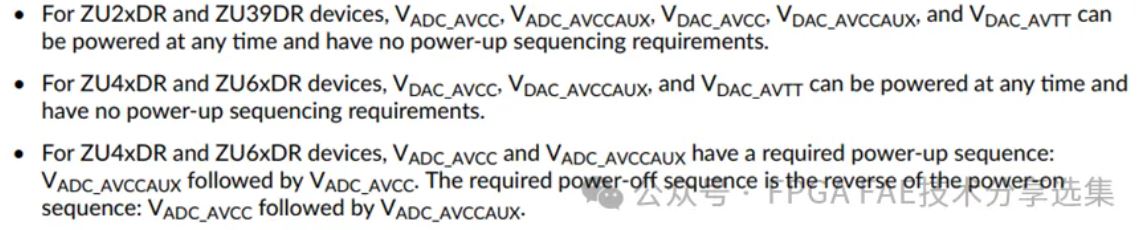

3. 上电顺序:DS926讲述了这几个电源的上电顺序要求,这里贴图说明。

上电顺序总体也没什么复杂要求,DAC的3种没有要求,ADC的2种有先后顺序。

上电顺序总体也没什么复杂要求,DAC的3种没有要求,ADC的2种有先后顺序。

此外,还有SYSREF时钟,这是一个低频时钟,用于同步,DS926有对这个时钟的要求。

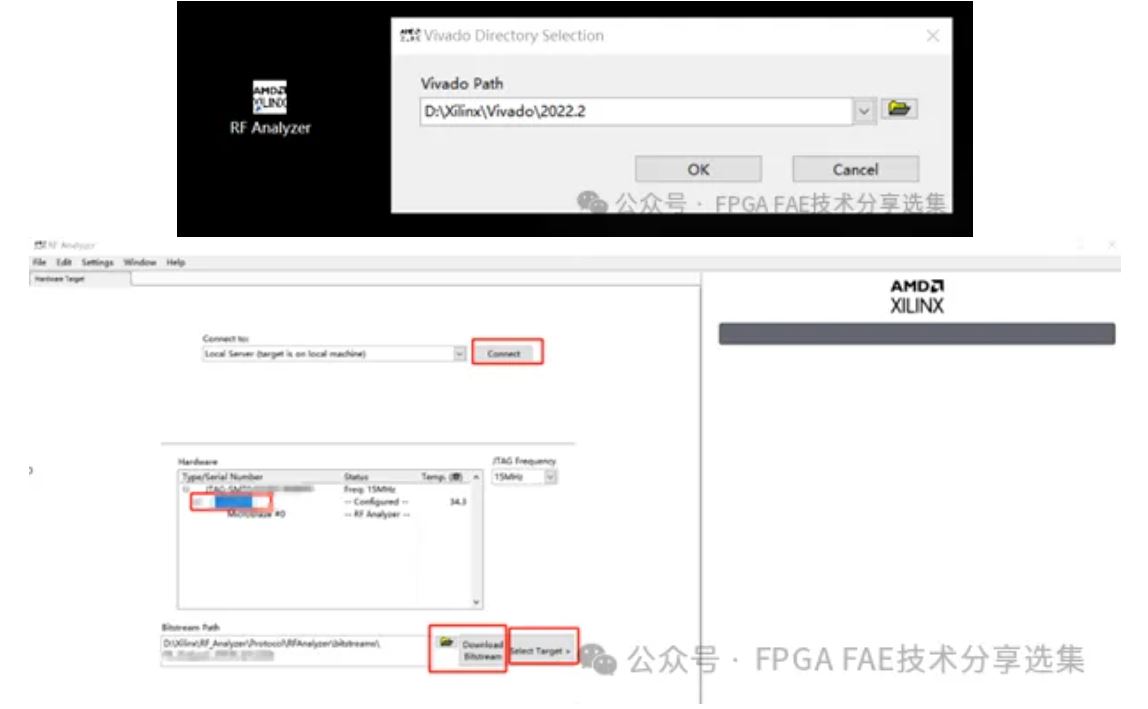

1. 官网下载并安装与Vivado版本对应的RF Analyzer版本;

2. 板子上电后,连上JTAG,双击安装好的RF Analyzer图标,设置Vivado路径并启动GUI。然后在接下来的GUI上点击Connect,然后选择RF Analyzer安装目录中提供的预建的比特流,它们位于安装目录RF_Analyzer\Protocol\RFAnalyzer\bitstreams,也可以选择自己建的Vivado工程生成比特流,点击Download Bitstream;

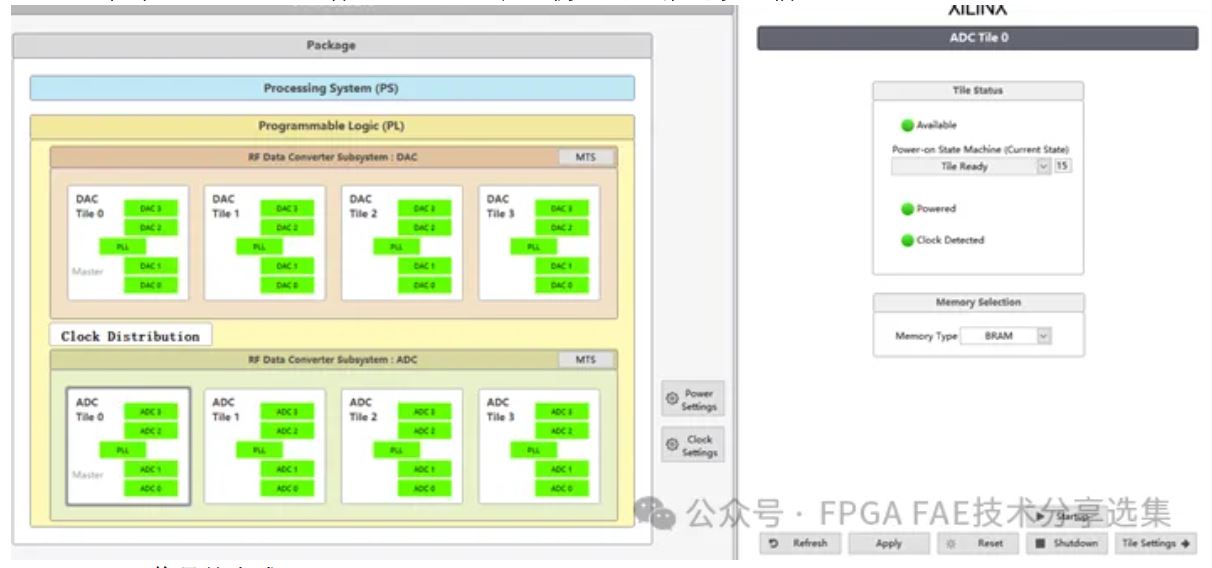

3. Download Bitstream之后,然后点击Select Target,RF Analyzer将读取RFDC IP配置,当设备配置读取完成后,将看到类似以下的界面;注意外部参考时钟应存在,并且其频率应与RFDC IP配置所需的频率相匹配。否则,ADC和DAC Tile可能无法完全启动和运行。

4. 单击ADC Tile 0-3或者DAC Tile 0-3,右侧将显示所选的Tile信息;

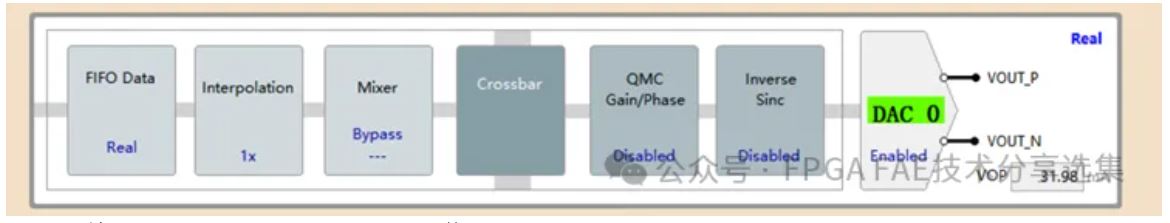

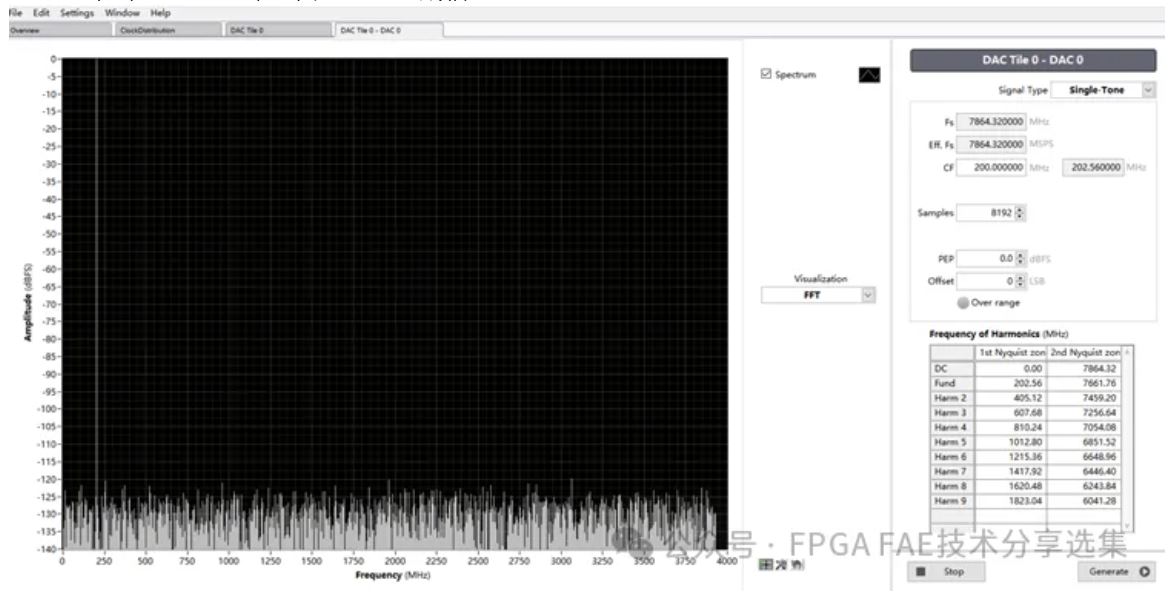

5. DAC信号的生成:

A. 双击DAC Tile 0;

B. 然后再双击DAC通道0;

C. 单击Generate即可由DAC 0生成信号。

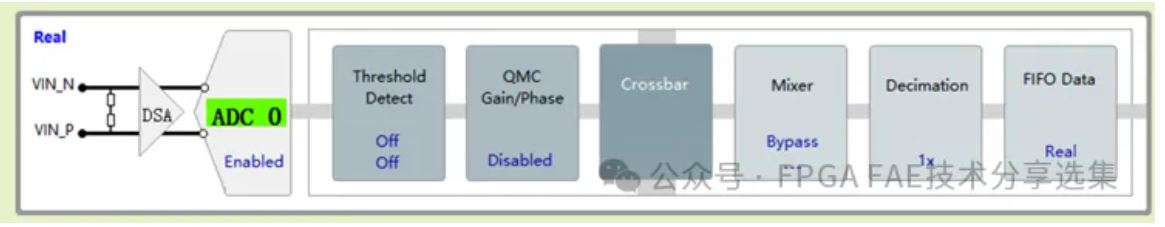

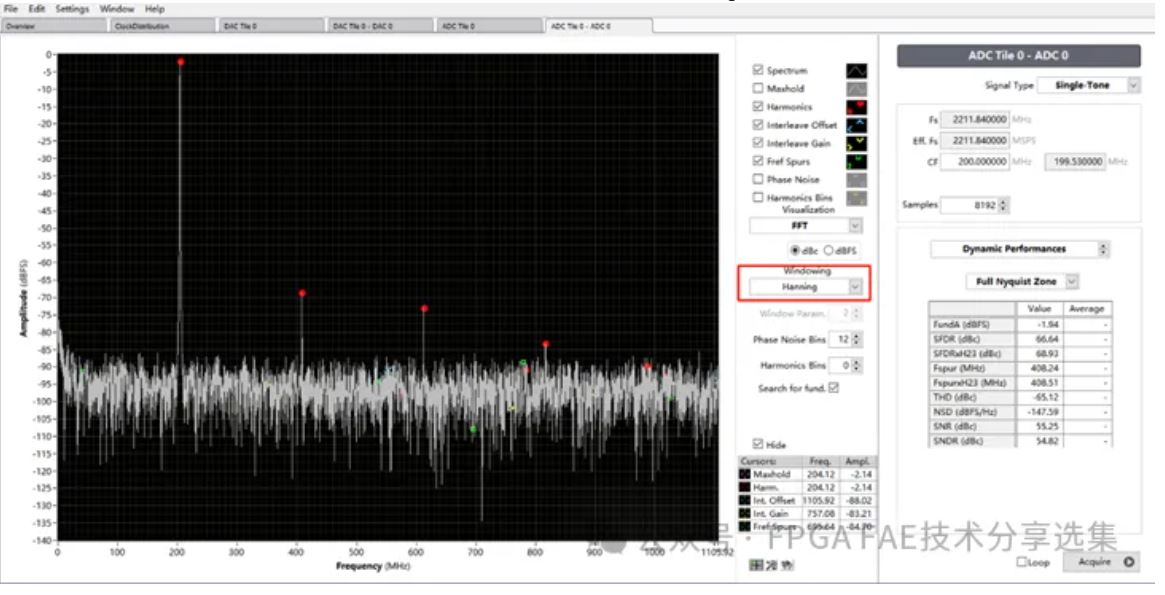

6. ADC信号的采集:

A. 双击ADC Tile 0;

B. 然后再双击ADC通道0;

C. 板子上将DAC0和ADC0使用SMA线环回,单击Acquire即可查看从DAC Tile 0_DAC 0的环回信号。减少由于采样不连贯性造成的频谱失真,可在界面上选择Hanning窗。

7. RF Analyzer还可配置ADC参数、DAC参数、时钟参数等,大家可以实际上板测试一下,这里不再一一介绍。

7. RF Analyzer还可配置ADC参数、DAC参数、时钟参数等,大家可以实际上板测试一下,这里不再一一介绍。

如果您对RFSoC系列有需求或者有疑问,欢迎联系: