概要

测试和测量系统的主要任务之一是记录尽可能多的测量值。在这种情况下,基于FPGA的解决方案的优势就体现出来了,如固有的并行性、极高的带宽、灵活性、支持多种接口和集成CPU。如果同时使用FPGA模块作为基础,那么额外的硬件设计通常会简化为开发一个复杂度低、组件数量少的简单基板。这种方法大大降低了项目风险、开发时间和成本。

解决方案

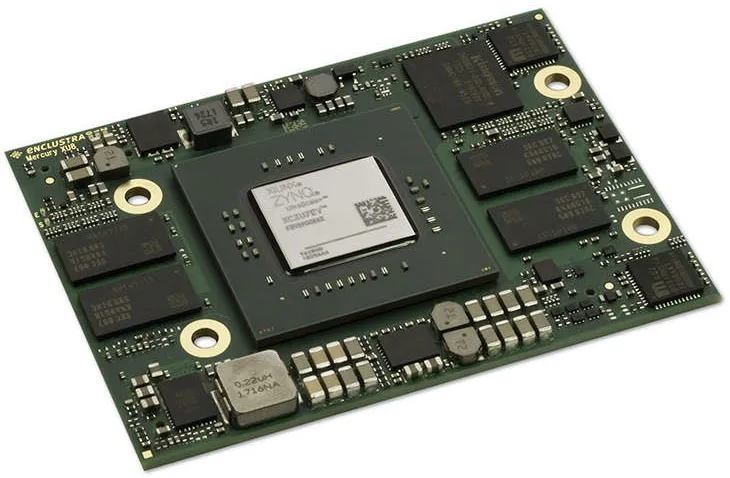

所有这些都促使客户委托Enclustra开发数据记录器,以升级现有的测量系统。为了确保尽可能缩短开发时间,瑞苏盈科的FPGA专家在开发固件和软件的同时,开始开发基于AMD Zynq™ UltraScale+™的Enclustra Mercury+ XU8 SOM的基板。作为集成在FPGA中的四处理器系统的操作系统,Linux负责读写固态硬盘上的数据。Ext4用作日志数据的文件系统。由于Mercury+ XU8免费提供了Linux板卡支持包 (BSP),因此很快就决定使用这项技术。

水星Mercury+ XU8亮点

基于AMD Zynq Ultrascale+™ MPSoC XCZU4CG/5EV/7EV

PS端(DDR4 ECC SDRAM)和PL端(DDR4 SDRAM)2个独立的内存通道

最高28.8 GByte/sec内存带宽

提供PCIe® Gen3x16,PCIe Gen2x4,2xUSB 3.0,2xGigabit Ethernet

多个型号可供选择,提供工业级型号

采用3个168-pin Hirose FX10连接器,引出236个用户I/O

提供Linux BSP和工具链

功能强大、身材小巧的FPGA核心板

水星Mercury+ XU8

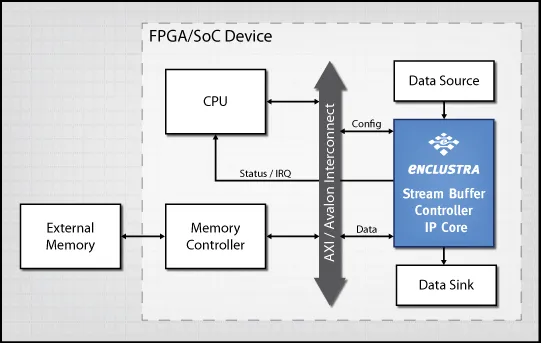

另外两项关键技术和程序也有助于最大限度地减少开发时间和精力。Enclustra总是尽可能使用IP核来开发固件,因为最终不一定要重新开发,而是要尽可能高效地解决问题。测量数据的临时存储,即在写入固态硬盘之前,是通过流缓冲控制器IP核的虚拟FIFO来实现的。该IP核可同时管理多达16个独立数据流,并支持高达4 GByte的内存大小,足以满足几乎所有要求。

流缓冲控制器IP核

基于ASP.NET Core的C#软件可在创纪录的时间内将数据记录器集成到现有的网络基础设施中。通过使用Web API,数据记录器可由上游系统通过网络进行控制。基于ASP.NET MVC和Razor Pages的本地精简网络图形用户界面对启动过程非常有帮助。

在很短的时间内,一个带有两个热插拔外壳的SATA SSD硬盘的系统就实现了。该系统能以每秒800 MBytes的速度持续记录和访问测量数据。FPGA技术的灵活性还使系统在设计时考虑到,M.2外壳中的SATA磁盘日后可以更换为速度更快的NVMe磁盘。

文章来源:Enclustra 瑞苏盈科