7. 射频数据转换器:模拟到数字

7.1 模数转换

7.2 射频频率ADC

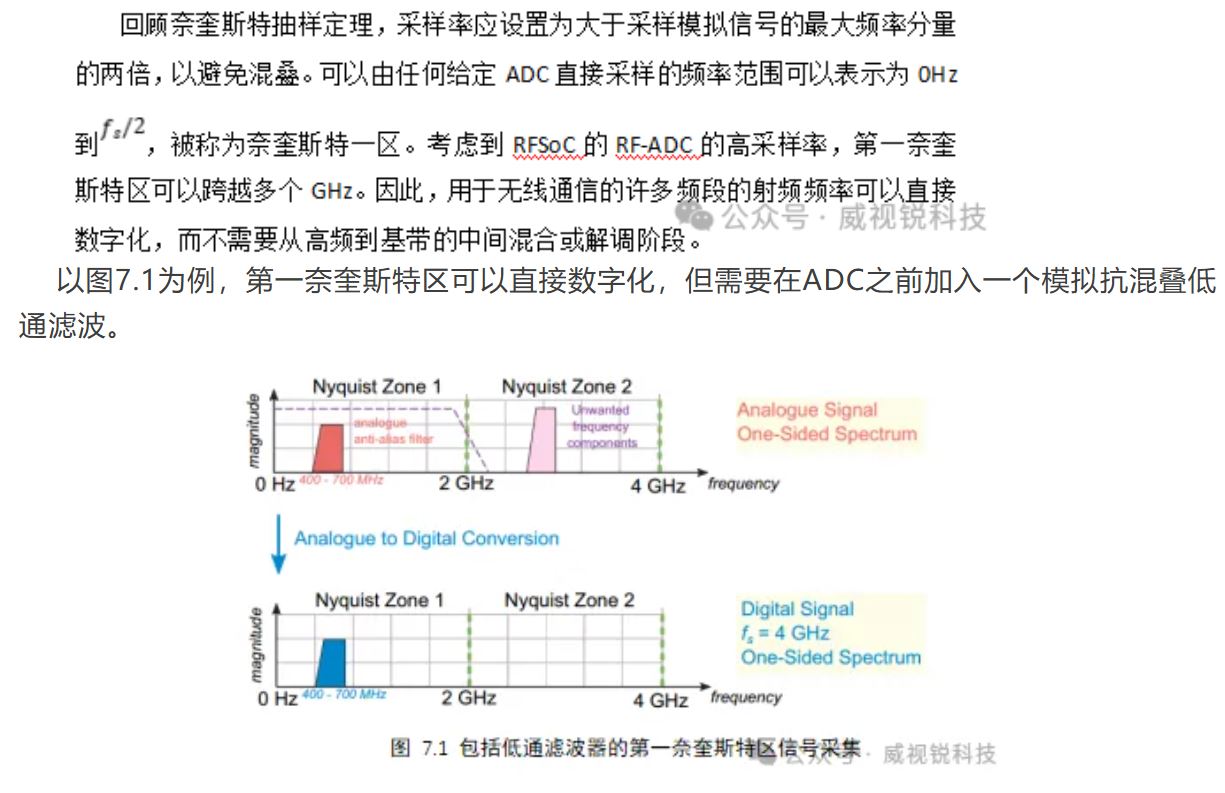

7.2.1 奈奎斯特一区

7.2.2 奈奎斯特二区及以上

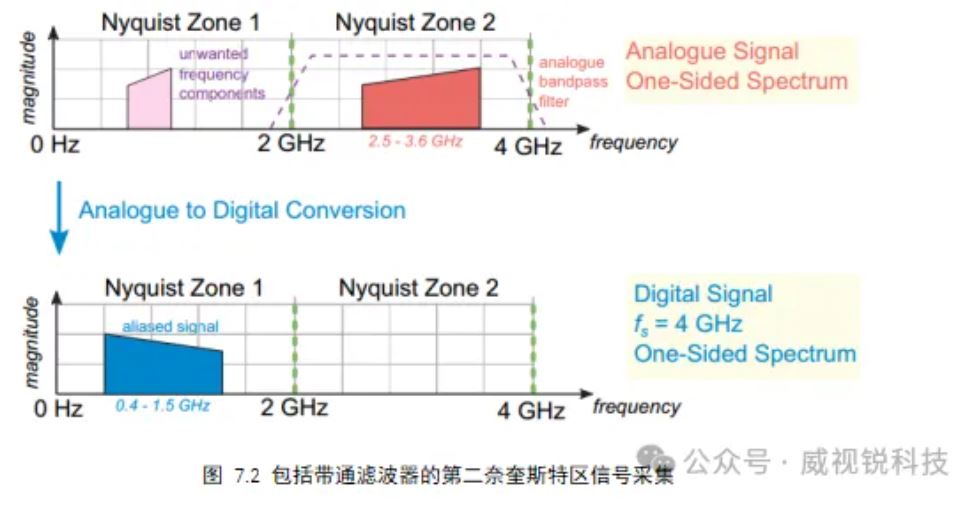

在某些情况下,可以利用混叠将信号折叠到奈奎斯特一区。折叠后可以用RF-ADC直接对第二奈奎斯特区的信号进行采样,而无需中频解调级。带通滤波并将奈奎斯特二区中的信号混叠到奈奎斯特一区的过程如图7.2。

7.2.3 模拟带通滤波器

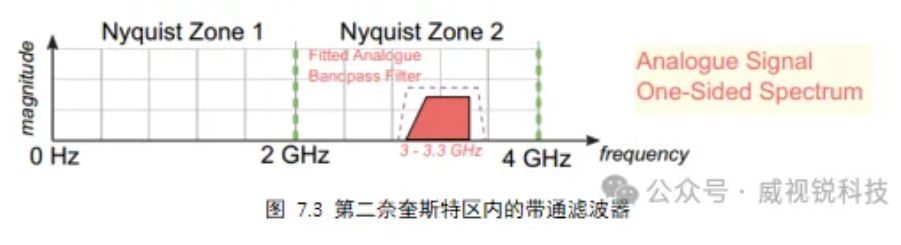

当系统被设计用于特定的标准或应用时,射频带通滤波器可用于在信号到达ADC之前隔离该信号,从而提供良好的带外抑制并提高设备的信噪比。图7.3给出了这样一个射频滤波器的示例。

RF-ADC的优势在于可以直接将许多现代通信信号数字化。且RF-ADC的高采样率也可应用于频谱分析。

7.3.1 RFSoC设备

RFSoC具有强化RFDC块,允许设备作为RF发射器和接收器。并且大多数设备还包括用于实现纠错方案的SD-FEC块。这些资源与相当于MPSoC器件的PL和PS一起,使RFSoC器件非常灵活,因此非常适合作为SDR实现平台。几代RFSoC设备的命名分别为:Gen 1——ZU2xDR,Gen 2——ZU39DR,Gen 3——ZU4xDR,RFSoC DFE——ZC6xDR。

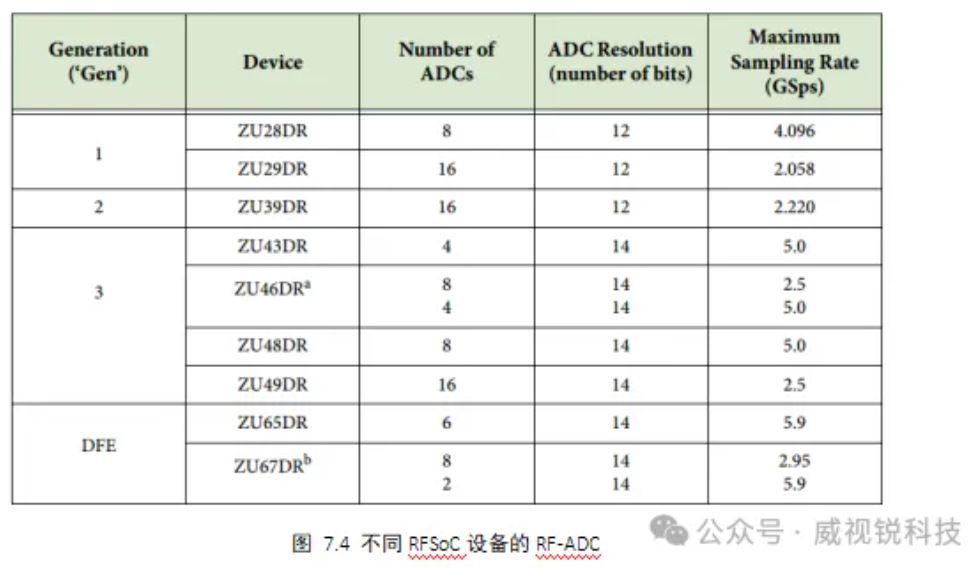

RFSoC的采样率决定了可以接收的信号频率范围,分辨率决定了由量化噪声而产生的本底噪声。图7.4展示了不同RFSoC设备的RF-ADC参数。

7.3.2 RF-ADC片架构

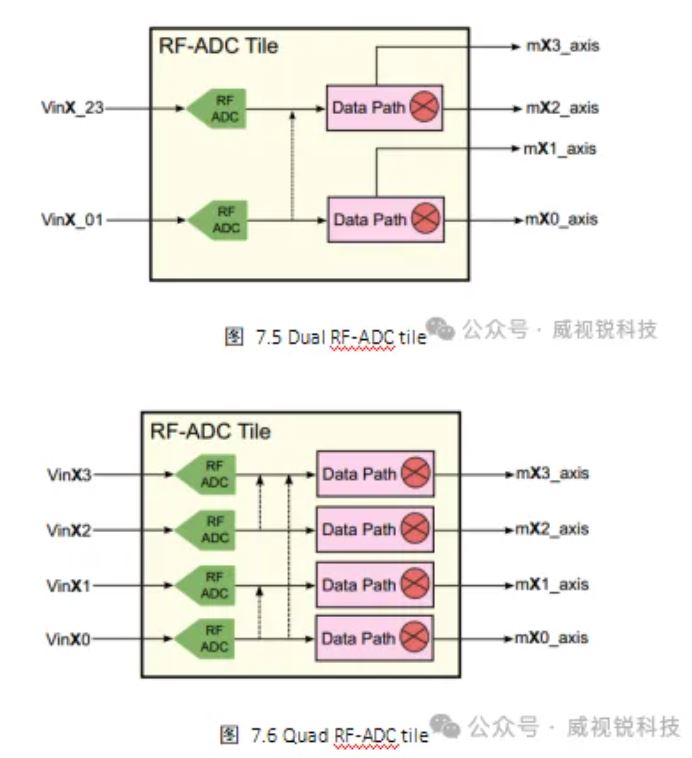

RFSoC的RFDC包括RF-ADC和RF-DAC,以片和块的层次结构构成。每个RF-ADC和RF-DAC都包含在一个块中。根据设备的不同,一个、两个或四个块组成一个片,分别称之为Single tile,Dual tile和Quad tile。Dual tile和Quad tile结构分别如图7.5和7.6所示。

第三代设备根据设备的不同,要么只使用Quad tile或Dual tile,要么将两者结合起来。ZU48DR和ZU49DR器件与前面讨论的两个器件类似,分别由4个Dual tile和4个Quad tile组成,总共有8个和16个RF-ADC。ZU46DR器件采用混合配置,共包含12个RF-ADC,由2个Dual tile和2个Quad tile组成。ZU43DR器件包含四个Single tile,每个片有一个RF-ADC,因此总共有4个RF-ADC。DFE设备在结构上与第三代设备相似,有两种DFE器件可用:ZU65DR和ZU67DR。前者包含三个Dual tile,总共6个RF-ADC; ZU67DR也包含三个片:两个Quad tile和一个Dual tile,总共10个RF-ADC。

7.3.3 交叉因子

RFSoC器件的每个RF-ADC都由多个子ADC组成,这些子ADC交织在一起以提高最大采样率。通过使用ADC交织,输入信号由每个子ADC同时采样,使用m个子ADC,有效采样率比单个ADC提高了m倍,这就是所谓的交织因子。

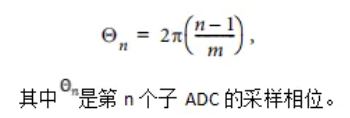

为了成功交错,ADC之间的时钟相位关系至关重要:

在Dual tile中,每个RF-ADC由8个交织的子ADC组成,而Quad tile中,每个RF-ADC由4个交错的子ADC组成。因此同样的RFSoC组成中,Dual tile采样率为Quad tile采样率的二倍。

7.3.4 RF-ADC片组成

无论片的配置如何,其中的每个RF-ADC块都包含一个高性能输入缓冲区和一个包括RF-ADC本身的组件管道;一个正交调制校正(QMC)单元,它可以纠正正交系统外部信号路径中的任何不平衡,用于解调的复杂混频器;以及用于降低采样率的抽取滤波器。该RFADC处理管道针对射频信号频率的直接转换进行了优化。

1. 第一代RF-ADC片

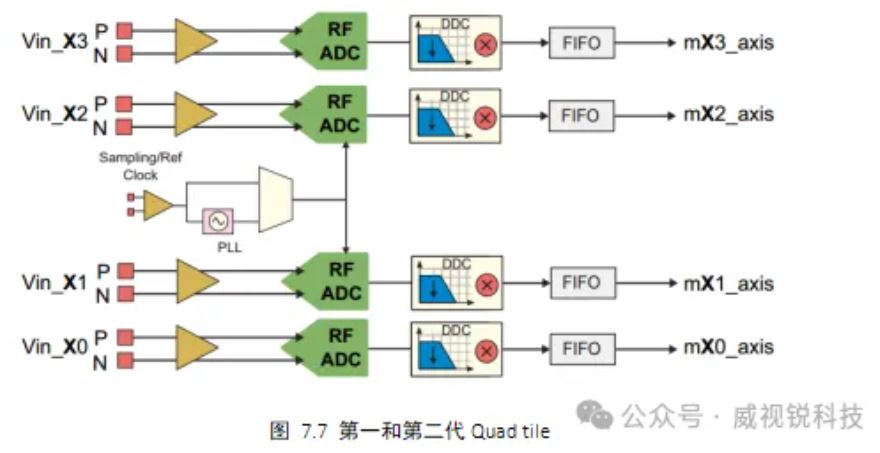

Quad tile和Dual tile的结构相似,时钟电路包括一个锁相环(PLL),由外部参考时钟驱动。每片内的RF-ADC都有一个相关联的数字下变频(DDC),其中包含一个数字复杂混频器和一个可编程十进制抽取器。每个RF-ADC都有自己专用的混频器和抽取器。

如图7.7所示,第一代Quad tile包含4个RF-ADC,排列成两对。每个RF-ADC可以单独配置,也可以作为一对的一部分,分别用于实信号和复信号。

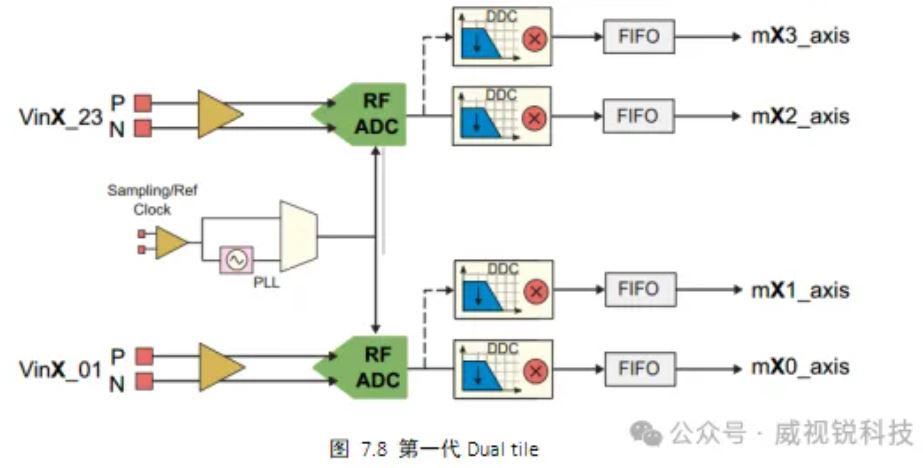

图7.8展示了第一二代Dual tile的配置,它与Quad tile非常相似,但只存在两个RF-ADC,既可以单独操作,也可以成对操作来接收复信号。

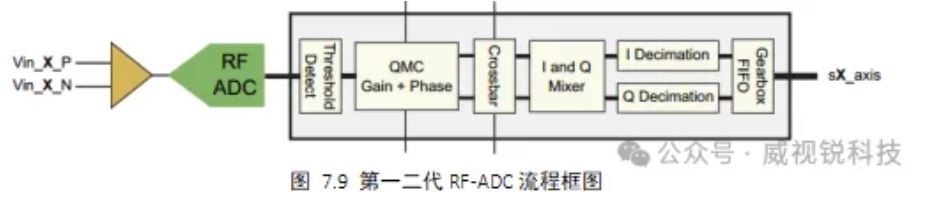

每个RF-ADC块的操作以及与之相关的DDC简化为如图7.9的流程,步骤如下。输入缓冲器控制信号采集速率后,RF-ADC对模拟输入信号进行采样,将其转换为数字信号。再用阈值检测器来检测和记录输入的振幅水平。接下来,若接收信号为复信号,用QMC块对I路和Q路之间的不平衡进行补偿。然后,复混频器将输入信号调制到基带以简化处理。在通过FIFO与PL接口之前,I路和Q路抽取器能够对信号进行抽取。

2. 第三代RF-ADC片

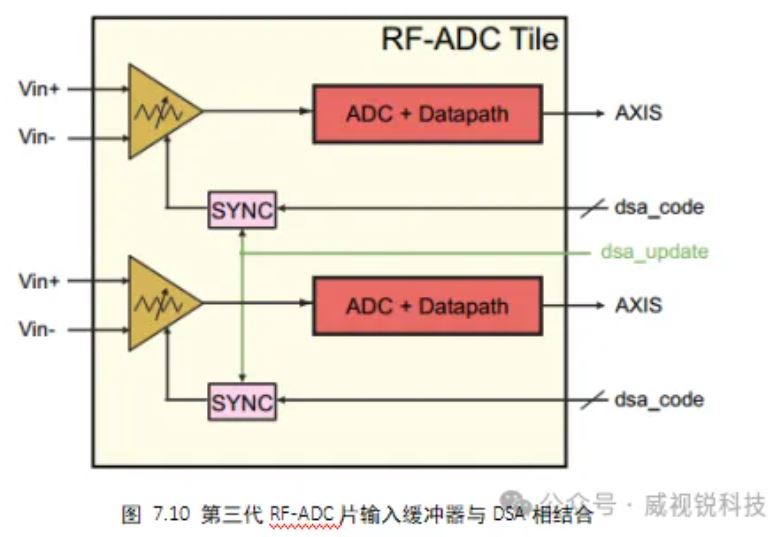

第三代在RF-ADC之前具有数字阶跃衰减器(DSA)并提供了更高级的抽取过滤器链,能够以1x, 2x, 4x, 6x, 8x, 10x, 12x, 20x, 24x和40x的倍数进行抽取。

DSA用于模拟信号幅度或功率随时间变化的情况,允许将可变信号的幅度调整到RF-ADC的最佳值。传统上,DSA将是一个外部组件,然而第3代设备将此功能与内部输入缓冲器相结合,如图7.10所示。

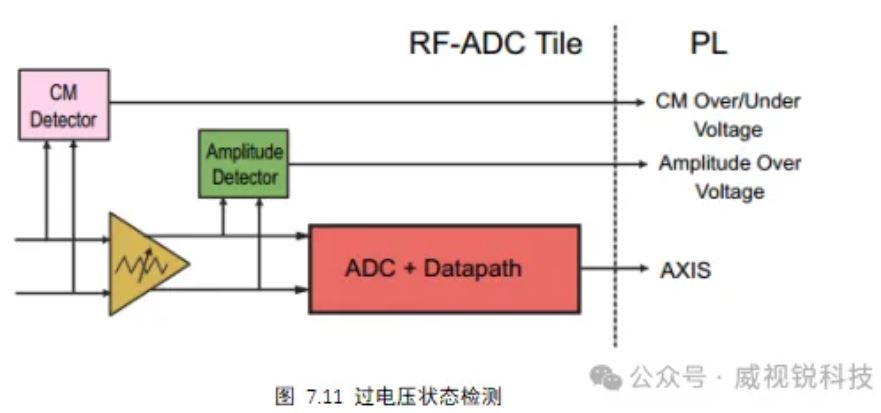

DSA还用于自动防止过电压状态,即输入信号太大,RF-ADC无法处理的情况。这有两种形式:过幅和共模范围外。对于过幅,当输入缓冲器中的信号幅度对于RF-ADC来说太大时,DSA由缓冲器中的一个标志触发并自动设置。当输入端的值超过或低于可靠的共模范围时,将触发外部共模范围。这可以通过禁用输入缓冲区来解决。这些过电压保护相对于DSA的位置如图7.11所示。

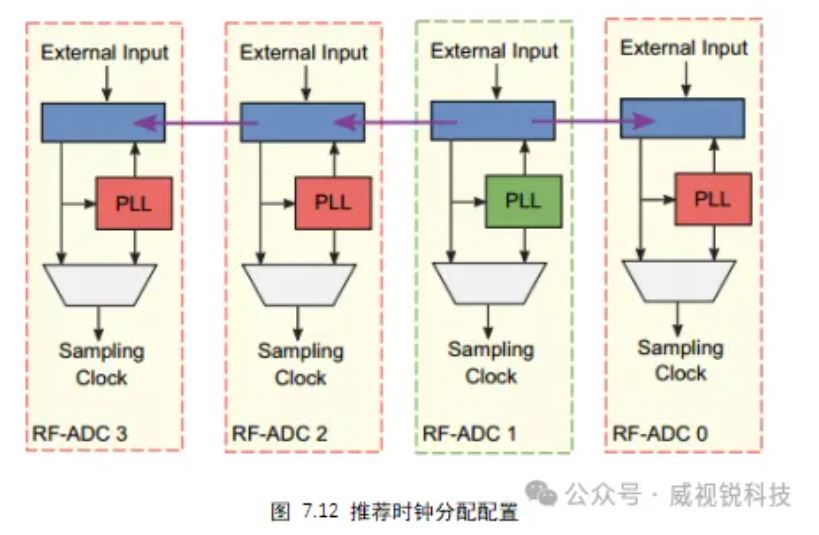

第三代RF-ADC也允许时钟分布在RF-ADC和RF-DAC中,如图7.12所示,允许一个RF-ADC片将其时钟分布到链中其他相邻的片上。

文章来源:威视锐科技