-ALINX NVME SPCle IP -

在嵌入式设备、边缘计算、工业控制等领域快速崛起的同时,开发人员越来越多地面对一个问题:

硬件资源有限,但对高速存储的需求却越来越高。这些平台可能没有 PCIe 硬核,或者无法承担高昂的硬件成本。

NVMe SPCle IP 正是为这样的场景量身定制。通过结合 PCIe 软核 IP 与 NVMe 主机控制器,让开发人员在无硬核的情况下,也能轻松接入 NVMe SSD,突破了传统存储方案的硬件限制。

简单来说,NVMe SPCle IP 的存在,让高性能存储不再是高成本设备的专属。

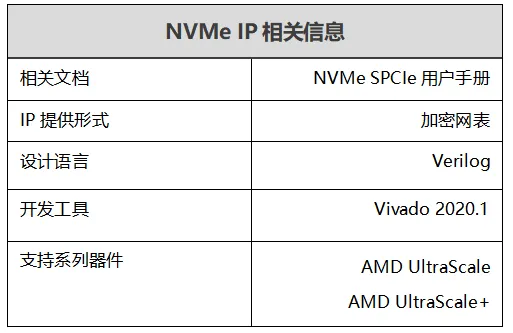

ALINX NVMe SPCle IP 详情

IP 资源消耗表

产品特性

产品特性

功能实现:带有 PCIe 软核 IP 的 NVMe 主机控制器,实现不依靠 CPU 访问外置内存 NVMe SSD,自动初始化 NVMe 和 PCIe 链路硬件模块,自动提交和完成命令 兼容性:命令支持(Identify, Write, Read, Flush),支持 PCIe Gen 1.0-4.0,兼容 NVME 1.4 协议 性能参数: (1) 支持最大每个队列 65535 个 I/O 命令 (2) 基于 PCIe3.0 X4 读写速率均可达到 3000 MB/s (3) MPSMIN (最小内存页传输大小):4 Kbyte (4) MDTS (最大数据传输大小):至少 128 Kbyte 或者没有限制 (5) LBA 单元:512 字节或者 4096 字节 参考设计:XCZU19EG + FMC子板(FH1402)+SAMSUNG 980 M.2 SSD 技术支持:提供完备的技术支持与定制化设计服务

ALINX NVMe SPCle IP 应用交互

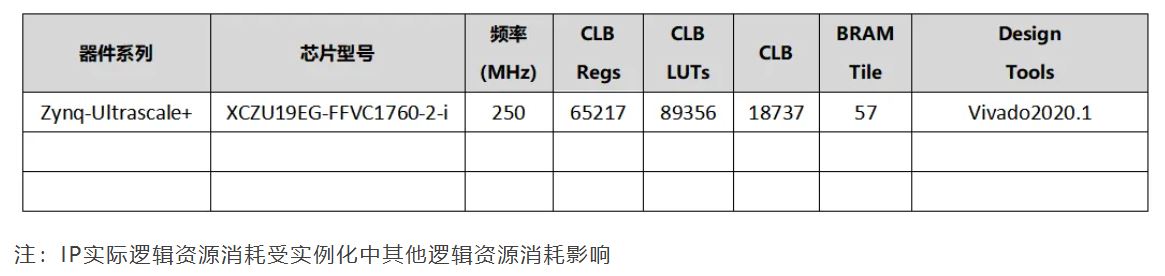

如图所示,ALINX NVMe SPCIe IP 包含的 PCIe 软核 IP,完成了 PCIe 协议的数据链路层和物理层的部分功能。其物理接口通过 PIPE 接口与 AMD PCIe PHY 连接,AMD PCIe PHY 包括收发器和均衡器逻辑,用于实现高速数据传输。

NVMe SPCIe IP 由 NVMe IP 和 PCIe 软核 IP 组成,因此 NVMe SPCIe IP 在功能上与 NVMe AXI IP 相似性。

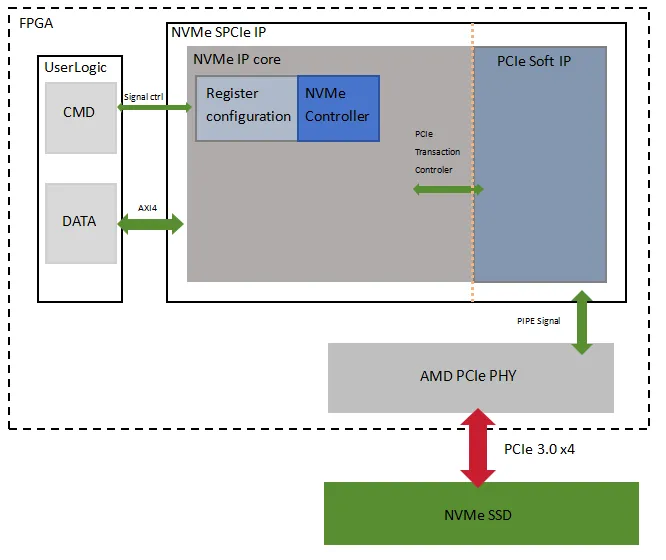

下表显示了 NVMe SPCIe IP 和 NVMe AXI IP 的比较信息。

如图所示,NVMe SPCIe IP 的主要优点是不需要使用 PCIe 硬核 IP。因此,SSD 的最大数量不受 PCIe 硬核 IP 数量的限制,而是受收发器模块数量和资源的限制。但是 NVMe SPCIe IP 的资源消耗较 NVMe AXI IP 高,且仅支持 4 Lane PCIe Gen3 SSD。

ALINX NVMe IP 选型

ALINX 推荐在需要大容量存储和高速存储的应用场景中,优先使用不包含 PCIe 硬核 IP 的低成本 FPGA。

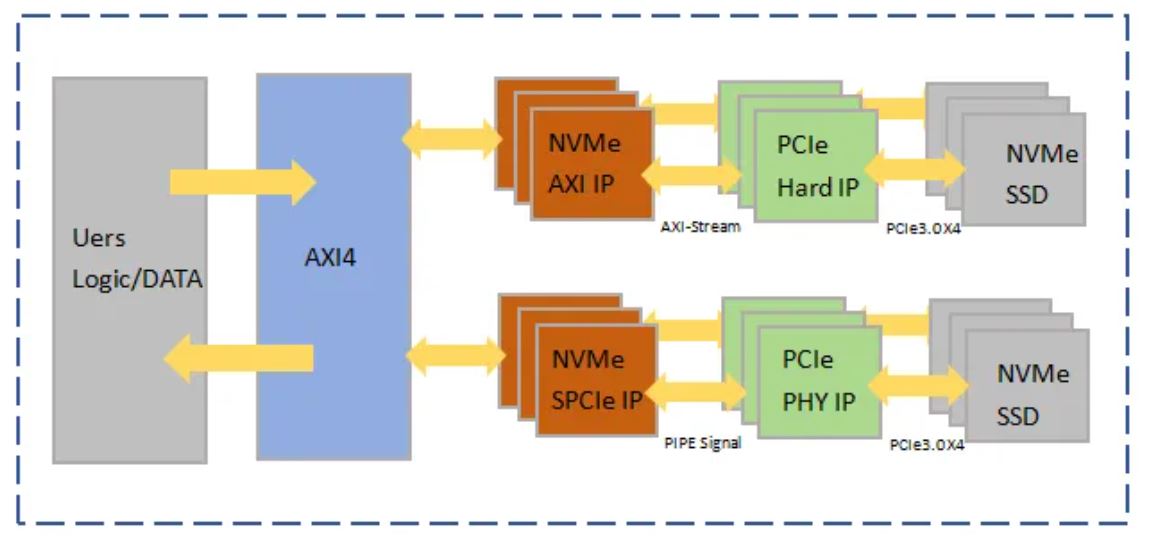

当用户所选设备没有足够的 PCIe 硬核 IP 来连接所有 NVMe SSD 时,可以同时使用 NVMe AXI IP 和 NVMe SPCIe IP 进行系统设计,如下图所示。

当所选 FPGA 器件已经集成了 PCIE 硬核 IP,并且数量足够时,建议使用 NVMe AXI IP 进行设计,以减少 FPGA 资源的占用。

有关 NVMe IP 的更多信息,您可以随时联系 ALINX 进行咨询 (021-67676997) 。ALINX 还可为您提供 FPGA 器件的参考设计评估服务,帮助您选择最合适的产品和方案。

文章来源:ALINX