本文翻译转载于:Cadence Blog

作者:Satish Kumar Padhi

外围器件互连快速通道 (PCIe) 是一种广泛用于连接处理器、存储器和外围设备的高速接口标准。随着 PCIe 在敏感数据处理和关键高速数据传输中的日益普及,确保验证过程中的数据完整性和加密成为首要目标。在验证领域,随机化被公认为驱动稳健 PCIe 验证的关键技术。随机化带来了不可预测性,可模拟现实场景并发现设计中隐藏的问题。本文将探讨随机化在 PCIe IDE 验证中的重要性,重点介绍它如何在确保数据完整性和加密可靠性方面发挥关键作用,同时也揭示了该过程的独特挑战。

数据完整性

确保数据在传输过程中不发生任何变化。即便数据包仅出现轻微损坏,也可能对系统可靠性产生影响。因此,完整性是 PCIe 验证的一个核心要素。

数据加密

在传输过程中保护敏感数据,避免未经授权的访问。PCIe 中的加密遵循一定的标准,能够在高速运行时保障信息安全。

对于所有端点设备来说,在 PCIe 6.0 的 64GT/s 和 PCIe 7.0 的 128GT/s 高速数据传输速率下,确保数据完整性和数据加密至关重要。然而,验证这些机制需要采用全面的测试和验证方法,随机化在其中发挥着关键作用。

PCIe 验证中的随机化

随机化是指生成具有不可预测输入和条件的测试场景,呈现边界情况。在 PCIe 验证中,随机化有助于确保测试所有可能的行为,包括一些罕见或意外情况,这些情况可能导致数据损坏或加密失败,继而在后续阶段引发严重问题。因此,我们正计划将随机化引入 PCIe IDE 验证,以便更有效地验证行为。

数据完整性验证的随机化

以下是一些模拟真实流量情况的随机验证方法,能够揭示常规验证方法中可能不会出现的细微完整性问题。

随机数据包注入

该技术将数据包随机化,并注入设备之间的通信流。在此过程中,我们向 PCIe 链路注入随机、格式错误或无序的数据包,并混合有效和无效的 IDE 加密数据包,以验证系统是否能够检测和拒绝未经授权或无效的数据包,检查数据包之间的加密/解密是否正确。在验证过程中,我们检查系统在遇到无效数据包时是否能够准确记录错误或警报。这样可以确保覆盖不同的数据路径,进而实现可靠的协议检查。

此方法有助于从以下方面评估 IDE 功能在 PCIe 中的弹性:

(i) 数据损坏:检测系统是否能够维护数据完整性。

(ii) 加密失败:测试随机注入数据时的加密可靠性。

(iii) 数据包排序错误:确保重新排序不会影响数据传输。

随机错误和故障注入

模拟随机位翻转、PCRC 错误或协议违规,帮助验证 PCIe 错误检测和纠正机制的可靠性。

这些方法有助于评估 PCIe IDE 实现的效果:

(i) 检测并响应意外错误。

(ii) 在压力下保持安全通信。

(iii) 遵循 PCIe 错误恢复和报告机制(AER – 高级错误报告)。

(iv) 确保加密和解密状态在端点之间保持同步。

流量模式随机化

将数据包的顺序、大小和传输时间随机化,有助于测试设备如何在繁重、不可预测的流量负载下保持数据完整性。

数据加密验证的随机化

加密增加了验证的复杂性,因为传统检查无法读取加密的数据流。在测试不同场景下的加密时,随机化起到了至关重要的作用。数据加密验证中的随机化可确保识别和缓解密钥重用或可预测模式等漏洞。

随机加密密钥和有效载荷

随机变化的密钥和有效载荷有助于验证加密的正确性,而无需依赖硬编码假设,确保加密逻辑在所有可能的输入中都能正确运行。

随机初始化向量 (IV)

许多加密协议要求每个事务都有唯一的 IV。随机 IV 可有效防止加密过程中的模式重复。要了解 IDE 密钥管理流程,可以参考下图,其中展示了使用 IDE_KM 协议的密钥编程流程详细示例。

图 1:IDE_KM 示例

如图 1 所示,IDE_KM 协议的功能包括启动 IDE_KM 会话、设备能力发现、来自主机的密钥请求、对 PCIe 设备的密钥编程以及密钥确认。首先,主机通过检测是否存在 PCIe 设备来发起 IDE_KM 会话;如果设备支持 IDE 协议,系统将继续执行密钥编程流程。然后通过查询找到设备的加密功能,确定设备支持动态密钥更新还是静态密钥。随后,主机向密钥管理实体发送请求以获得适用于设备的密钥。在获得密钥后,主机会将其编程至 PCIe 端点上的 IDE 控制器中。此时,主机和设备使用相同的密钥对流量进行加密和验证。设备确认收到并成功安装加密密钥后,将确认消息发送回主机。主机和 PCIe 端点的密匙配置完成后,将建立安全的通信通道。从这一刻起,通过 PCIe 链路传输的所有数据都被加密,以确保数据的机密性和完整性。

IDE_KM 可用于安全分发密钥,保持 PCIe 事务的机密性和完整性。此关键编程流程可确保在主机和 PCIe 设备之间建立安全的通信通道。因此,随机密钥方法可避免加密过程中的模式重复。

随机化 PHE

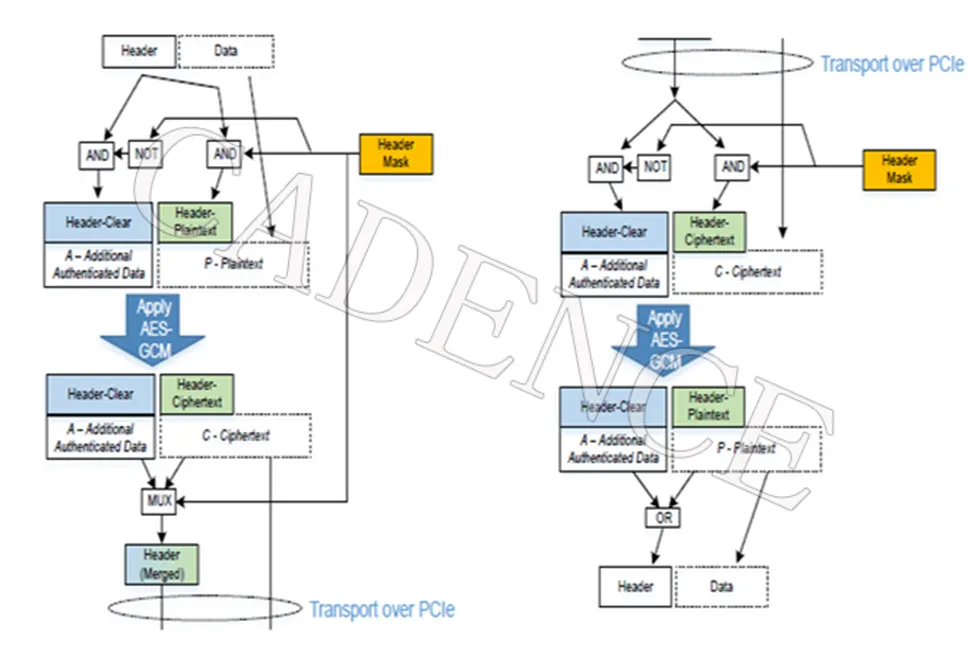

部分包头加密 (PHE) 是 PCIe 6.0 完整性和数据加密 (IDE) 中的一个附加机制。PHE 验证使用各种流量;在用于验证 PHE 功能的 API 中引入随机化,可以显著提升数据加密的可靠性。

图 2. 部分包头加密

IDE 地址关联寄存器值的随机化

IDE 地址关联寄存器 1/2/3 应根据 IDE 伙伴端口的内存地址范围进行配置。这些寄存器的字段包括多个值,如内存基数下限、内存限制下限、内存基数上限和内存限制上限。IDE 的实现可以包含多个寄存器块,并支持多种配置选项,如 32 位或 64 位地址、不同的寄存器大小、0-255 个可选流、0-15 个地址块等。随机化验证可以帮助验证所有边界情况。请参考图 2。

图 2. 部分包头加密

加密期间的随机故障

随机故障注入(例如,丢包或时间不匹配)可确保系统能够处理中断,防止数据泄露。

IDE 随机化带来的挑战及其解决方案

随机化引入了大量场景,而模拟每一种可能性需要庞大的计算量。约束随机化将随机输入限制在有效范围内,但仍可覆盖边界情况。此外,使用覆盖率驱动的验证策略,能够避免关键场景的测试存在过多冗余。

使用随机输入来验证加密数据会增加复杂性。加密会掩盖数据,很难在不损害安全性的情况下验证输出。我们可以在 IDE 回调中实现多种 IDE 检查机制,直接分析加密流量,而无需进行解密。

随机化可能会引发意外故障,而且通常难以重现。通过使用基于种子的随机化,特定的种子生成可重复的随机序列,有助于更准确地重现和分析行为。

结论

随机化是 PCIe 验证中的一种强大技术,可确保有效验证数据的完整性和机密性,有助于我们发现非随机测试可能遗漏的细微错误和边界情况。在 Cadence PCIe VIP 中,我们提供成熟的 IDE 验证机制,并通过严格的随机验证确保数据完整性。为了实现安全高效的数据通信,我们采用强大且可靠的加密机制。然而,随机化也带来了诸多挑战。为了克服这些挑战,我们结合使用约束随机化、基于种子的测试和覆盖率驱动的验证方法。如今,PCIe 正在以更快的速度发展,业内也日益注重安全性,在此背景下,Cadence PCIe VIP 能够满足行业需求,通过验证高性能系统,确保在实际运行时有效保障数据安全。