第二代 AMD Versal Premium 系列自适应 SoC 是一款多功能且可配置的平台,提供全面的 CXL® 3.1 子系统。该系列自适应 SoC 旨在满足从简单到复杂的各种 CXL 应用需求。无论您是高级自适应 SoC 开发人员,还是 CXL 初学者,第二代 Versal Premium 系列都能提供灵活的 CXL 3.1 子系统,非常适合内存扩展、内存池化和内存加速应用。

CXL

Compute Express Link® ( CXL )是由行业领导者联合开发的一项新型高速互联技术。它旨在弥合 CPU、GPU 和其他高性能加速器之间的差距,使它们能够在统一的内存空间中更高效地协同工作。CXL 通过提供高带宽、低时延、以内存为中心和缓存一致性的接口来实现这一目标,该接口使设备能够在互联中共享数据和内存。

CXL 内存扩展

随着人工智能和机器学习等先进技术的蓬勃发展,数据生成和处理在全球范围内持续激增。因而计算过程中对更大内存容量的需求变得更加迫切。FPGA 系统设计人员面临的内存挑战与典型的基于处理器的设计类似。因此,客户可以通过第二代 Versal Premium 系列的 CXL 3.1 子系统为其 FPGA 增加更多内存,这是 Versal 产品组合中首款提供 CXL 内存扩展功能的产品。

CXL 近内存计算

当前的计算领域已开启一个需要大量内存密集型运算的新时代。随着此类计算任务的需求不断增长,业界专业人士越来越关注并致力于将某些内存密集型操作移至更靠近内存的位置,以提升系统性能并降低功耗。第二代 Versal Premium 系列自适应 SoC 已成为近内存处理应用的理想平台,设计人员可以利用 CXL 接口在内存空间中更高效地迁移预处理和后处理的数据。

CXL 3.1 子系统功能概述

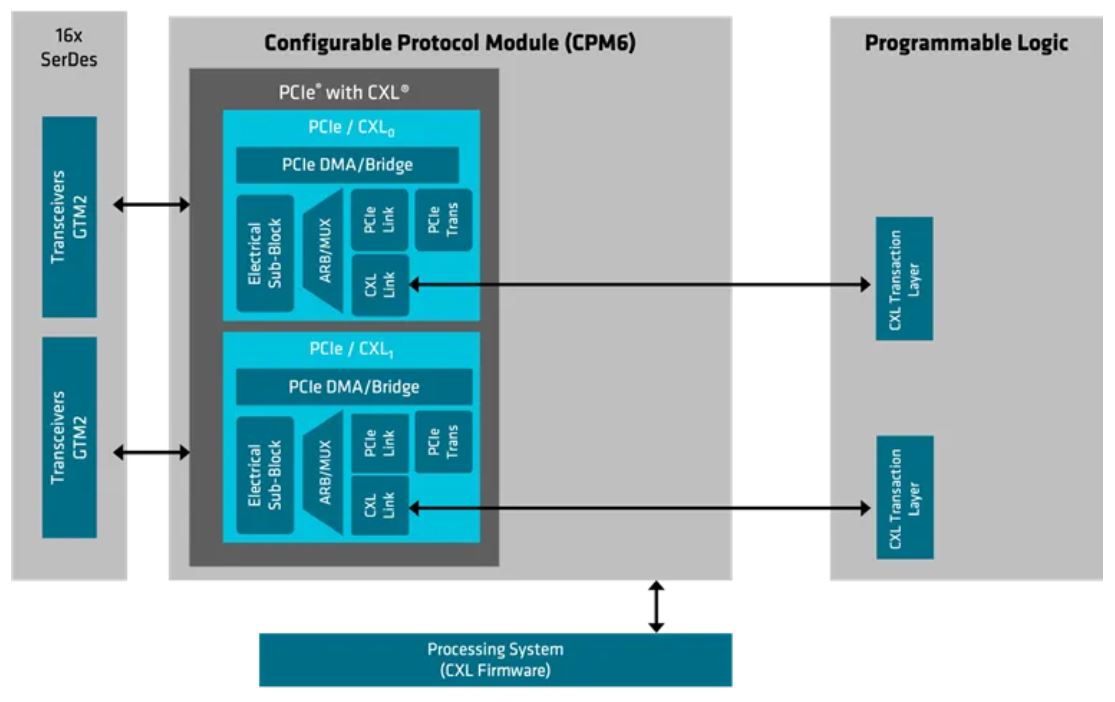

第二代 Versal Premium 系列 CXL 子系统由四个主要组件构成:GTM2 收发器、可配置协议模块 6( CPM6 )控制器、CXL 事务层 IP 和 CXL 固件。系统架构师可以选择使用整个 CXL 子系统,或根据自身配置和定制需求使用部分子系统。CXL 子系统同时支持 CXL 端点模式和 CXL 主机模式。

第二代 Versal Premium 系列 CXL 子系统

GTM2 收发器

PCIe® 物理层

支持第一代到第六代( NRZ 和 PAM4 )

CPM6 控制器

支持 CXL 1.1/2.0/3.1 替代协议协商

支持 68B 和 256B FLIT

CPM6 CXL 仲裁器和多路复用器( ArbMux )

CPM6 数据链路层( DLL )

CXL 事务层 IP

通过 Vivado LogiCORE IP 目录提供

可配置为 Type-3、Type-2 和 Type-1

CXL 固件

提供 C 源代码

初始化和配置。运行时管理

更大容量,更大宽带1

主要优势

设计符合 CXL 标准

提升系统性能

灵活且可配置

主要功能

CXL 3.1 硬件子系统

CXL 内存扩展

CXL 近内存计算

主要特性

支持 CXL 1.1、2.0 和 3.1

最大链路速率:64 GT/s( PAM4 )

2 个 CXL 控制器

16 条 PCIe/CXL 通道( 2 x 8 )

支持 CXL.io

支持 CXL.mem

支持 CXL.cache

端点模式:Type-3/2/1

主机模式:Type-3

客户示例设计( CED )

下一步

如需了解有关第二代 AMD Versal Premium 系列器件的更多信息,敬请访问产品专区。

1. 基于 AMD 进行的内部分析,比较了第二代 AMD Versal Premium 系列器件(配备 CXL 3.1 和 LPDDR5X 存储器组件)所具有的总内存带宽与同类器件(仅配备 LPDDR5X 存储器)的总内存带宽。内存带宽会因系统配置和其他因素而异。(VER-059)

文章来源:AMD