智多晶FIFO_Generator v2.0 IP

FIFO_Generator是智多晶设计的一款通用型FIFO IP。当前发布的FIFO_Generator IP是2.0版本,相比之前的1.1版本主要新增了非等比输入输出数据位宽支持和异步FIFO跨时钟级数配置功能。

FIFO_Generator IP特性

支持同步/异步选择

支持RAM类型选择:自动、块(BLOCK)RAM、分布式RAM

读端口支持普通/预读模式:普通读模式 、预读模式(First Word Fall Through)

支持跨时钟域级数配置

支持输入输出数据位宽比例可变

数据保护,确保不会出现写超和读超的情况

支持data_count输出(可配置)

支持prog_full, prog_empty端口(可配置)

支持almost_full, almost_empty端口(可配置)

RAM类型选择

FIFO_Generator IP支持用户选择FIFO内RAM的资源类型,可选“块(Block)RAM”和“分布式RAM”。默认为“自动”,软件根据用户输入的FIFO数据位宽和深度,自动选择合适的资源来实现。

分布式RAM使用LUT资源,块(Block)RAM使用块RAM(EBR)资源。一般建议小尺寸FIFO使用分布式RAM,大尺寸的FIFO使用块(Block)RAM。合理选择使用的存储资源类型可以获得很好的性能和资源占用。

读数据模式选择

FIFO_Generator IP支持2种FIFO读模式,“普通读模式”和“预读(FWFT)模式”。

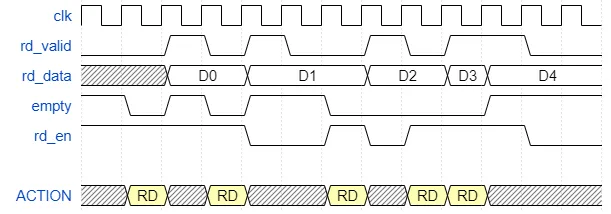

普通读模式,数据在进行有效读信号(rd_en & !empty)以后立即更新。在没进行读操作之前,端口上的数据无效,或保持上一次读出的数据。

FIFO普通读模式时序图

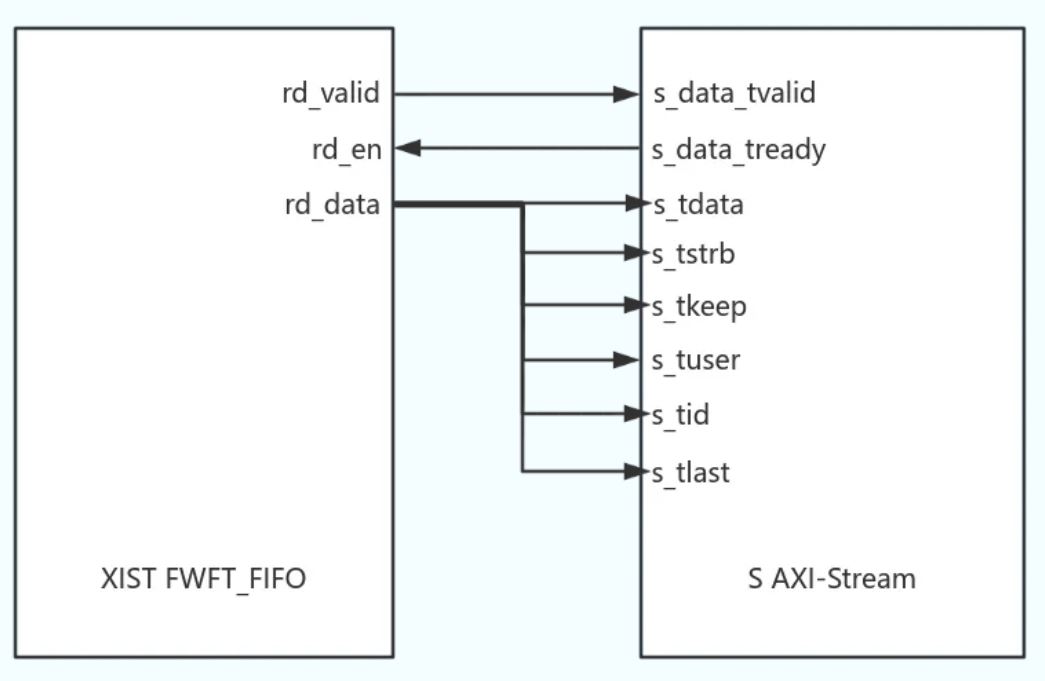

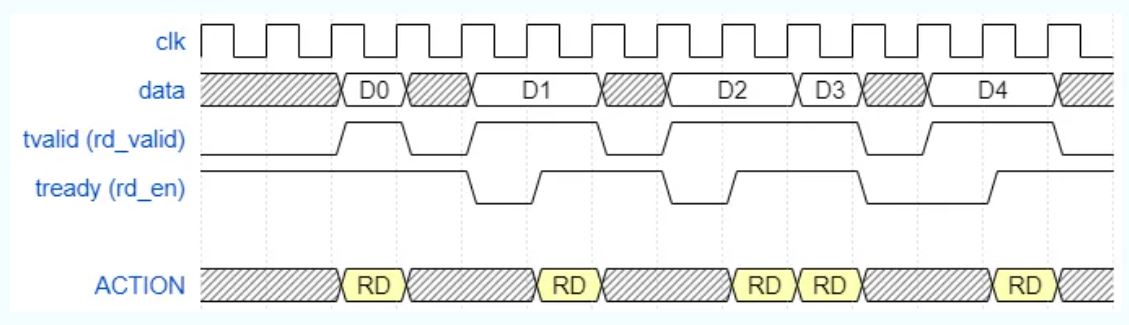

预读模式,数据在FIFO内会自动搬运到端口上并以rd_valid信号作为端口数据可用且未过期的标志。预读模式下,以rd_valid和rd_en信号同时为1的作为读取条件,因此工作在预读模式的FIFO和AXI/AHB/APB总线的握手反压操作兼容性非常好。

智多晶FWFT FIFO适配AXI-Stream接口的典型连接

AXI-Stream握手反压式操作时序图

输入输出数据位宽比例变化

2.0版本的FIFO generator IP新增对输入输出端口的数据位宽调整的支持。默认为1:1模式,可选8:1,4:1,2:1,1:2,1:4,1:8。

当用户选择非等比输入输出接口位宽时,如果启用data_count端口,会分别得到wr和rd两个端口的data_count输出。

该特性在选择块(Block)RAM和分布式RAM模式下都提供支持,对RAM类型没有要求。

FIFO_Generator IP配置与使用

打开IP

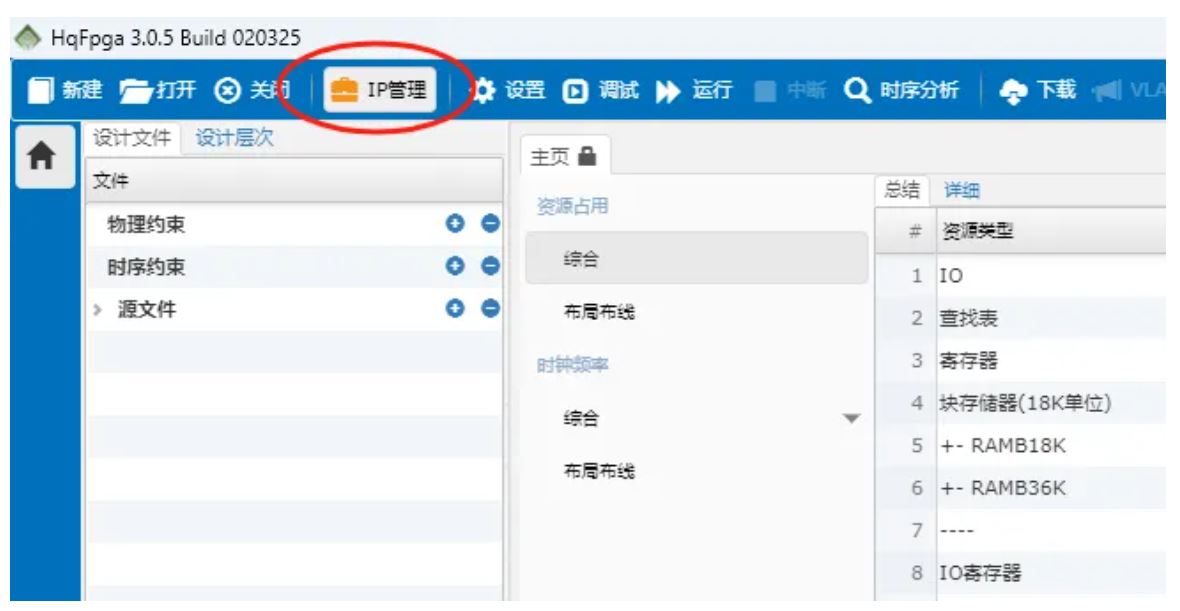

第一步,使用HqFpga v3版本软件,创建或打开一个工程。

第二步,在已打开的工程中,点击“IP管理”图标。

第三步,在IP管理器“IP Creator”--“存储单元”分类或“基本单元”分类下找到FIFO_Generator IP,双击打开FIFO_Generator IP配置界面。

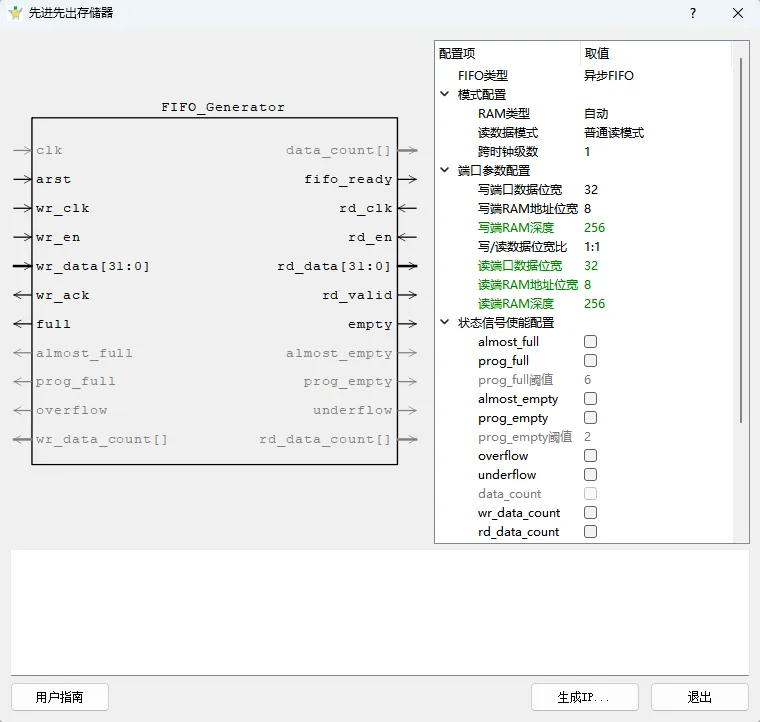

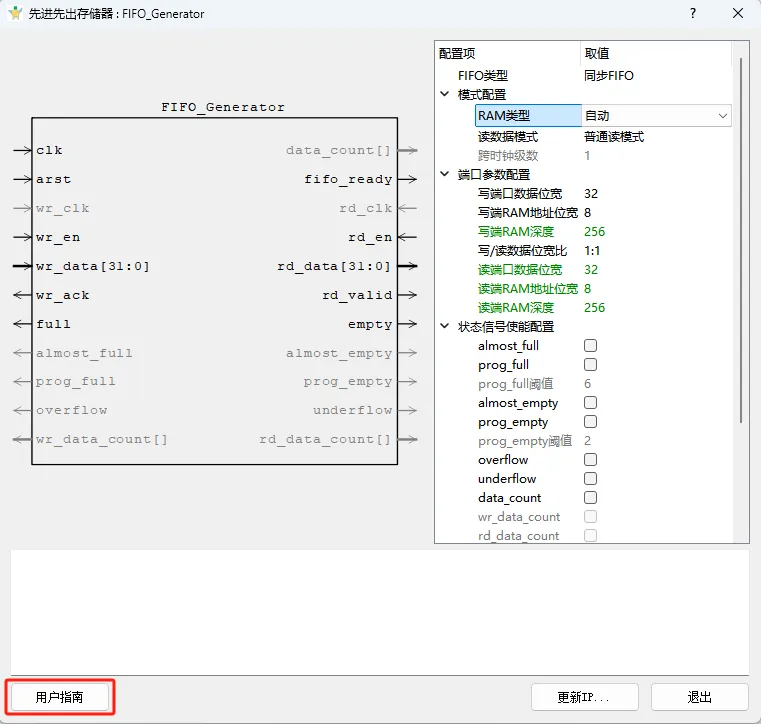

配置IP

IP配置界面的配置选项清晰明确。从上到下依次对FIFO类型,功能模式,端口规模参数进行配置,最后选择需要用到的状态信号。针对输入输出数据端口变位宽的特性,IP界面会根据当前的配置以绿字方式提供实时信息反馈,帮助用户理解这些配置产生的效果。

不同的功能配置会影响输出IP占用的FPGA逻辑资源和IP模块的性能,建议用户关闭不需要的功能从而获得最佳的资源和性能表现。

设计资源

FIFO_Generator IP用户文档已随IP发布,可通过IP界面直接获得。

在FIFO_Generator IP界面左下角,点击“用户指南”可以直接打开FIFO_Generator IP的用户指南(UserGuide)pdf文件。

其它相关设计资源后续会陆续通过官网发布,欢迎关注。有任何疑问请通过智多晶公众号或FAE与我们联系。

文章来源:智多晶