AI Engine Tile 架构

AI Engine数据移动架构

本节描述了AI Engine阵列内以及AI Engine Tile和可编程逻辑(PL)之间的数据通信示例。

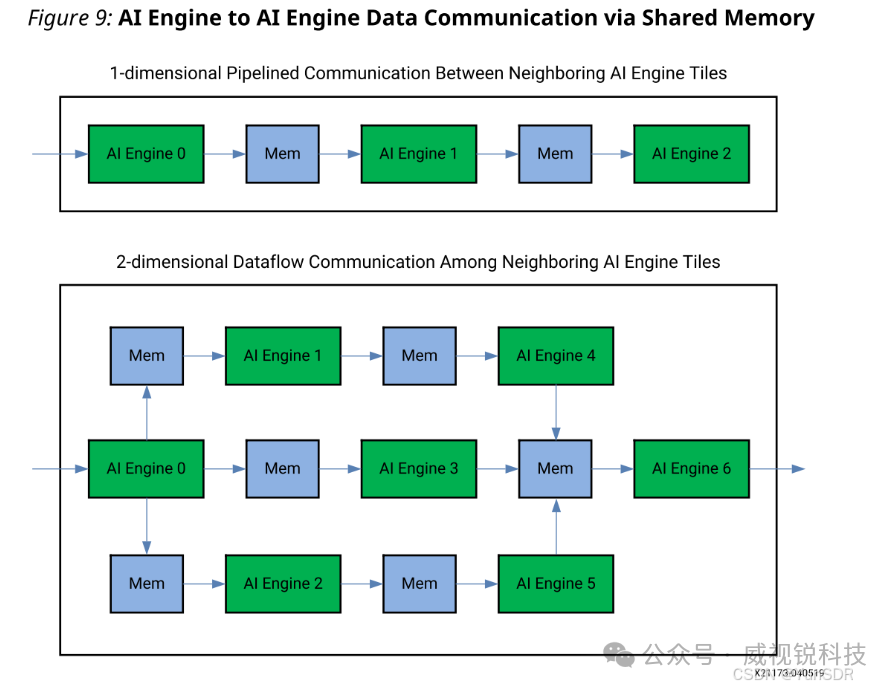

(1)通过共享内存进行AI Engine到AI Engine的数据通信

在多个内核适合单个AI Engine的情况下,可以使用共享内存中的公共缓冲区建立两个连续内核之间的通信。对于内核位于单独但相邻的AI Engine中的情况,通信是通过共享内存模块进行的。数据移动的处理可以通过一个简单的pipe或多个并行的pipe阶段(见下图)。两个AI Engine之间的通信可以在单独的存储体上使用ping和pong缓冲区(图中未显示)来避免访问冲突。同步是通过锁完成的。这种类型的通信不需要DMA和AXI4流互连。下图显示了AI Engine Tile之间的数据通信。它们是AI Engine Tile和共享内存模块的逻辑表示。

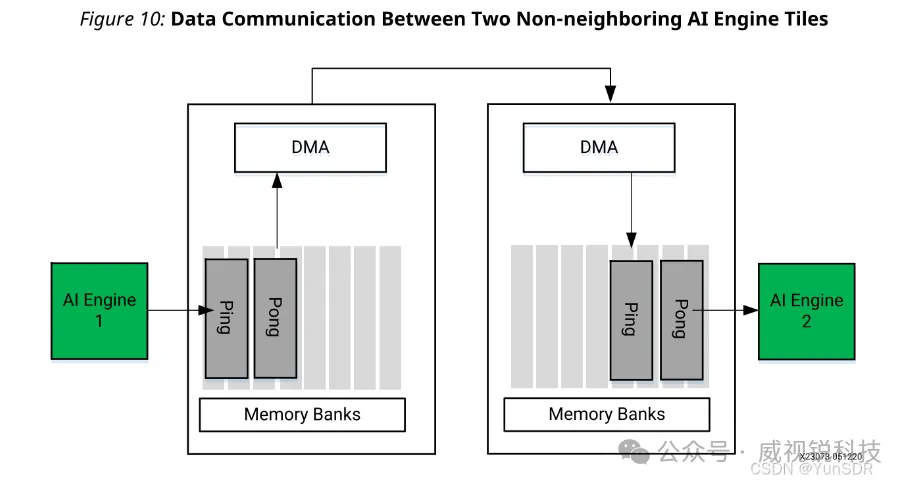

(2)通过内存和DMA进行AI Engine瓦片到AI Engine瓦片的数据通信

上一节中描述的通信是在AI Engine Tile内部或两个相邻的AI Engine图片之间进行的。对于非相邻的AI Engine区块,可以使用与每个AI Engine区块关联的内存模块中的DMA建立类似的通信,如下图所示。每个内存模块中ping-pong缓冲区的同步由锁以类似于通过共享内存部分进行AI Engine到AI Engine数据通信的方式进行。主要区别在于通信延迟和内存资源的增加。

(3)通过AXI4流互连进行AI Engine瓦片到AI Engine瓦片的数据通信

AI Engine可以直接通过AXI4流互连进行通信,而无需任何DMA和内存交互。如下图所示,数据可以通过流媒体接口以串行方式从一个AI Engine发送到另一个,或者可以使用多播通信方法将相同的信息发送到任意数量的AI Engine Tile。溪流可以流向北/南和东/西。在所有流动情况下,都有内置的握手和背压机制。注意:在多播通信方法中,如果其中一个接收器未就绪,则整个广播将停止,直到所有接收器再次就绪。

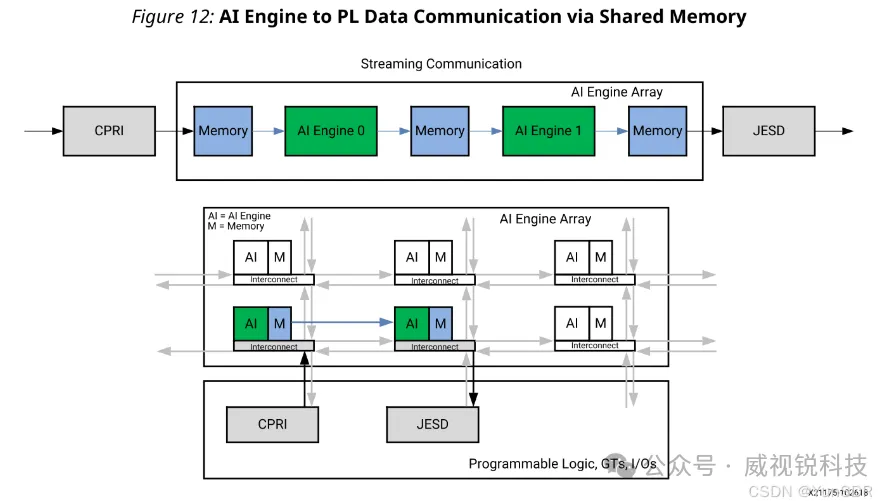

(4)通过共享内存进行AI Engine到PL数据通信

在一般情况下,PL块通过流接口消耗数据。然后,它生成一个数据流并将其转发到阵列接口,其中有一个FIFO接收PL流并将它转换为AI Engine流。然后,AI Engine流被路由到AI Engine目标函数。根据通信是基于块还是基于流,可能涉及DMA和ping-pong缓冲区。

下图显示了公共公共无线电接口(CPRI™)和PL中的JESD®之间的示例(用例)。AI Engine和PL可以使用AI Engine Tile中的DMA进行通信。DMA将流移动到与消费AI Engine相邻的内存块中。第一个图表示逻辑视图,第二个图表示物理视图。

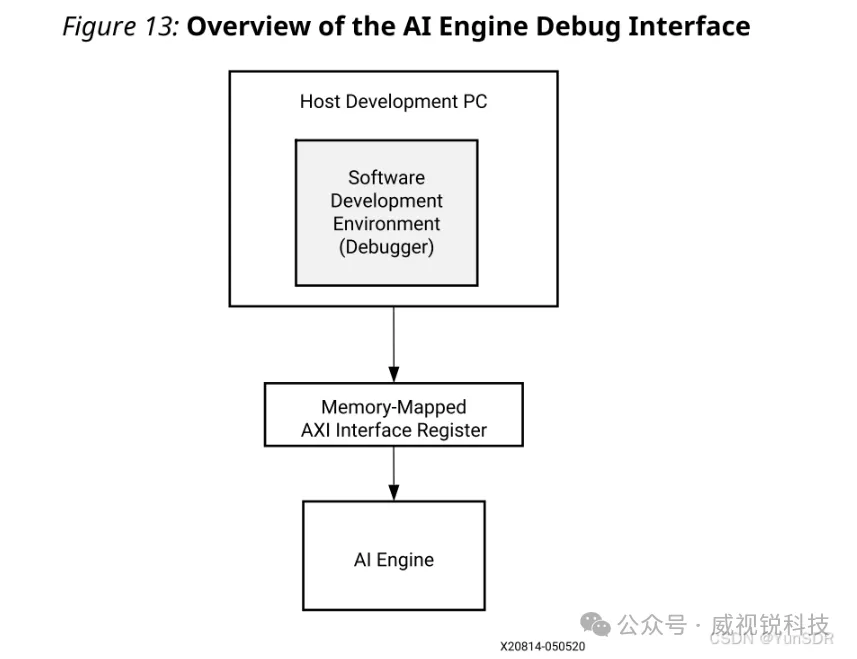

AI Engine调试

调试AI Engine使用内存映射的AXI4接口。AI Engine阵列中的所有主要组件都是内存映射的

•程序存储器

•数据存储器

•AI Engine寄存器

•DMA寄存器

•锁定模块寄存器

•流开关寄存器

•AI Engine断点寄存器

•事件和性能计数器寄存器

这些内存映射寄存器可以从任何可以产生内存映射AXI4接口请求(PS、PL和PMC)的主机上读取和/或写入。这些请求通过NoC到达AI Engine阵列接口,然后到达阵列中的目标tile。下图显示了一个典型的调试设置,涉及在主机开发系统上运行的软件开发环境及其集成调试器。

调试器使用JTAG连接或AMD高速调试端口(HSDP)连接连接到启用AI Engine的Versal设备上的平台管理控制器(PMC)。

AI Engine跟踪和分析

AI Engine Tile具有跟踪和分析功能。它还具有控制跟踪和分析硬件的配置寄存器。

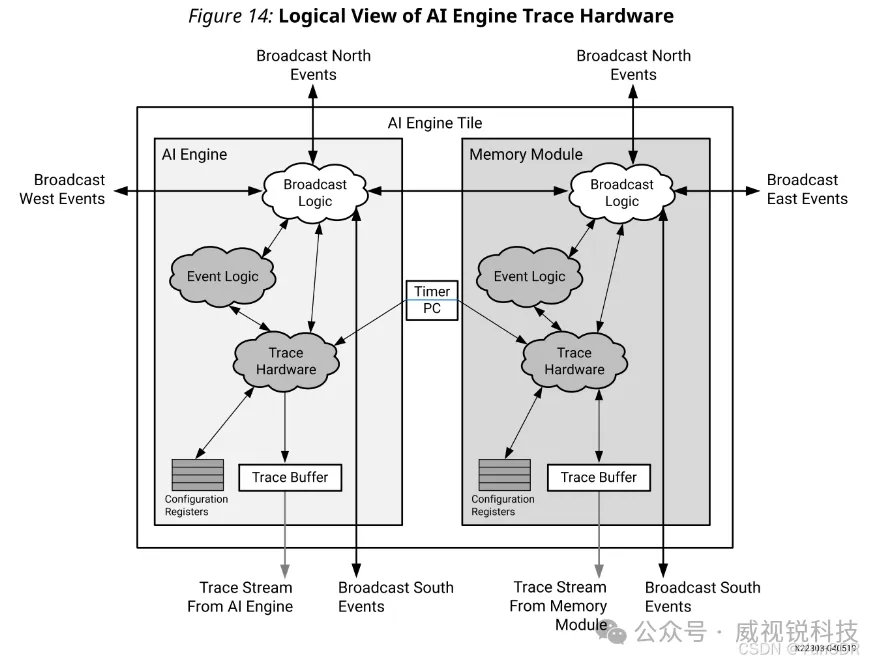

(1)Trace

每个AI Engine Tile都有两个跟踪流。一个流来自AI Engine,另一个来自内存模块。这两个流都连接到tile流交换机。在AI Engine Tile中的每个AI Engine模块和内存模块中都有一个跟踪单元,在AI Engine PL接口tile中有一个AI Engine可编程逻辑(PL)模块(参见阵列接口tile的类型)。这些单元可以在以下模式下运行:

○事件时间

○事件PC

○执行跟踪

•AI Engine内存模块模式

○事件时间

•AI Engine PL模块模式

○事件时间

跟踪通过AXI4流作为AI Engine分组交换流分组从单元输出。数据包大小为8x32位,包括一个报头字和七个数据字。阵列AXI4流交换机使用数据包头中包含的信息将数据包路由到它可以路由到的任何AI Engine目的地,包括通过AI Engine块DMA的AI Engine本地数据存储器、通过AI Engine阵列接口DMA的外部DDR存储器,以及通过AI Engine到PL AXI4码流的块RAM或URAM。

事件时间模式在每个周期内最多跟踪八个独立编号的事件。创建跟踪帧以记录跟踪事件中的状态变化。这些帧被收集在输出缓冲区中,形成AI Engine分组交换流分组。多个帧可以打包成一个32位流字,但它们不能跨越32位边界(填充帧用于32位对齐)。

在事件PC模式下,每个周期都会创建一个跟踪帧,在该帧中,八个监视的事件中的任何一个或多个都会被断言。跟踪帧记录AI Engine的当前程序计数器(PC)值以及八个观看事件的当前值。这些帧被收集在输出缓冲区中,形成AI Engine分组交换流分组。

AI Engine中的跟踪单元可以在执行跟踪模式下运行。实时地,该单元将通过AXI4流发送一组最小的信息,以允许离线调试器重建程序执行流。这假设脱机调试器可以访问ELF。信息包括:

•有条件和无条件的直接分支

•所有间接分支

•零开销环路LC

AI Engine生成基于数据包的执行跟踪,可以通过32位宽的执行跟踪接口发送。下图显示了AI Engine Tile中跟踪硬件的逻辑视图。从tile中输出的两个跟踪流在内部连接到事件逻辑、配置寄存器、广播事件和跟踪缓冲区。注:未显示两个模块之间的不同操作模式。

为了控制事件跟踪的跟踪流,有一个32位的trace_control0/1寄存器来启动和停止跟踪。还有trace_event0/1寄存器,用于对要添加到跟踪中的内部事件号进行编程。有关具体寄存器信息,请参阅Versal Adaptive SoC AI Engine寄存器参考(AM015)。

(2)Profiling(性能计数器)

AI Engine阵列具有可用于分析的性能计数器。AI Engine有四个性能计数器,可以配置为对任何内部事件进行计数。它将计算事件的发生次数或两个定义事件之间的时钟周期数。PL和NoC阵列接口块中的存储器模块和PL模块每个都有两个性能计数器,可以配置为执行类似的功能。下图显示了AI Engine Tile中分析硬件的高级逻辑视图。性能控制寄存器和性能计数器寄存器在Versal自适应SoC AI Engine寄存器参考(AM015)中进行了描述。

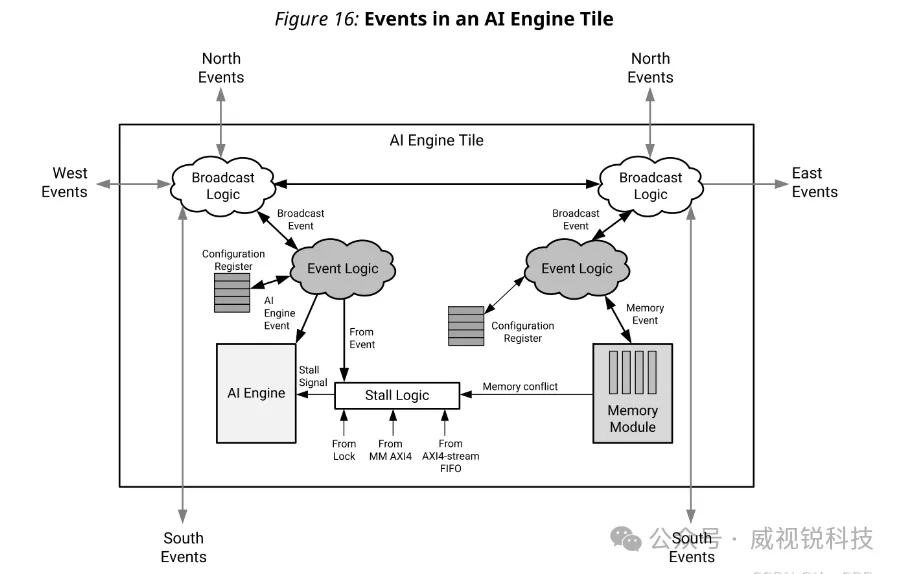

AI Engine事件

AI Engine和内存模块每个都有一个事件逻辑单元。每个单元都有一组定义好的本地事件。下图显示了AI Engine Tile中事件的高级逻辑视图。事件逻辑需要配置一组动作寄存器,这些寄存器可以通过内存映射的AXI4接口进行编程。存在仅与AI Engine和内存模块交互的事件逻辑硬件。事件操作可以配置为在特定事件发生时执行任务。事件硬件有两组单独的配置寄存器。此外,还有单独的广播逻辑来向相邻模块发送事件信号。

(1)事件操作

事件本身没有操作,但事件可用于创建操作。可以配置事件广播和事件跟踪来监视事件。事件操作的示例包括:

•启用、禁用或重置AI Engine

•调试AI Engine的暂停、恢复或单步

•AI Engine错误停止

•重新同步计时器

•启动和停止性能计数器

•启动和关闭跟踪流

•生成广播事件

•驱动器组合事件

•ECC清理事件

对于这些事件操作中的每一个,都有相关的寄存器,其中设置了一个7位事件编号,用于配置在给定事件上触发的操作。AI Engine和内存模块的事件操作配置寄存器的完整列表可以在Versal Adaptive SoC AI Engine寄存器参考(AM015)中找到。

(2)ECC擦除事件

擦除用于检测程序存储器和数据存储器中的2位ECC错误并纠正1位ECC错误。清理可以通过用户事件启动。有一个寄存器可以用事件号编程,以开始对事件进行清理。如果此寄存器未编程,则跳过擦除。当ECC清理纠正程序存储器中的1位错误并检测到2位错误时,AI Engine中会生成事件。当ECC清理纠正数据存储体中的1位错误并检测到2位错误时,AI Engine内存模块中会生成事件。您可以使用性能计数器计算事件的发生次数。这些计数器可以作为计时器,可以根据事件启动和停止。这有助于计算两个事件之间的时钟数量。

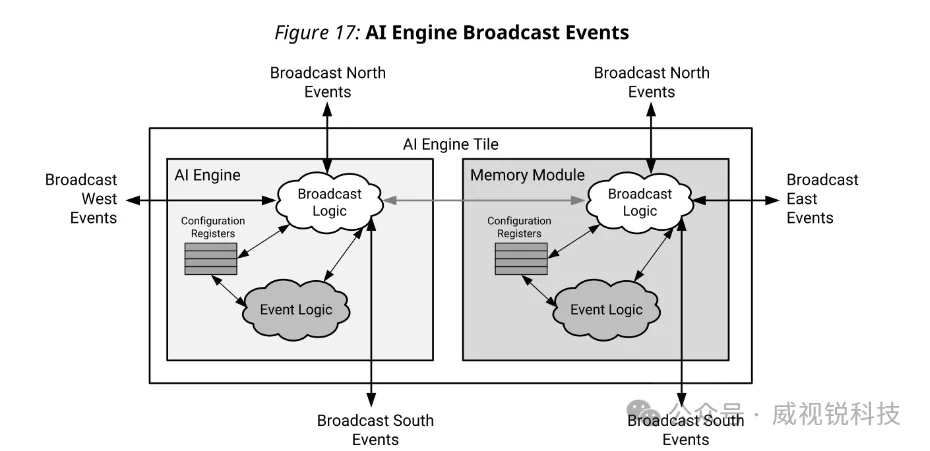

(3)事件广播

广播事件既是事件又是事件操作,因为它们是在配置的事件被断言时触发的。下图显示了AI Engine Tile内广播逻辑的逻辑视图。AI Engine和内存模块中的广播逻辑中的单元从所有四个方向接收输入并发送信号。广播逻辑连接到生成所有事件的事件逻辑。有配置寄存器用于选择发送的事件,还有掩码寄存器用于阻止任何事件从AI Engine Tile中传出。

每个模块都有一个内部寄存器,用于确定在其他方向上广播的广播事件信号。为了避免广播循环,传入事件信号与内部事件进行OR运算,以根据以下列表驱动传出事件信号:

•内部、东部、北部、南部→西部

•内部、西部、北部、南方→东部

•内部、南部→北部

•内部、北部→南部

提示:AI Engine模块东部广播事件接口在内部连接到内存模块西部广播事件接口,不会离开AI Engine Tile。在AI Engine模块中,有16个广播事件,分别在北、南和西方向。在内存模块中,有16个广播事件,分别位于北、南和东方向。关于广播事件,从程序员的角度来看,奇数行和偶数行之间的接口没有区别。

文章来源:威视锐科技