AI Engine 阵列接口架构

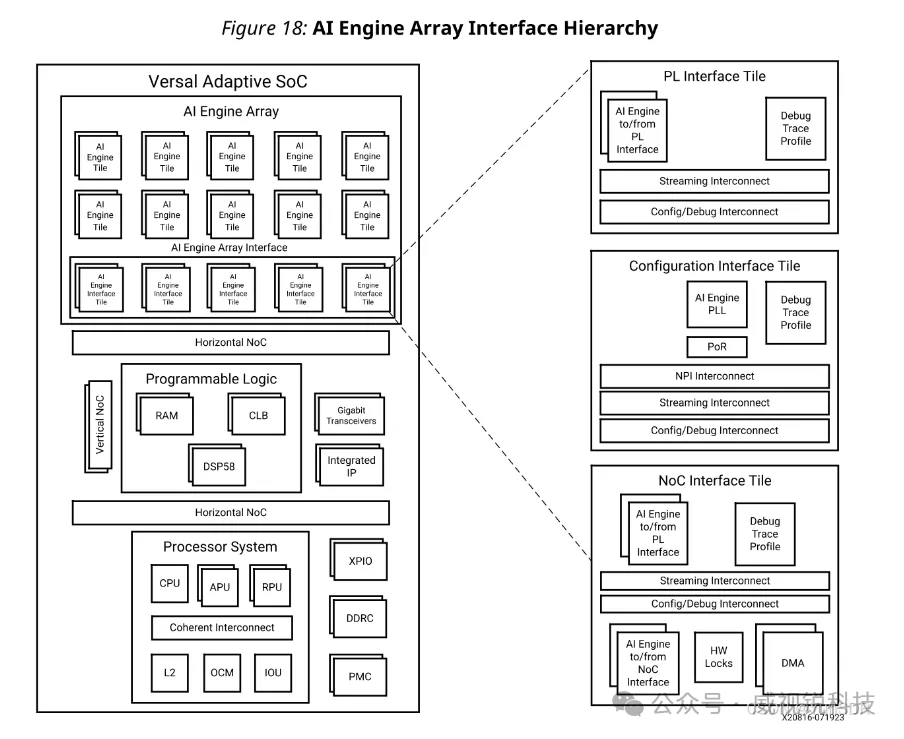

AI Engine以二维阵列的形式排列,如下图所示。AI Engine阵列接口提供与设备其余部分接口所需的功能。AI Engine阵列界面有三种类型的AI Engine界面平铺。AI Engine阵列的每一列都有一对一的接口Tile对应。接口Tile形成一行,并水平(左和右)移动内存映射的AXI 4和AXI 4-Stream数据,并垂直向上移动AI EngineTile列。AI Engine接口模块基于模块化架构,但最终的组成是特定于设备的。AI Engine阵列中AI Engine阵列接口的内部层次结构如下图所示。

本节介绍阵列接口tile的类型及其内部的模块。

• AI EnginePL接口模块: PL模块包括: -AXI 4-流开关 -存储器映射的AXI 4开关 - AI Engine到PL流接口 -控制、调试和跟踪单元 • AI Engine配置接口模块(每个AI Engine阵列正好一个实例): 用于AI Engine时钟生成的PLL 上电复位(POR)单元 PLL生成单元 动态功能交换(DFx)逻辑 NoC外围互连(NPI)单元 AI Engine阵列全局寄存器,其控制全局特征,诸如PLL/时钟控制、安全/非安全行为、中断控制器、全局复位控制和DFx逻辑 • AI EngineNoC接口Tile: ○ PL模块(参见先前描述) ○具有到NMU和NSU的接口的NoC模块包括: -双向NoC流接口 -阵列接口DMA

AI Engine阵列接口

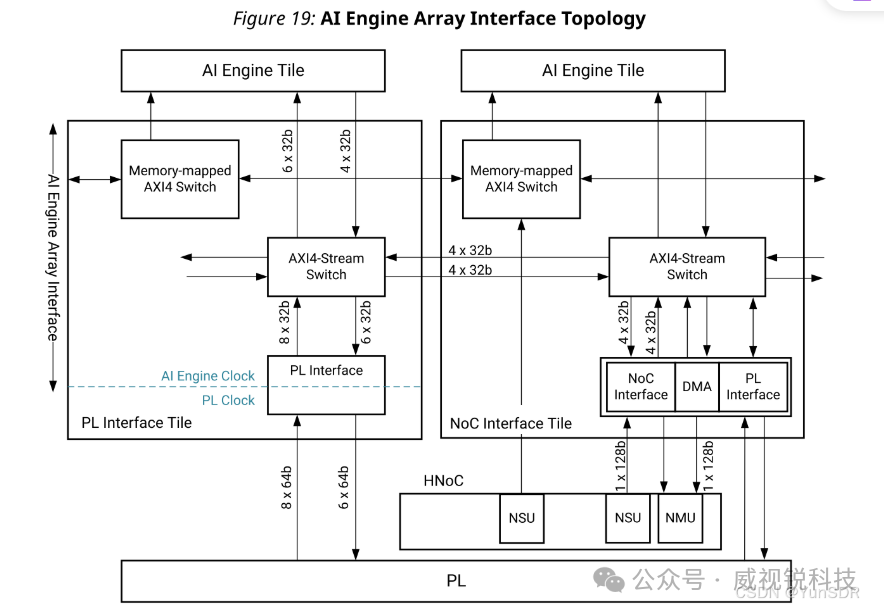

AI Engine接口由PL和NoC接口Tile组成。每个设备还有一个配置界面Tile。下图显示了AI Engine阵列用于与Versal架构中的其他模块通信的阵列接口连接。还指定了与PL、NoC或AI EngineTile接口的AXI 4-Stream互连中以及AXI 4-Stream交换机之间的流的数量。

注:对于-1L速度级设备,AI EngineFMAX为1 GHz。PL时钟应设置为该速度的一半,即500 MHz。在用于AI Engine和NoC的时钟之间的NoC接口Tile处也存在时钟域交叉。

到PL和NoC的接口类型是:

•存储器映射AXI 4接口:通信信道是从NSU到作为从机的AI Engine

•AXI 4-流互连具有三种类型的接口:

○与PL流接口的双向连接

○与使用存储器生成进入NoC的流量的阵列接口DMA的连接-映射的AXI 4接口

○直接连接到NoC流接口(NSU和NMU)

AI Engine阵列接口Tile管理两个高性能接口:

• AI Engine到PL

• AI Engine到NoC

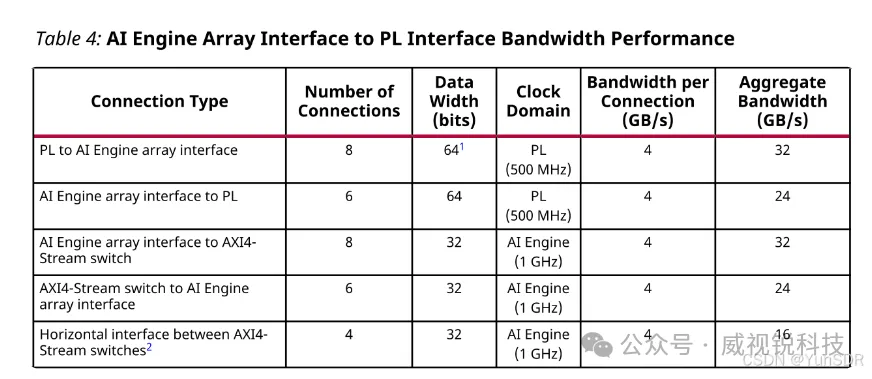

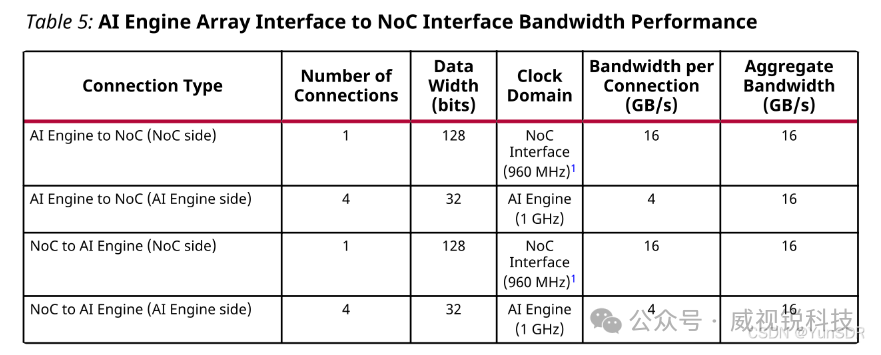

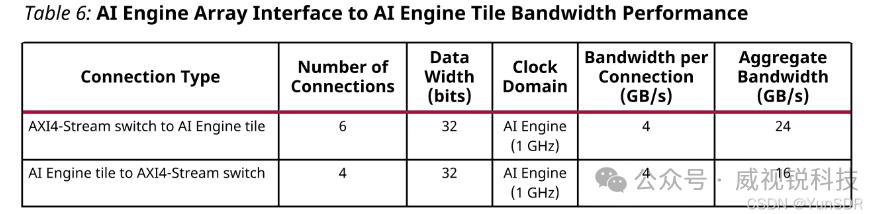

下表总结了AI Engine阵列与PL、NoC和AI EngineTile接口的带宽性能。对于-1L速度等级设备,每个AI Engine列都规定了带宽性能。PL到AI Engine接口和AXI 4-Stream交换机到AI Engine模块之间的每列连接数量减少。这是为了支持提供额外水平路由能力的水平连接流交换机。不同速度等级的各种器件的总带宽可以在Versal AI Core系列数据表:DC和AC开关特性(DS 957)中找到。

注:1.所有去往和来自PL的流在PL侧是64比特。流可以转换为32位宽,但64位宽的流中只有一个32位字有效。两个64位宽的流可以组合成一个128位宽的流,但连接数量减半。2.所示的聚合带宽在东/西方向上。每个AXI 4-Stream交换机有两组连接进出。

注:1.频率基于-1L速度等级。

AI Engine阵列接口的功能

•内存映射AXI 4互连:提供将传入的内存映射AXI 4请求从NoC传输到AI Engine阵列内部的功能。

•AXI 4-流互连:利用AI EngineTile流互连功能。

• AI Engine到PL接口:AI Engine PL模块直接与PL通信。异步FIFO用于处理时钟域交叉。

• AI Engine to NoC Interface:AI Engine to NoC模块负责将128位片上网络流转换为32位AI Engine流(反之亦然)。它为片上网络组件(NMU和NSU)提供接口逻辑。执行电平转换是因为NMU和NSU与AI Engine处于不同的功率域中。

•硬件锁:利用AI Engine tile中的相应单元,并可从AI Engine阵列接口或外部存储器映射AXI 4主机访问,该模块用于同步阵列接口与外部存储器的DMA传输。

•调试、跟踪和分析:利用AI Engine图块中的所有特性进行本地事件调试、跟踪和分析。

阵列接口内存映射AXI4互连

AI Engine内存映射AXI 4互连的主要任务是允许外部访问内部AI EngineTile资源,如内存和寄存器,以进行配置和调试。它的设计目的不是将大部分数据移动到AI Engine阵列或从AI Engine阵列进行数据移动。内存映射的AXI 4接口都通过AI Engine阵列接口行互连。这使得阵列接口Tile中的存储器映射的AXI 4互连能够将传入的存储器映射的信号水平地移动到正确的列,然后通过开关将它们垂直地转发到该列的底部AI EngineTile中的存储器映射的AXI 4互连。

每个内存映射的AXI 4接口都是一个32位地址和32位数据。最大内存映射AXI 4带宽设计为1.5 GB/s。

为了馈送存储器映射的AXI 4接口,NoC模块包含存储器映射的AXI 4桥,其接受来自NoC NSU接口的存储器映射的AXI 4传输,并且充当内部存储器映射的AXI 4接口开关的存储器映射的AXI 4主设备。

阵列接口AXI 4-流互连

AI EngineAXI 4-Stream交换机的主要任务是在AI Engine和可编程逻辑或NoC之间传送确定的吞吐量和高速电路或分组数据流。因此,它被设计为将大部分数据移动到AI Engine阵列或从AI Engine阵列移出。AI EngineTile底部行中的AXI 4-Stream开关直接与AI Engine阵列接口中的另一行AXI 4-Stream互连开关连接。

AI Engine到可编程逻辑接口

AI Engine中的AXI 4-Stream交换机到PL模块可以使用AXI 4-Stream接口直接与可编程逻辑通信。从AI Engine到PL有六个流,从PL到每个AI Engine列有八个流。从带宽的角度来看,每个AXI 4Stream接口都可以支持以下功能。

• 24 GB/s从每个AI Engine列到PL • 32 GB/s从PL到每个AI Engine列 在VC1902设备中,有50列AI EngineTile和AI Engine阵列接口Tile,但是,只有39个阵列接口Tile可用于PL接口。因此,PL接口的总带宽约为: • 1.0 TB/s从AI Engine到PL • 1.3 TB/s从PL到AI Engine 所有带宽计算均假定-1L速度等级器件的标称1 GHz AI Engine时钟为VCCINT = 0.70 V。PL接口可用的阵列接口片数量以及AI Engine到其他设备和不同速度等级的PL接口的总带宽在Versal AI Core系列数据表:DC和AC开关特性(DS 957)中指定。 边界逻辑接口触发器位于AI Engine与PL接口之间。它们可以用来改善时间。通过将边界逻辑接口(BLI)约束应用于设计中的触发器,您可以在设计布局期间自动利用此功能。请参阅《通用自适应SoC系统集成和验证方法指南》(UG 1388)中的“AI Engine-PL时序接口技术"部分。

AI Engine到NoC接口

除了AXI 4-Stream接口功能之外,AI Engine到NoC接口Tile还包含连接到水平NoC(HNoC)的路径。从AI Engine来看,从AI Engine到NoC有四个流,从NoC到AI Engine有四个流。从带宽的角度来看,每个AI Engine到NoC接口Tile可以在HNoC和AXI 4-Stream交换机之间引导流量。

提示:实际的总带宽可能受到设备中可用的水平和垂直信道的数量以及NoC的带宽限制的限制。

中断处理

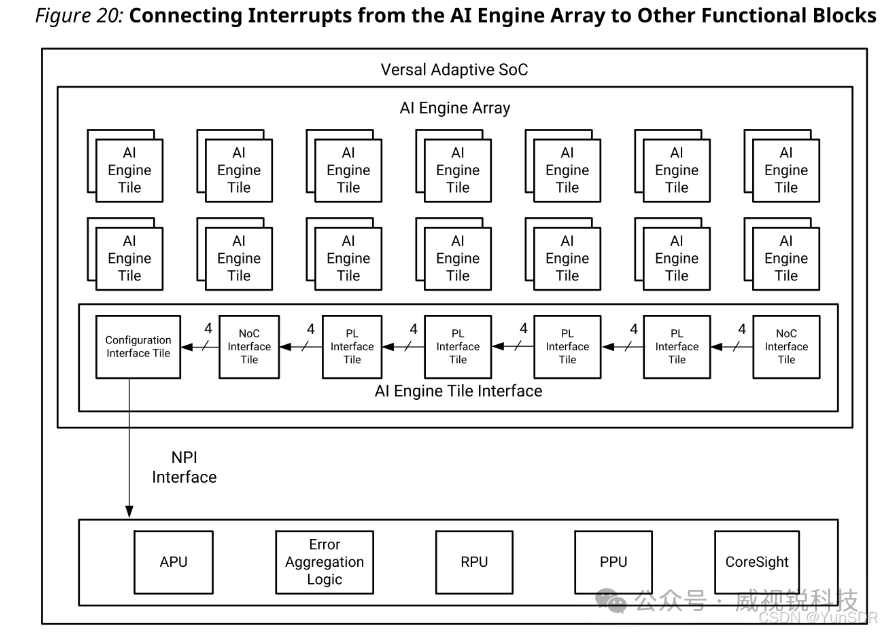

可以设置中断到处理器系统(PS)和平台管理控制器(PMC),由AI Engine阵列内的事件触发。本节介绍AI Engine阵列的中断类型。AI Engine阵列生成四个中断,这些中断可以从AI Engine阵列路由到PMC、应用处理单元(APU)和实时处理单元(RPU)。从AI Engine阵列生成中断的总体层次结构如下:

•事件从任何AI EngineTile或AI Engine接口Tile触发。

•每一列都有一级中断处理程序,可以捕获生成的触发器/事件并将其转发给二级中断处理程序。二级中断处理程序仅在NoC接口中可用。

•第二级中断处理程序可以驱动AI Engine阵列接口中的四条中断线中的任何一条。

•这四条中断线最终连接到AI Engine配置接口模块。下图是一个高级框图,显示了从AI Engine阵列到Versal设备中其他模块的NPI中断连接。该图未显示阵列接口Tile和AI EngineTile的实际布局/放置。

在上图中,四个中断是从一个NoC接口片生成的。它们通过PL接口Tile并到达配置接口Tile。然后,内部错误(如PLL锁定丢失)与四个传入中断进行OR运算,得到的四个中断直接连接到NPI接口上的NPI中断信号,NPI接口是一个32位宽的存储器映射AXI4总线。

在器件级,四个NPI中断分配为4到7。有三组NPI寄存器(IMR0.IMR3、IER0.IER3和IDR 0.IDR 3)。每一对(IMR、IER和IDR)都可以用来配置四个NPI中断。IMR寄存器是只读的,IER和IDR寄存器是只写的。只能对与NPI中断4对应的寄存器进行编程。对于NPI中断5、6和7,三组寄存器无效,并且不能通过对NPI寄存器进行编程来屏蔽这三个中断。NPI寄存器的结构和地址在《通用自适应SoC AI Engine寄存器参考》(AM015)中进行了描述。

文章来源:威视锐科技