智多晶eSPI_Slave IP

eSPI总线具有低功耗、管脚数量少、高效的数据传输等优点,常用于与EC、BMC、SIO等外设的通信,是PC中CPU与这些外设通信的主流协议。智多晶eSPI_Slave IP符合eSPI标准规范,支持相关协议属性。

eSPI_Slave IP特性:

支持Single SPI、Dual SPI和Quad SPI模式;

支持所有eSPI命令;

提供apb用户接口;

为flash通道事务提供apb接口;

为带外通道事务提供apb接口;

为外设通道事务提供apb接口;

为虚拟线通道事务提供GPIO拓展接口和Simple_vwire接口;

支持错误检测。

典型应用

芯片间通信:eSPI协议主要用于现代计算机系统中CPU与各种外围设备之间的通信,它取代了传统的LPC总线,成为新一代的通信协议;

低功耗和低引脚需求:eSPI协议具有低功耗和低引脚数量的特点,这使得它在需要节省能源和减少硬件成本的场景中非常适用;

实时数据传输:eSPI协议支持实时数据传输,特别是在需要快速响应的应用中,如系统管理、安全管理和远程管理等功能。这使得eSPI在服务器管理和远程控制中具有重要应用。

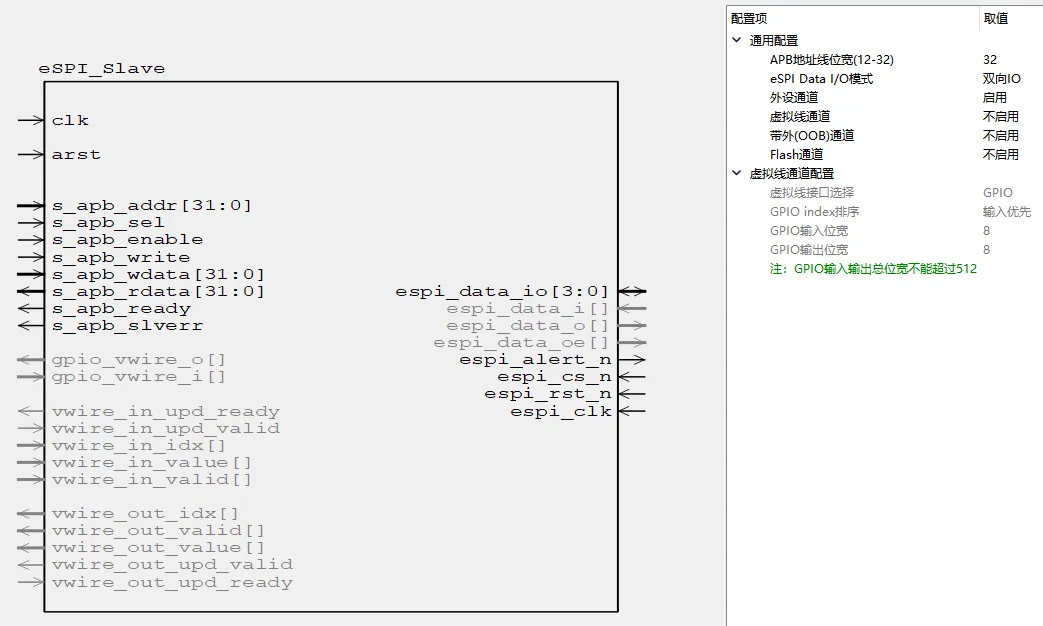

eSPI_Slave IP界面配置

在配置界面,用户可配置是否使用双向eSPI Data I/O,可根据需求启用通道。

如果启用虚拟线通道,可根据需求选择虚拟线通道接口。对于GPIO接口,支持对GPIO的输入输出位宽和GPIO的index排序进行配置。

如需了解更多关于智多晶eSPI_Slave IP的信息,请联系本公司FAE团队。

文章来源:智多晶