引言

随着AI、HPC及超大规模芯片设计需求呈指数级增长原型验证平台已成为芯片设计流程中验证复杂架构、缩短迭代周期的核心工具。然而,传统原型验证系统受限于单芯片容量(通常<5000万门)、多芯片分割效率及系统级联能力,难以支撑上亿门级以上设计的全场景验证需求。

为应对这一挑战,行业亟需兼具超大规模容量、高效分割算法与跨芯片级联能力的下一代原型验证。AMD Versal™ Premium VP1902自适应SoC凭借单核等效1亿门容量,成为构建高性能仿真与原型验证系统的理想硬件底座。思尔芯芯神瞳逻辑系统S8-100通过搭载AMD VP1902,并配套自主研发的智能分割工具链,显著提升超大规模设计的原型验证效率。本文以芯神瞳逻辑系统S8-100与芯神瞳逻辑矩阵 LX2(采用VU19P)在多芯片级联场景下的性能数据对比,揭示S8-100在容量、速度的显著优势。

芯神瞳逻辑系统S8-100自去年上市以来,凭借其卓越的性能表现获得了国内外头部芯片设计厂商的广泛采用。作为新一代原型验证解决方案,S8-100系列提供灵活的单核、双核及四核配置,可全面满足从边缘计算到数据中心等不同规模的AI和HPC芯片设计验证需求。通过搭载AMD Versal™ Premium VP1902,S8-100单核即可提供约1亿等效逻辑门的容量,较思尔芯上一代产品实现两倍的容量提升。同时,其创新的多系统级联架构能够轻松应对超大规模芯片设计的验证挑战。

在当今超大规模芯片验证领域,单纯比较单颗FPGA的性能指标已无法反映实际工程需求。随着AI和HPC芯片设计规模普遍突破上亿门级,多FPGA分割验证已成为行业标配。为此,我们针对思尔芯S8-100与传统VU19P方案进行了系统级对比测试。

S8-100Q:搭载 4颗AMD Versal VP1902 FPGA,单颗VP1902等效容量约1亿门,通过FPGA级联,总容量高达4亿门。 LX2:采用 8颗AMD VU19P FPGA 级联,单颗VU19P等效容量约5000万门,总容量与S8-100Q相当。

使用思尔芯配套软件PlayerPro-CT(2024.2)进行设计组网与自动分割,先组网后分割 使用Vivado2024.2完成物理实现 完全使用软件自动分割,启用统一优化策略:TDM感知、自动全局优化等

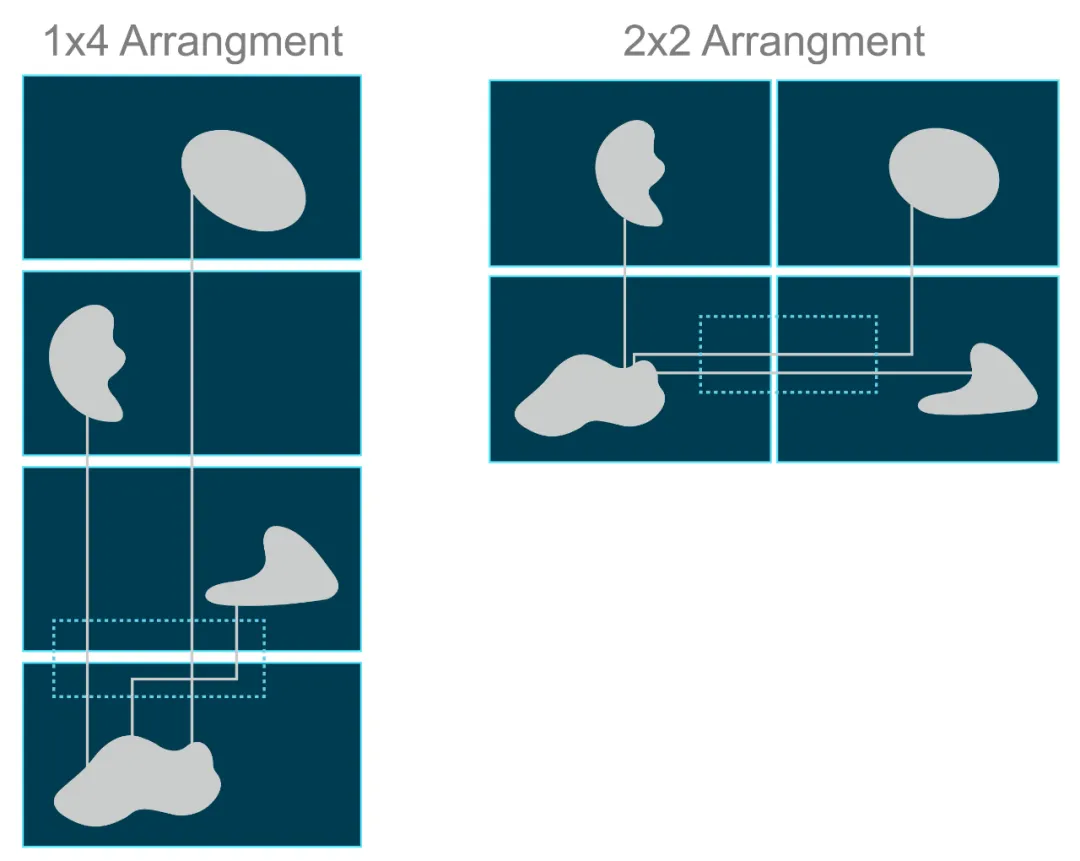

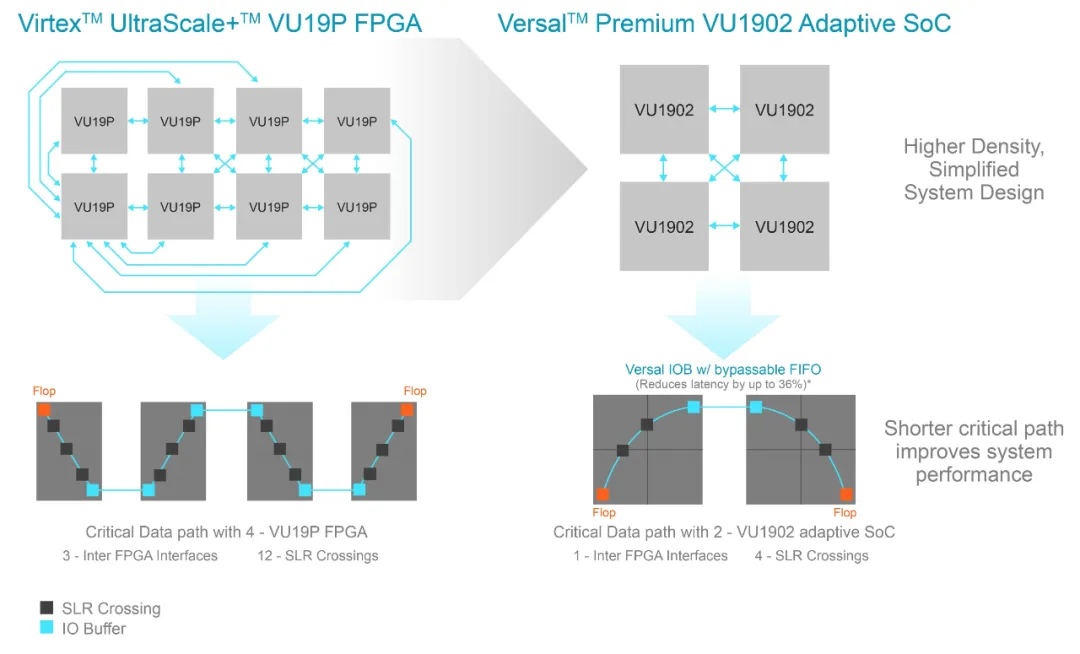

架构优化:采用改进的布线架构,支持更大规模器件。器件尺寸提升2倍,单颗芯片可集成更多设计。Die采用2x2排列,最远路径从3阶缩短至2阶,减少性能损耗。

级联优化:VP1902容量扩大后分割更高效,SLR(超长线资源)跨区减少,互联简化,FPGA跨区整体大幅降低。 I/O优化:I/O延迟仅为UltraScale+架构的64%

更多白皮书,可登录思尔芯官网www.s2ceda.com点击“热门资源-技术文档”下载。