作者:Shaoyi Chen,AMD开发者;来源:AMD开发者社区

在使用 VPK120 开发板进行高性能 FPGA 设计时,用户常常需要根据具体应用对外部时钟源进行定制,以满足不同模块对频率的要求。VPK120 板载的 8A34001 可编程时钟芯片支持多路时钟输出,具备灵活配置的能力。为了适配特定设计场景(如高速接口、图像处理、AI 运算等),工程师通常需要修改某一路时钟输出的频率,例如将 Clock10 调整为 100 MHz。 本文将详细介绍如何在 VPK120 上修改 8A34001 时钟频率的完整流程,包括所需工具准备、配置修改、文件部署与最终验证,帮助用户快速完成定制化时钟配置。

从IDT官网下载Timing Commander软件。

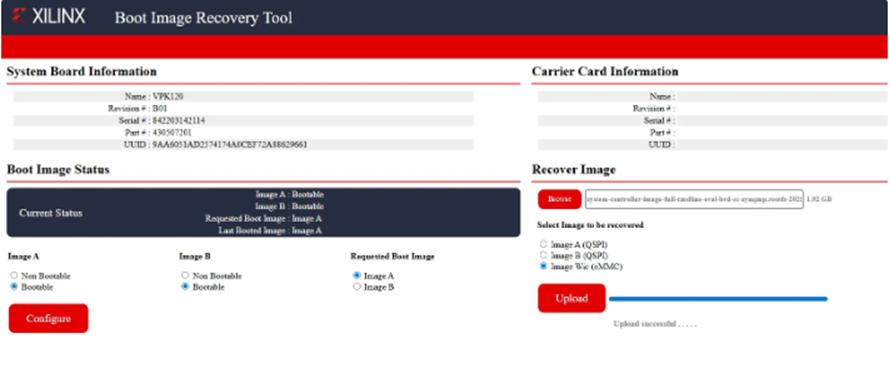

同时将开发板的SC固件更新到最新的7.1。

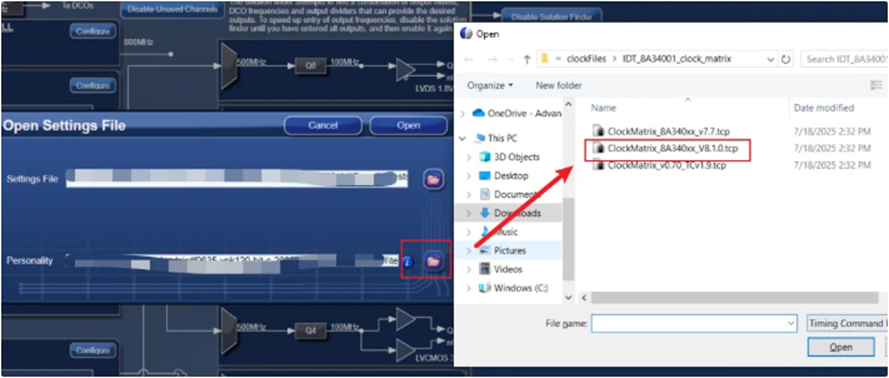

打开BoardUI中携带的setting模板。

指定personality文件:

修改为想要的频率,我们这里将clock10修改为100MHz:

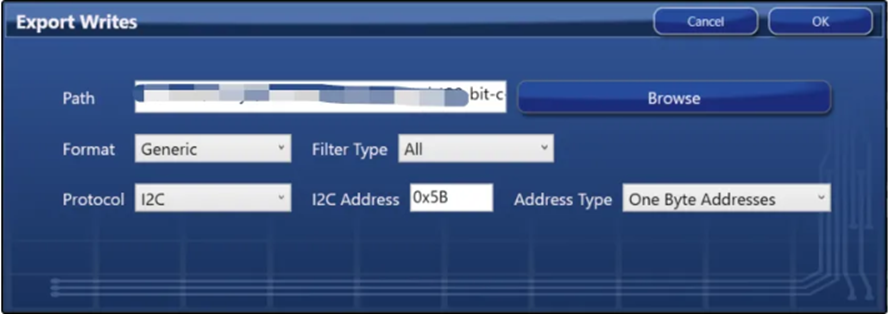

将设置导出。

同时将工程文件tcs保存。

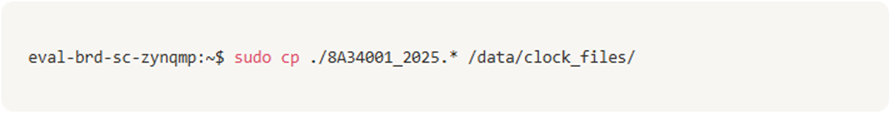

将tcs和txt文件上传到SC系统里,tcs和txt需要同时存在才可以下载。文件默认存放的位置为/data/clock_files/

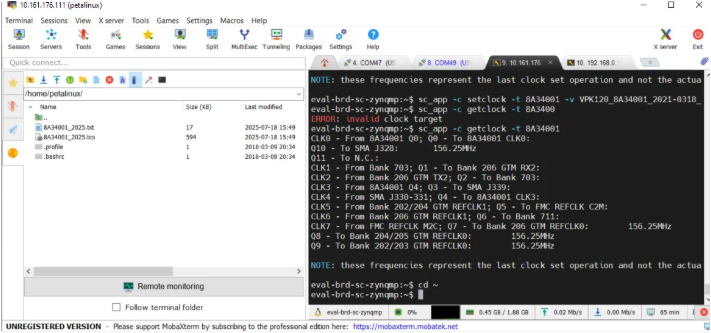

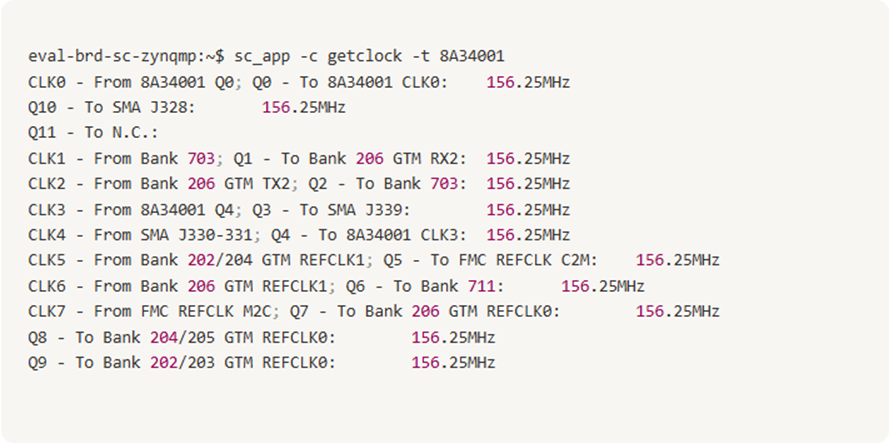

首先查询板卡的时钟信息。

sc_app -c getclock -t 8A34001

将板卡文件传输到/data/clock_files/目录下。

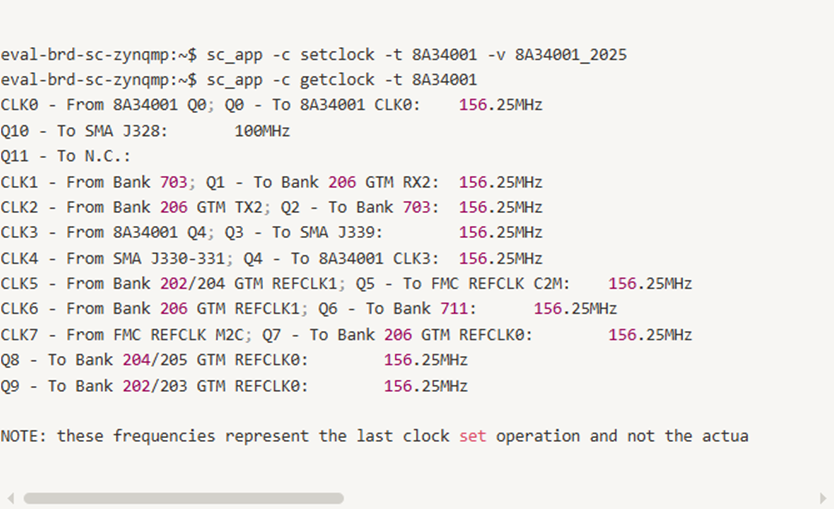

设置频率

观察到Q10的频率已经改变。