本篇主要介绍TTL/CMOS电平的互连、OC/OD的互连,其余单端逻辑电平的互连可参考相关器件规范、电平规范。

1、TTL/CMOS互连

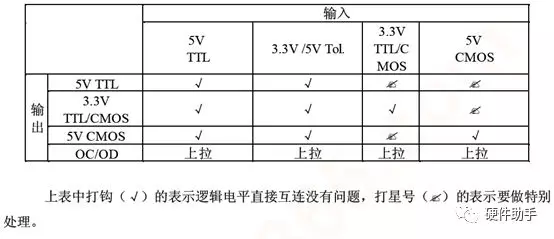

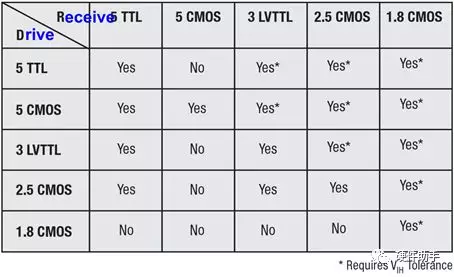

常用的TTL和CMOS电平主要是5V TTL、5V CMOS、3.3VTTL、3.3V CMOS、3.3V/5V Tol(输入时3.3V逻辑电平,但是可以接受5V的信号输入)等,随着处理器电压越来越低,现在1.8V CMOS等低电压的逻辑电平也越来越普及了。

针对各种单端逻辑电平,只要上一级的输出电压不满足下一级的输入电压,就不能直接进行互连,后续会专门介绍逻辑电平的转换。

|

5V TTL门作驱动源 |

驱动3.3V TTL/CMOS |

通过LVC/LVT系列器件(为TTL/CMOS逻辑电平输入,LVTTL逻辑电平输出)进行转换。 |

|

驱动5V CMOS |

上拉5V电阻,或使用AHCT系列器件(为5VTTL输入、5VCMOS输出)进行转换。 |

|

|

5V CMOS门作驱动源 |

驱动3.3V TTL/CMOS |

通过LVC/LVT器件(输入是TTL/CMOS逻辑电平,输出是LVTTL逻辑电平)进行转换。 |

|

3.3V TTL/CMOS门作驱动源 |

驱动5V CMOS |

使用AHCT系列器件(为5V TTL输入、5VCMOS输出)进行转换(3.3V TTL电平(LVTTL)与5V TTL电平可以互连)。 |

|

驱动2.5V CMOS |

使用LV、LVC、AVC、ALVT系列器件来进行3.3VTTL/CMOS逻辑电平到2.5V CMOS逻辑电平的转换。 |

|

|

2.5V CMOS门作驱动源 |

驱动3.3V TTL/CMOS |

使用双轨器件SN74LVCC3245A来进行2.5V逻辑电平到3.3V逻辑电平的转换。 |

***上表中的所有互连方式都可以通过外部MOS管等分离器件搭建。

2、OC/OD互连

针对OC/OD逻辑门,为了保证输出高电平的值,必须进行外部上拉处理,上拉电阻的选取可以参考相关总线的标准,也可以参考《I2C Bus Pull up Resistor Calculation》、《Choosing an Appropriate Pull-up/Pull-down Resistor for Open Drain Outputs》等文章。相同电压的OC/OD逻辑电平可以直接互连,不同电压的OC/OD需要进行电平转换,可以采用独立的MOS管搭建,也可以采用专门的OC/OD总线转换芯片实现(专用芯片的节本架构也是基于MOS管的,只是多了外围电路以及一些辅助的功能电路)。下面就针对采用MOS管进行OC/OD电平转换进行介绍,使用专用芯片进行转换的方式后续再介绍。

针对上述电路分析如下:

a、3.3V→5V转换过程:

b、5V→3.3V转换过程:

以上就是针对TTL/CMOS,OC/OD逻辑电平的互连介绍,后续会针对专门的逻辑电平转换进行介绍。

文章转载自:硬件助手