作者:鹏哥DIY

来源:CSDN

对ZYNQ的学习的渴望由来已久,前不久买了一个基于xc7z010的开发板,现在将自己的学习的进阶之路记录在此,希望能给想要入门的ZYNQ学习者一点帮助,本人也刚开始学习,能力有限,其中若有不足之处希望大家多多交流,以便共同进步!

xilinx ZYNQ-7000系列芯片将处理器的软件可编程能力与FPGA的硬件可编程能力实现了完美结合,有低功耗和低成本等系统优势,可以实现无与伦比的系统性能、灵活性和可扩展性,同时可以加速产品的上市进程。与传统的SoC处理解决方案不同,ZYNQ-7000器件的灵活可编程逻辑能实现优化与差异化功能,使设计人员可以根据大部分应用的要求添加外设和加速器。

下面我们从最基本的LED流水灯开始ZYNQ的进阶之路,教程使用的开发板使用的是xc7z010这颗芯片,芯片内部包含双核cortex-A9硬核处理器和Aritx-7 FPGA(PS+PL),本节我们先使用PL部分实现流水灯。首先我们要安装vivado 软件,

链接:https://pan.baidu.com/s/16IXGO5ckhFP_ov6kNAT3Jg

提取码:ed5m

这里我们就不费时间去讲解如何安装软件了,安装教程百度比比皆是,我们使用的软件版本是vivado2017.1版。

其次我们要知道如何创建ZYNQ工程,不步骤如下:

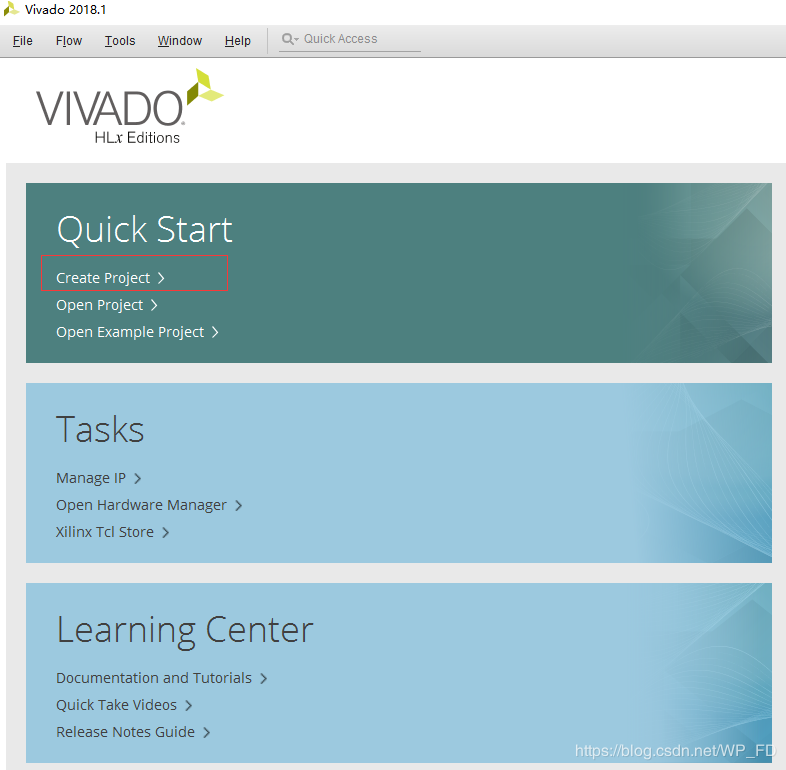

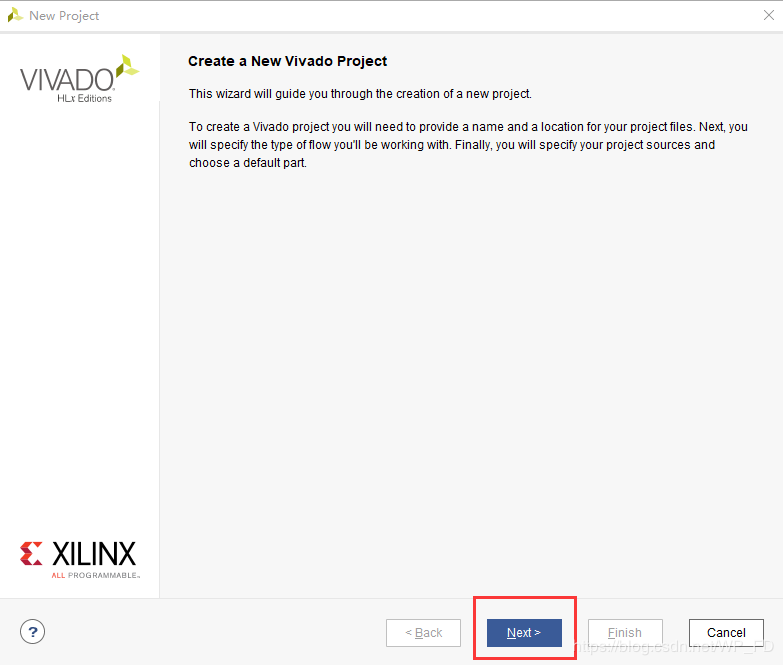

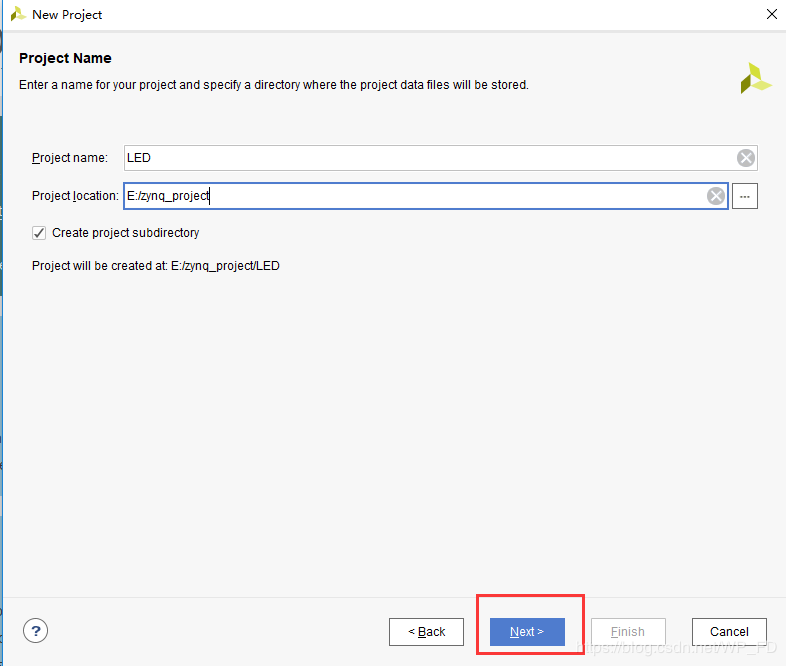

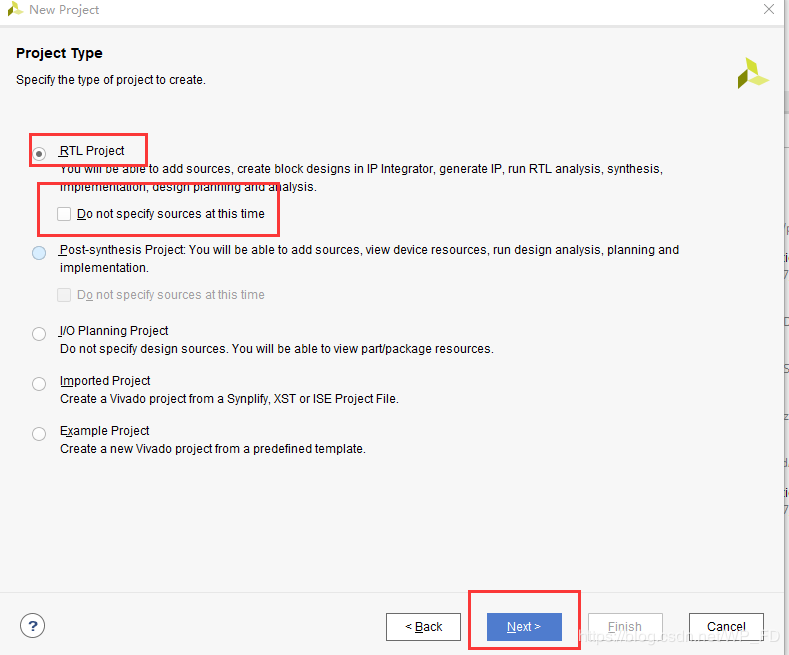

1、打开软件,创建新工程

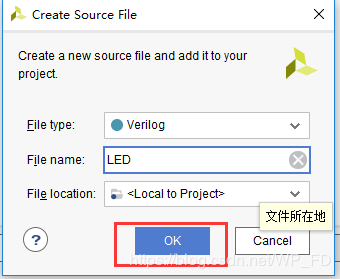

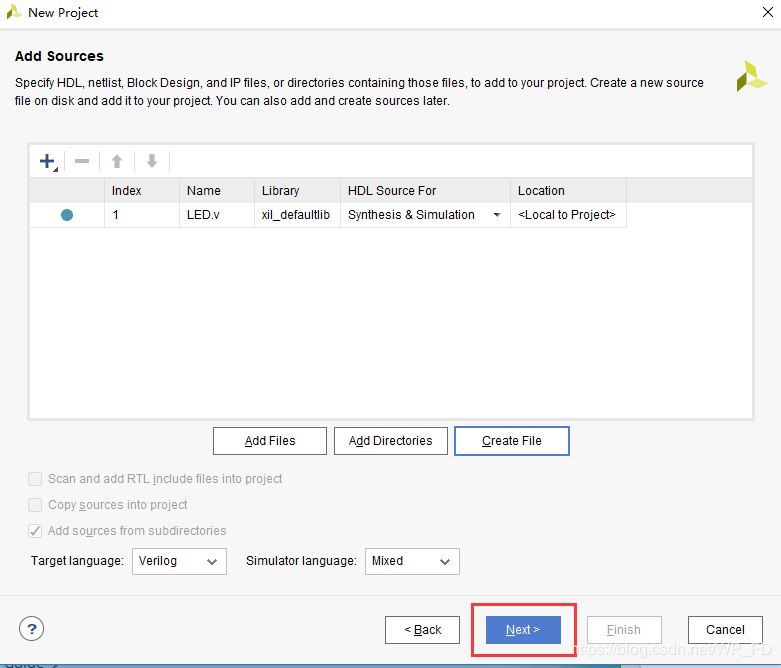

创造verilog文件:

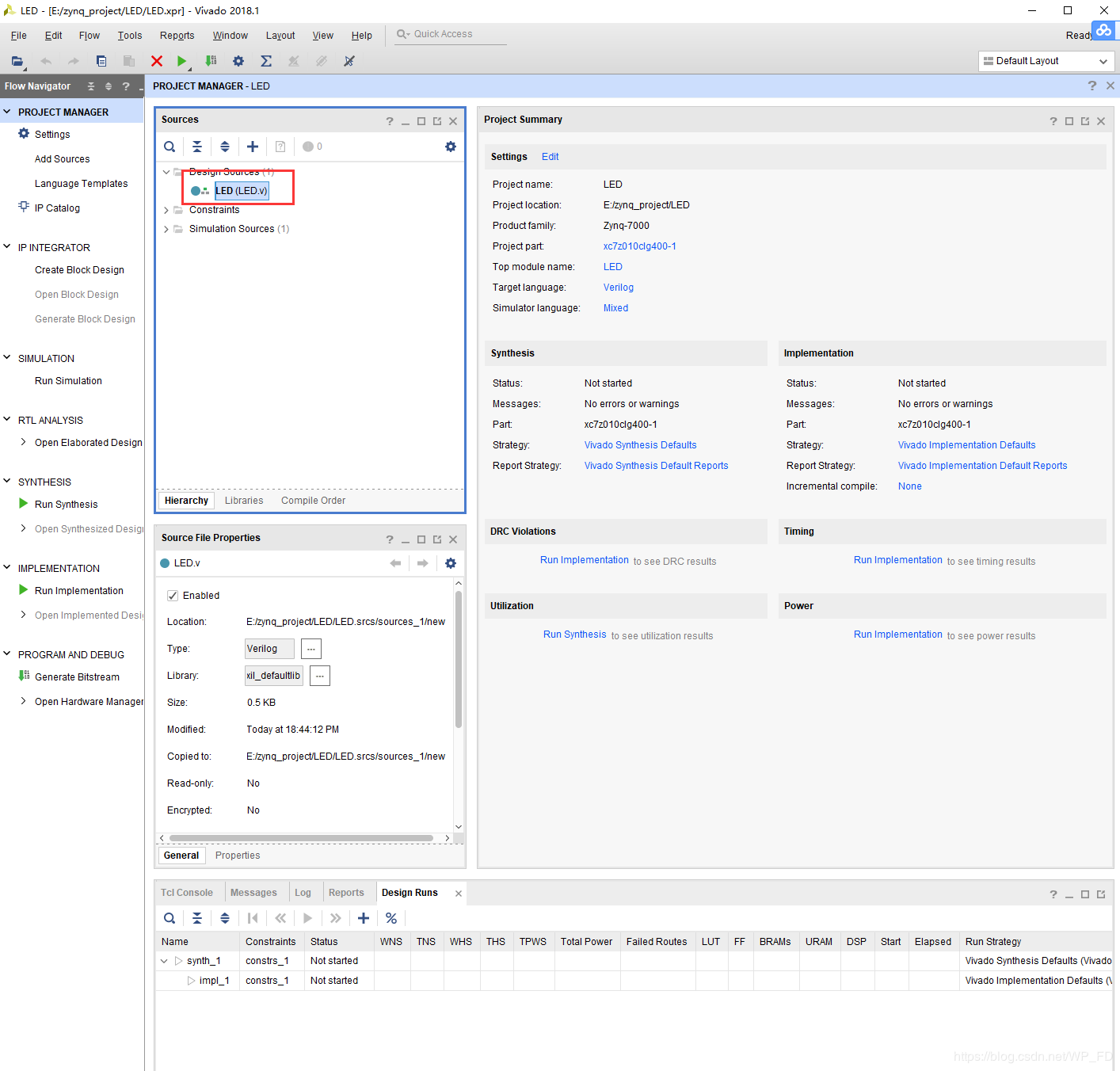

工程建立好以后界面如下所示:

2、编写流水灯verilog代码。

module LED(

//sys signal

sys_clk_50m,

reset_n,

//led

led

);

parameter LED_FREQUENCY = 49999999;

parameter UDLY = 1;

//sys signal

input sys_clk_50m;

input reset_n;

//led

output [3:0] led;

//sys signal

wire sys_clk_50m;

wire reset_n;

//led

reg [3:0] led;

reg [25:0] led_count;

always @(posedge sys_clk_50m or negedge reset_n)begin

if(!reset_n)begin

led <= 4'b0001;

led_count <= 26'd0;

end

else if(led_count == 26'd49_999_999)begin//1s count,50M

led_count <= #UDLY 26'd0;

led <= #UDLY {led[2:0],led[3]};

end

else begin

led_count <= #UDLY led_count + 26'd1;

end

end

endmodule3、时钟与引脚约束

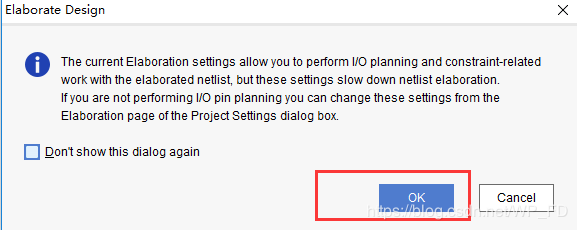

首先跑RTL

然后点击Layout->I/O Planning

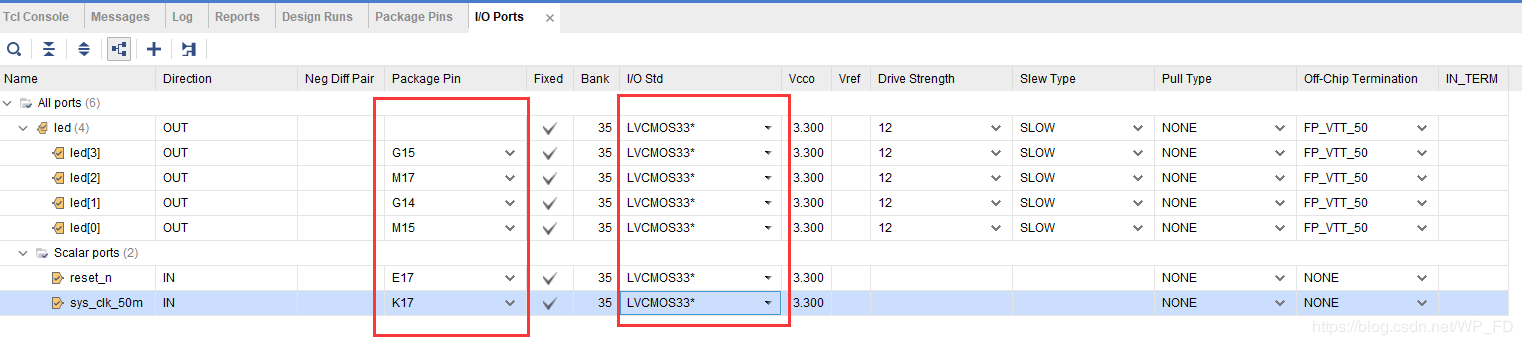

约束引脚:

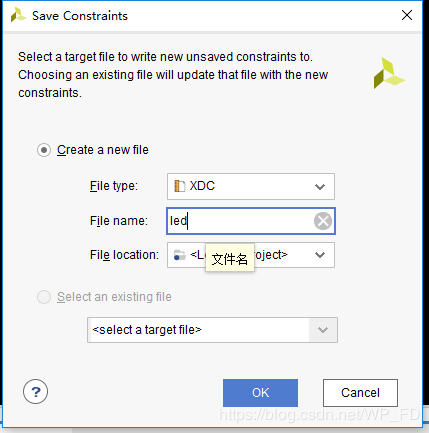

设置完成,保存设置,点击OK

点击Run Synthesis综合工程,可能需要一分钟时间:

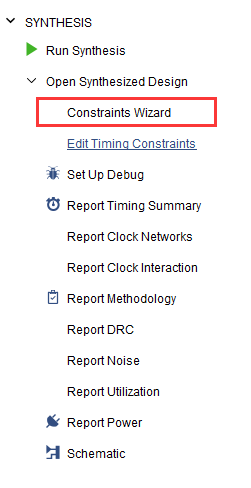

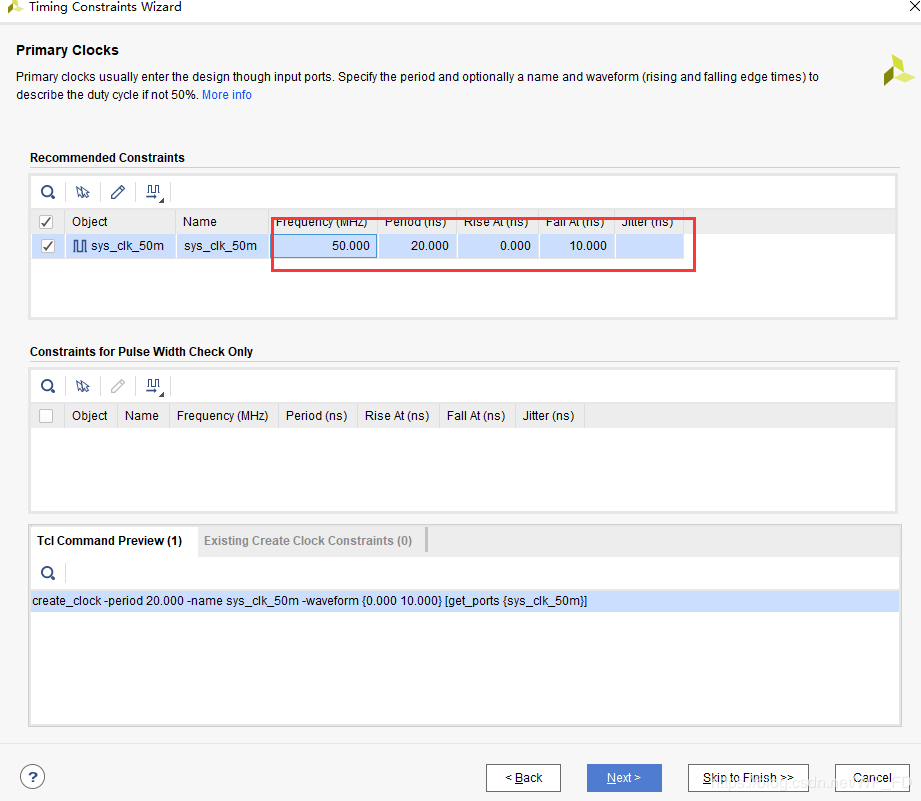

约束时钟,点击Constraints Wizard:

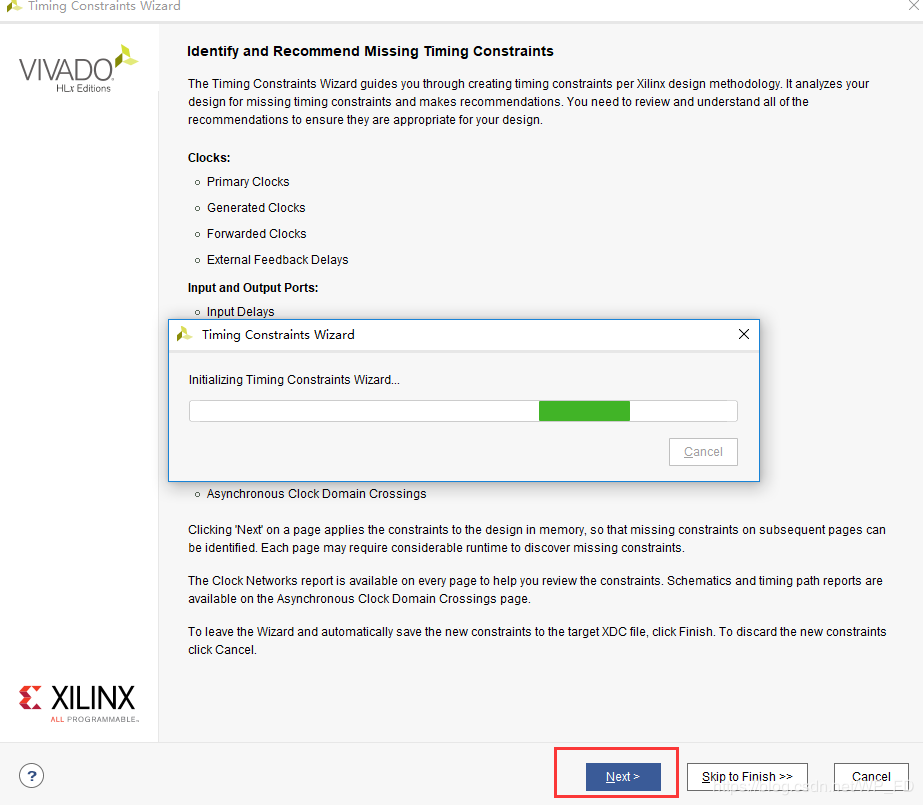

点击Next:

开发板时钟为50Mhz,点击Next,然后点击Skip to Finish完成时钟约束:

4、生成bit文件

点击Generate Bitstream生成bit文件

5、将程序下载到开发板中

将开发板上电,连接JTAG

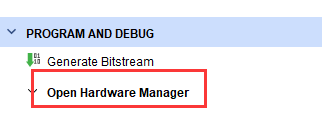

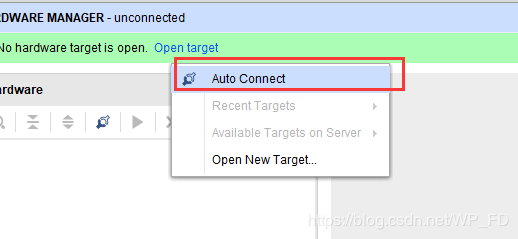

点击Open Hardware Manager连接硬件

显示如下画面表示连接上ZYNQ芯片

点击Program device下载bit文件到设备中

然后我们的流水灯就愉快的跑了起来!

版权声明:本文为CSDN博主「鹏哥DIY」的原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/WP_FD/article/details/82556954